Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

| Linha 3 008: | Linha 3 008: | ||

== ATIVIDADE EXTRA-CLASSE (AE) == | == ATIVIDADE EXTRA-CLASSE (AE) == | ||

| − | A soma das atividades Extra-classe será correspondente a | + | A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo. |

| − | + | <!-- | |

===AE1 - Palavras-cruzadas INTRODUÇÃO=== | ===AE1 - Palavras-cruzadas INTRODUÇÃO=== | ||

{{collapse top | bg=lightyellow | AE1 - Palavras-cruzadas INTRODUÇÃO}} | {{collapse top | bg=lightyellow | AE1 - Palavras-cruzadas INTRODUÇÃO}} | ||

Edição das 15h40min de 5 de abril de 2022

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 3 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||

|---|---|---|

|

|}

-->

- FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS.

A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a síntese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é:

[rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas.

O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [1].

- A FUNCTION: declaração, uso, mapeamento posicional x nominal, PURE x IMPURE.

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

end function;

- A PROCEDURE: declaração e uso

procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is

declarações

begin

afirmações sequenciais

end procedure;

- Exemplos de uso ASSERT, FUNCTION e PROCEDURE

- Exemplo: Cálculo do log2 de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural.

function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

- Exemplo: Declaração de FUNCTION em ARCHITECTURE Ex.9.1

- Aplicação no projeto do timer0_9

- Exemplo: Declaração em FUNCTION PACKAGE Ex. 9.2

-- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

library ieee;

use ieee.numeric_std.all;

use work.my_package.all;

entity organizer is

generic (size : natural := 3);

port

(

x : in UNSIGNED(2 to 5);

y : out UNSIGNED(size - 1 downto 0)

);

end entity;

architecture organizer of organizer is

begin

y <= order_and_fill(x, size);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335

library ieee;

use ieee.numeric_std.all;

package my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED;

end package;

package body my_package is

function order_and_fill (input : UNSIGNED; bits : natural) return UNSIGNED is

variable a : UNSIGNED(input'LENGTH - 1 downto 0);

variable result : UNSIGNED(bits - 1 downto 0);

begin

assert (input'LENGTH <= bits)

report "Improper input size!"

severity FAILURE;

if (input'LEFT > input'RIGHT) then

a := input;

else

for i in a'range loop

a(i) := input(input'LEFT + i);

end loop;

end if;

if (a'LENGTH < bits) then

result(bits - 1 downto a'LENGTH) := (others => '0');

result(a'LENGTH - 1 downto 0) := a;

else

result := a;

end if;

return result;

end function;

end package body;

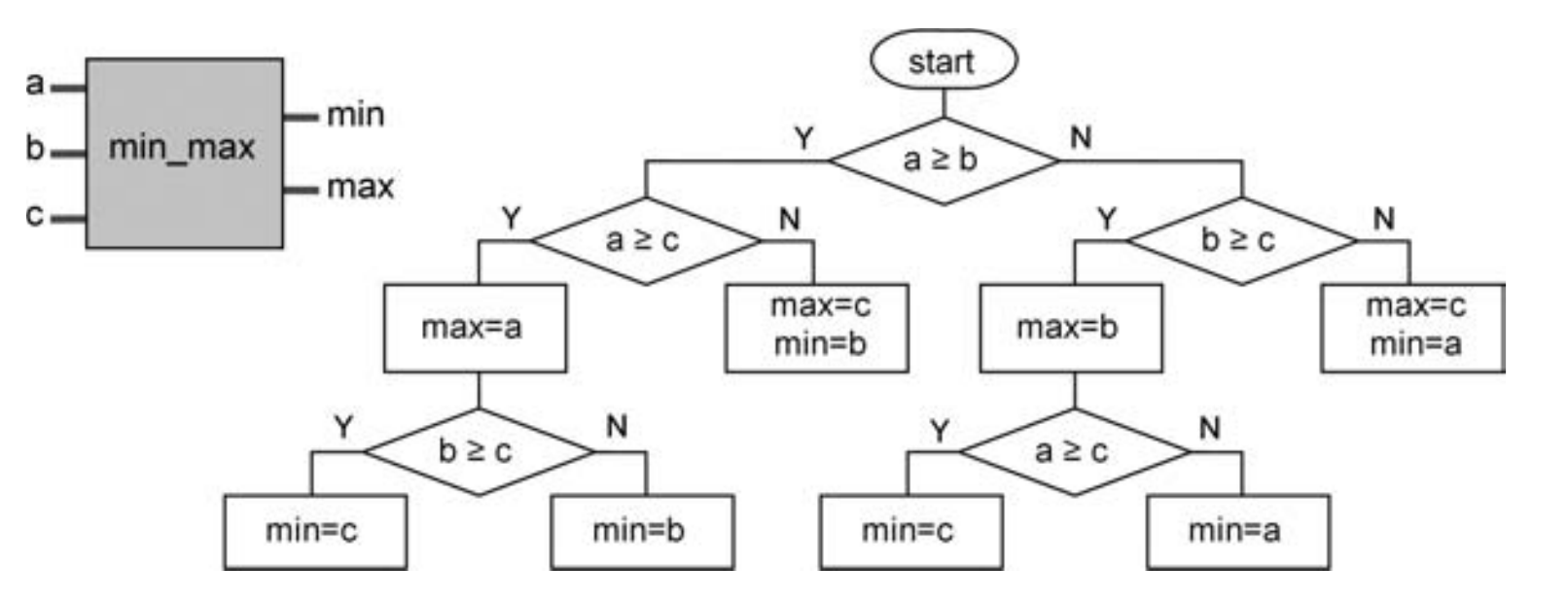

- Exemplo: min_max Ex.9.4

Figura 6.1 - Fluxograma da PROCEDURE min_max

-- FILE: comparator.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

use work.my_package.all;

entity comparator is

port

(

a, b, c : in integer range 0 to 255;

min, max : out integer range 0 to 255

);

end entity;

architecture comparator of comparator is

begin

min_max(a, b, c, min, max);

end architecture;

-- FILE: my_pkg.vhd

-- Fonte: PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2 ed. Massachusetts-EUA:MIT, 2010.

package my_package is

procedure min_max (

signal a, b, c : in integer;

signal min, max : out integer

);

end package;

package body my_package is

procedure min_max (

signal a, b, c : in integer range 0 to 255;

signal min, max : out integer range 0 to 255) is

begin

if (a >= b) then

if (a >= c) then

max <= a;

if (b >= c) then

min <= c;

else

min <= b;

end if;

else

max <= c;

min <= b;

end if;

else

if (b >= c) then

max <= b;

if (a >= c) then

min <= c;

else min <= a;

end if;

else

max <= c;

min <= a;

end if;

end if;

end procedure;

end package body;

- Exercícios: 9.1 a 9.4, 9.6 a 9.9

- Ver pag. 213 a 239 de [1])

- Aula 43 e 44 (12 mar) (presencial - Sábado 8h00 as 11h30)

- AE12 - Laboratório de programação de FPGA - Relógio Digital de 24 horas

|}

-->

- Aula 45 (15 mar)

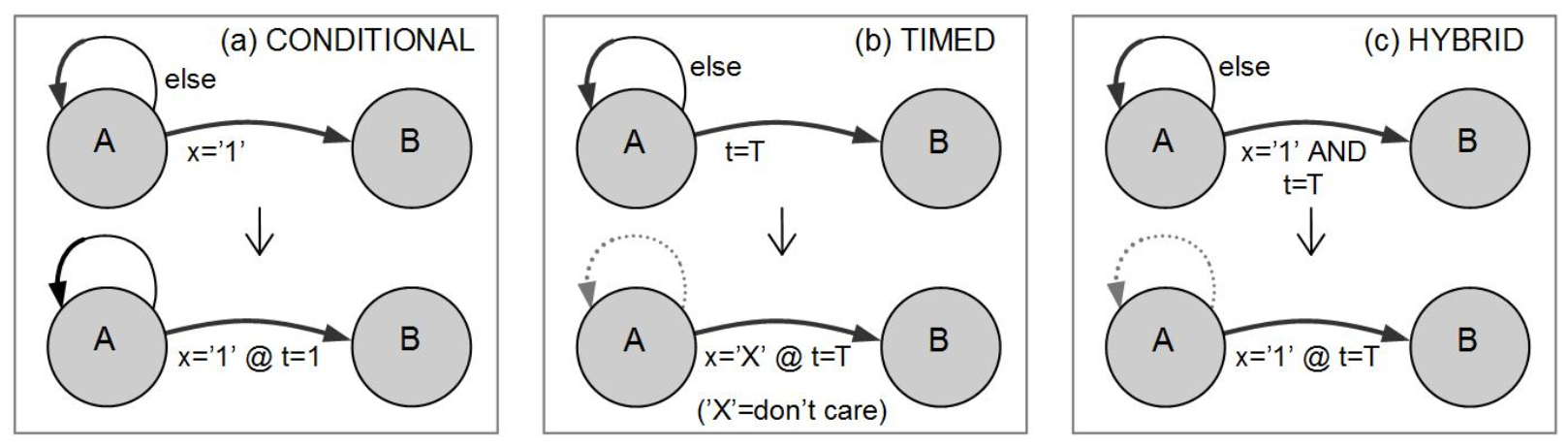

- Projeto de FSM temporizadas (nas quais as transições são ativadas também pelo tempo).

Figura 7.9 - Tipos de FSM (Condicional, Temporizada e Hibrida)

- Modelo de FSM temporizada

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END entity;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

signal timer: integer range 0 to MAX;

-- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

-- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

variable count: integer range o to MAX;

BEGIN

IF (rst = '1') THEN

pr_state <= A;

count := 0;

ELSIF (clk'EVENT AND clk = '1') THEN

count := count + 1;

if (count >= timer) then

pr_state <= nx_state;

count := 0;

end if;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

------Valores default das saidas------------

output <= < value >;

------Valores default do timer------------

timer <= <value>;

CASE pr_state IS

WHEN A =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ; -- apenas se diferente do valor default

IF (input =< value >) THEN

timer <= <value>; -- apenas se diferente do valor default

nx_state <= C;

...

ELSE

timer <= <value>; -- apenas se diferente do valor default

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END architecture;

- Ver pag. 298 a 301 de [1]

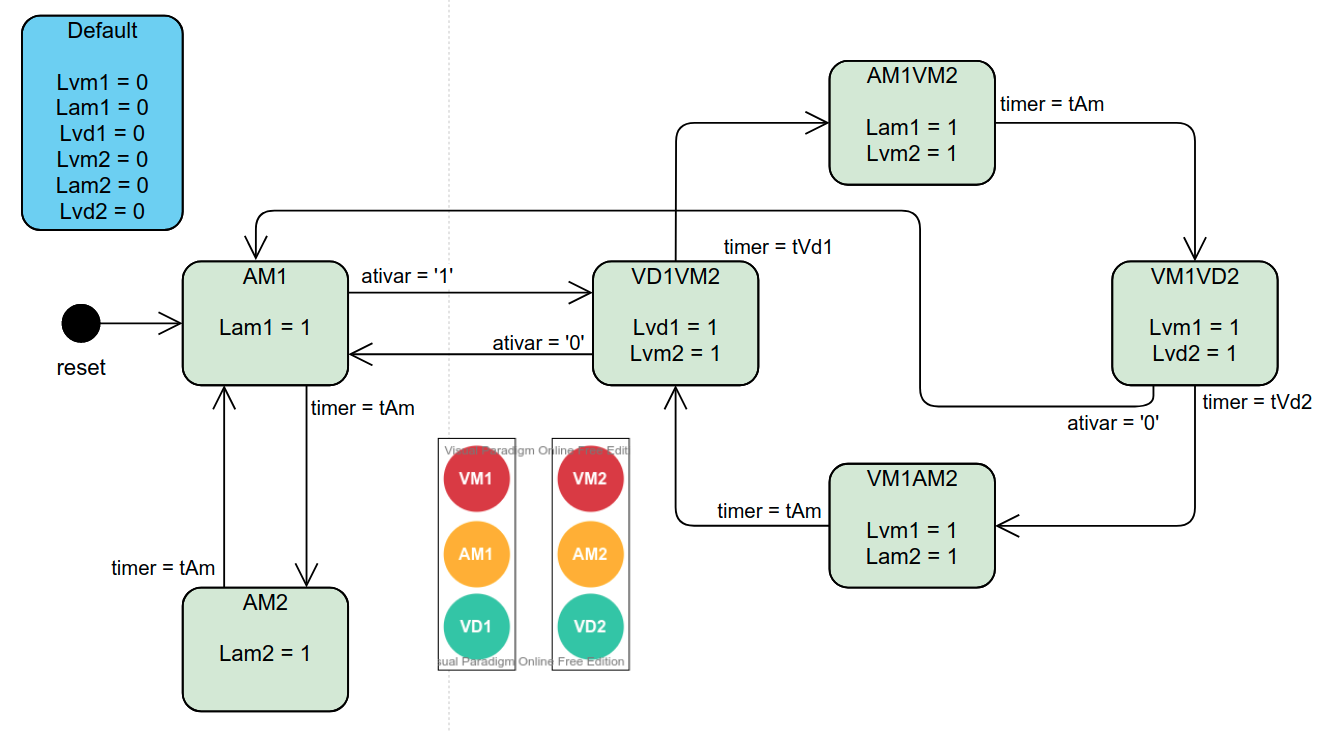

- Exemplo de FSM temporizada - semáforo temporizado

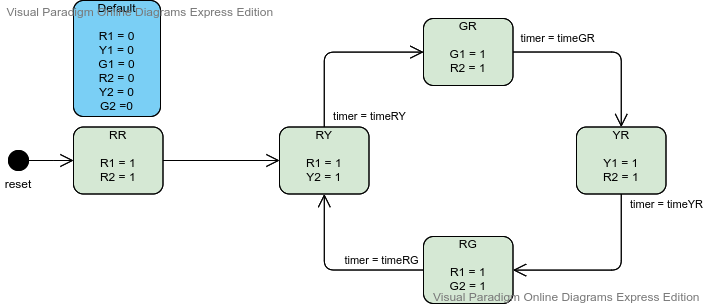

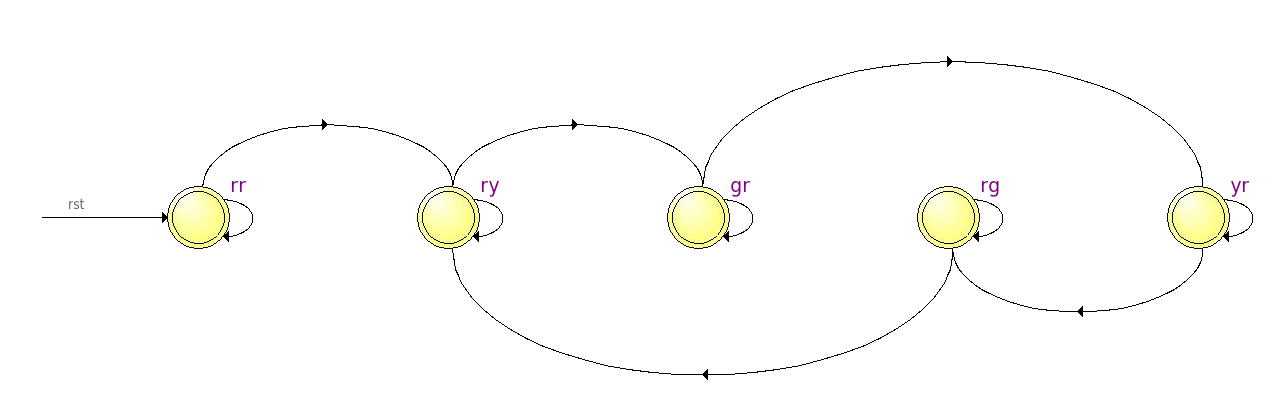

- Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular indicado pela FSM da figura abaixo:

Figura 7.10 - Diagrama de estados do controlador de semáforo

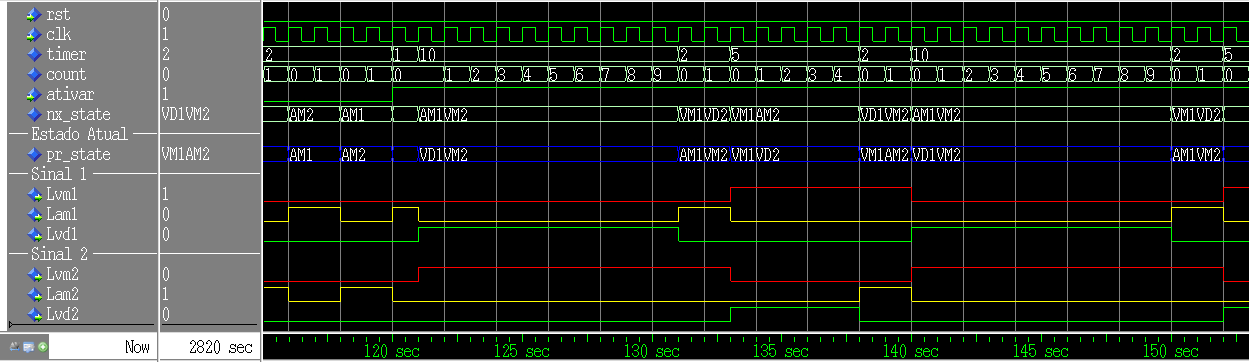

Figura 7.11 - Simulação do controlador de semáforo no Modelsim

| Exercício - Semaforo |

|---|

Figura 7.12 - Diagrama de estados do controlador de semáforo  Figura 7.13 - Diagrama de estados do Quartus do controlador de semáforo  |

-->

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.