De MediaWiki do Campus São José

Ir para navegação

Ir para pesquisar

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

| Unidade 1 - Introdução a disciplina

|

- Aula 1 (10 Mai)

- APRESENTAÇÃO DA DISCIPLINA

- Os materiais, prazos, documentação, histórico de trabalhos anteriores estão publicados nesta wiki.

- A PÁGINA DA DISCIPLINA contem os materiais que não alteram entre semestre.

- Nesta página está o REGISTRO DIÁRIO E AVALIAÇÕES.

- Para a realização e entrega das atividades será utilizada a PLATAFORMA MOODLE. Chave para auto inscrição (engtelecom_aluno)

- Durante a pandemia do COVID19 os encontros síncronos serão realizados através da plataforma Google Meet. Os encontros (havendo a concordância de todos) serão gravados, e ocorrerão nos horários normais das aulas. As aulas terão duração de 1h15 minutos com possibilidade de ainda acrescer 15 minutos previstos para esclarecimento de dúvidas. As gravações ficarão disponíveis por 30 dias no Drive do aluno, mas não poderão ser baixadas por limitação do sistema.

- Além dos horários de aula síncrona, serão agendados horários de ATENDIMENTO EXTRACLASSE para que os alunos possam tirar dúvidas da disciplina ou das ferramentas de ensino.

- Para a comunicação entre professor-aluno, além dos avisos do Sistema Acadêmimco (SIGAA), utilizaremos a plataforma SLACK. Sugere-se que os alunos também a utilizem para comunicação entre eles, principalmente nos trabalhos em equipe.

- Aula 2 (11 Mai)

- Introdução aos dispositivos lógicos programáveis:

-

- SPLD: PAL, PLA e GAL

- CPLDs

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

-

- Aula 3 (13 mai)

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Leituras complementares para a unidade

- Historia, processo de produção dos chips.

- Curiosidades do mundo digital

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

|

- Aula 4 (18 mai)

- Introdução ao VHDL e ambiente EDA - QUARTUS

- Estrutura do código VHDL

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Exemplo de descrição de um multiplexador de 4 entradas

entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

- Faça a análise e sintese do mux_novo, associando a architecture v_logica_pura, depois v_WITH_SELECT, depois v_WHEN e por último v_IF_ELSE.

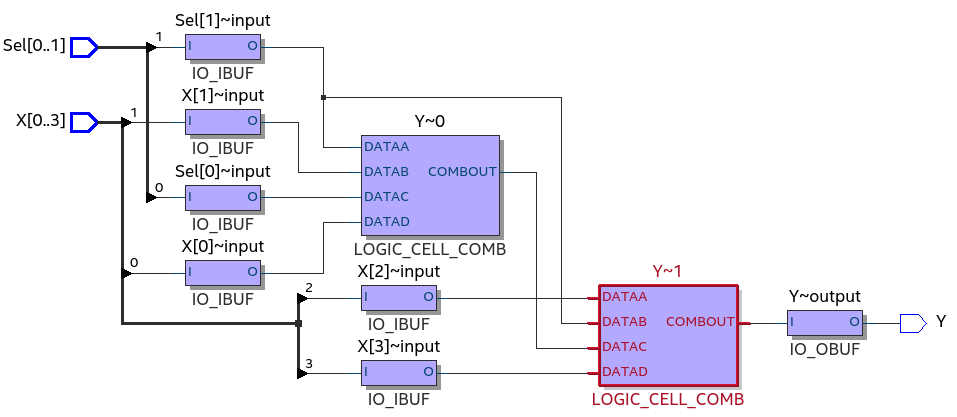

- Note a diferença entre os RTL Viewer obtidos para cada architecture.

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.2 - Código RTL do mux 4x1 v_WHEN

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- OBS: Register Transfer-Level (RTL) é uma abstração na qual o circuito é descrito em termos de fluxo de sinais entre os registradores presentes no hardware e as operações combinacionais realizadas com esses dados.

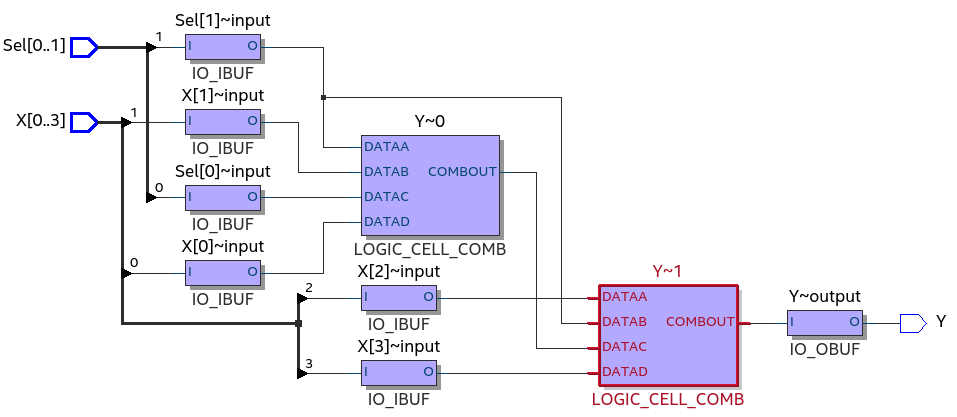

- Note a que ao verificar o Technology Map Viewer, nos 3 primeiros casos serão usados os mesmos elementos lógicos.

Figura 2.4 - Technology Map do mux 4x1

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Note que o elemento lógico é representado por uma Tabela Verdade, Mapa de Karnaugh ou Circuito Lógico Clicando com o botão Direito do Mouse e selecionando Properties. Todas as representações são equivalentes. Na prática a LUT do elemento lógico se comporta como uma tabela de consulta (Tabela Verdade).

- Aula 5 (20 mai)

- Exemplo 2.2 (VHDL) - programação de um flip-flop

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

Figura 2.3 - Technology Map do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

Figura 2.4 - Chip Planner do Exemplo 2.2

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops

Figura 2.5 - RTL 4 FF

Fonte: Elaborado pelo autor.

Fonte: Elaborado pelo autor.

- Aula 6 (24 mai)

- Uso de alguns sites auxiliares para a programação em VHDL:

- Exemplo de um contador em VHDL. COUNTER na página de VHDL da Wikipedia.

- Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal.

- Uso das bibliotecas no VHDL.

-

- O Package standard: é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift.

- O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação.

- Como declarar e usar os pacotes da biblioteca std.

- Note que esses pacotes são implicitamente carregados não precisando ser declarados. Ambos pacotes foram expandidos no VHDL 2008.

-- NAO É NECESSARIO DECLARAR

library std;

use std.standard.all;

use std.textio.all;

- Onde estão os arquivos dessa biblioteca na versão Quartus II instalada nos computadores do IFSC e na IFSC_CLOUD?

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

-

- O Package std_logic_1164 define os tipos de dados STD_ULOGIC e STD_LOGIC.

- O Package numeric_std define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo STD_LOGIC como base.

- O Package numeric_bit define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo BIT como base.

- O Package numeric_std_unsigned introduz operadores sobre o tipo STD_LOGIC_VECTOR, considerando os como números sem sinal.

- O Package numeric_bit_unsigned introduz operadores sobre o tipo BIT_VECTOR, considerando os como números sem sinal.

- O Package fixed_pkg (e pacotes associados) definem os tipos de ponto fixo unsigned (UFIXED) e signed (SFIXED) e seus operadores.

- O Package float_pkg (e pacotes associados) definem o tipo de ponto flutuante (FLOAT) e seus operadores.

- Pacotes não padronizados (NÃO UTILIZAR)

- O Package std_logic_arith define os tipos de dados SIGNED e UNSIGNED e seus operadores. Deve ser sempre substituído por pelo pacote padrão equivalente numeric_std. (disponível da Mentor e Synopsys)

- O Package std_logic_unsigned é semelhante ao numeric_std_unsigned. (disponível da Synopsys)

- O Package std_logic_signed é semelhante ao acima operando sobre números com sinal. (disponível da Synopsys)

- Como declarar e usar os pacotes da biblioteca ieee.

library ieee;

-- UTILIZAR ESTES PACOTES

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

-- NAO UTILIZAR ESTES PACOTES

use ieee.std_logic_arith.all;

use ieee.std_logic_signed.all;

use ieee.std_logic_unsigned.all;

- Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD?

- Os pacotes padrão:

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

- Os pacotes não padrão:

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics)

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

- Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD?

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

|

Avaliações

Nas avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues:

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

- ↑ 1,0 1,1 1,2 1,3 1,4 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335