Mudanças entre as edições de "DLP1-EngTel (página)"

| Linha 161: | Linha 161: | ||

::* Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4), Leading Zeros (LOOP com EXIT) (Ex 6.5) | ::* Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4), Leading Zeros (LOOP com EXIT) (Ex 6.5) | ||

:*Instrução '''CASE''' | :*Instrução '''CASE''' | ||

| − | ::* | + | ::* Exemplo: Contador de 0 a 9 segundos com saída SSD (Ex 6.6) |

| + | ::* Exemplo: Projeto ruim com CASE incompleto (Ex. 6.7) | ||

| − | :*Ver pag. 161 a | + | :*Ver pag. 161 a 171 de <ref name="PEDRONI2010b"/> |

==Recursos de Laboratório== | ==Recursos de Laboratório== | ||

Edição das 12h15min de 27 de março de 2015

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Informações Gerais

Registro on-line das aulas

Unidade 1

- Aula 1 (5 fev)

- Dispositivos lógicos programáveis.

- Bases da linguagem VHDL.

- Tipos de dados, libraries, conversão de tipos, operadores, atributos.

- Código VHDL concorrente e sequencial.

- Projeto hierárquico.

- Simulação e Testbench

- Maquina de estado finita (FSM).

- Projeto Final de circuitos lógicos.

- Avaliações.

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- Ver pag. 413 a 418 de [1]

- Aula 2 (6 fev)

- Introdução aos dispositivos lógicos programáveis:

- CPLDs e FPGAs

- Fabricantes de DLPs

- Vizualização no Chip Planner de um projeto.

- Ver pag. 419 a 424 de [1]

- Aula 3 (11 fev)

- Introdução aos dispositivos lógicos programáveis:

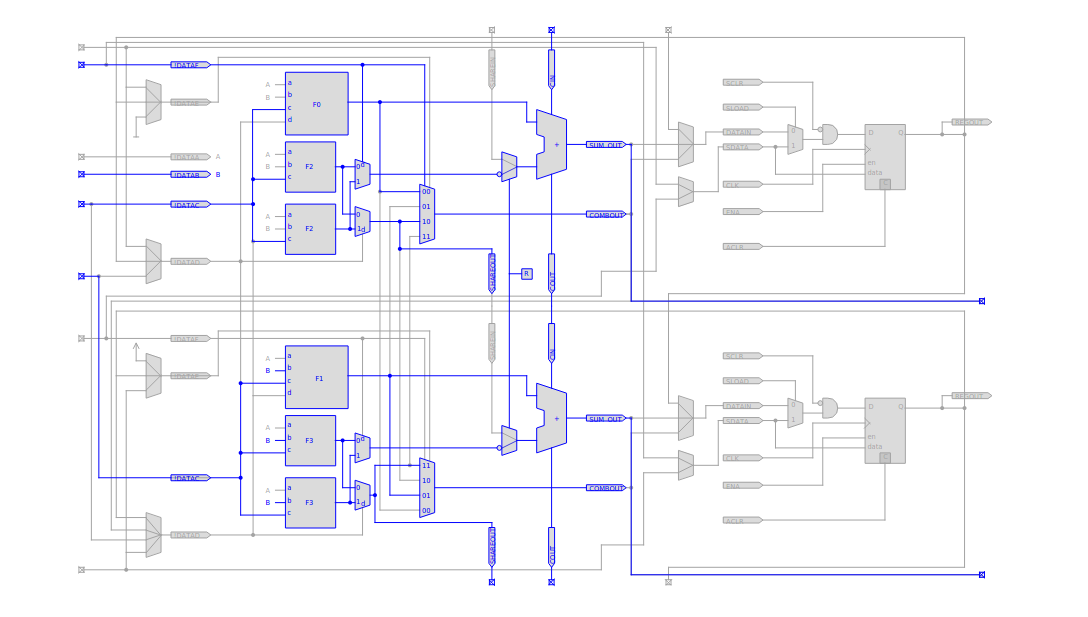

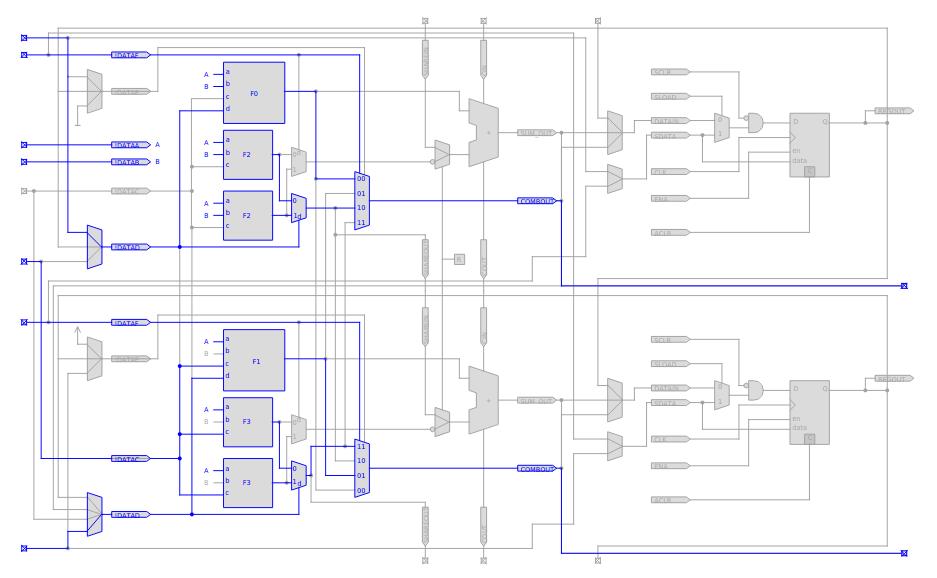

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Vizualização no Chip Planner de um projeto.

- Ver pag. 424 a 431 de [1]

Unidade 2

- Aula 4 (12 fev)

- Introdução ao VHDL.

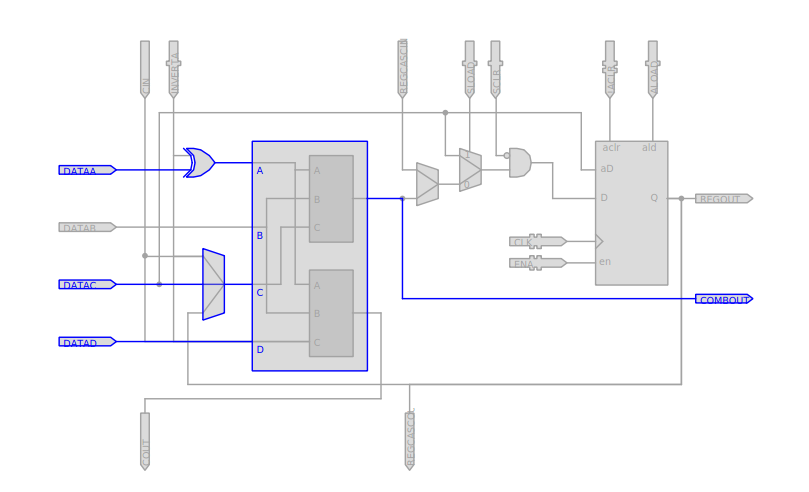

- Exemplo de programação de um full adder. Utilize os arquivos .qar enviados (V1 - estrutural. V2 - comportamental) para analisar os circuitos obtidos e realizar as simulações funcional e temporal.

- Ver pag. 3 a 8 de [2]

- Aula 5 (13 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Libraries, Entity, Architecture

- Aula 6 (19 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Exercicios 2.2 (VHDL e QSIM)

- Exemplo de programação de um flip-flop

- Exercicios 2.3 (VHDL e QSIM)

- Ver pag. 3 a 8 de [2]

- Aula 7 (20 fev)

- Introdução ao VHDL.

- Libraries, Entity, Architechture, Generic.

- Ver pag. 11 a 18 de [2]

- Aula 8 (25 fev)

- Introdução ao VHDL.

- Exemplo de um circuito somador

- Exemplo de FF-D

- Ver pag. 19 a 21 de [2]

Unidade 3

- Aula 9 (26 fev)

- Tipos de Dados em VHDL.

- Exemplo de um circuito somador com registrador

- Exemplo de decodificador de endereço genérico

- Ver pag. 22 a 27 de [2]

- Aula 10 (27 fev)

- Tipos de Dados em VHDL.

- Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE.

- Palavra chave OTHERS

- Bibliotecas padrão.

- Não use as bibliotecas não padrão (std_logic_arith, std_logic_unsigned, std_logic_signed)

- Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR, (UN)SIGNED

- Classificação dos tipos de dados.

- Exemplo 3.1 Buffer Tri-state

- Exemplo 3.3 Multiplicador

- Ver pag. 31 a 54 de [2]

- Aula 11 (5 mar)

- Tipos de Dados em VHDL.

- Tipos Array definidos pelo usuário: 1D, 1D x 1D, 2D, 1D x 1D x 1D, 3D.

- Ver pag. 62 a 79 de [2]

- Aula 12 (6 mar)

- Operadores em VHDL.

- Operadores predefinidos: Atribuição, Logicos, Arithméticos, Comparação, Deslocamento, Concatenação, "Matching".

- Sobrecarga de operadores

- Ver pag. 91 a 98 de [2]

- Aula 13 (11 mar)

- Atributos em VHDL.

- Atributos predefinidos: tipo escalar e enumerados; tipo array; de sinal;

- Exemplo 4.1 (Simulação funcional)

- Atributos definidos pelo usuário;

- Atributos de síntese: Enum_encoding, chip_pin, keep.

- Exemplo: Delay line (Síntese e Simulação temporal sem o com o atributo keep)

- Ver pag. 99 a 109 de [2]

- Aula 14 (12 mar)

- Atributos em VHDL.

- Atributos de síntese: preserve, noprune.

- Exemplo: Redundant Register

- Group e Alias

- Exercício 4.17: Discussão de possibilidades de implementação

- Ver pag. 109 a 119 de [2]

Unidade 4

- Aula 15 (13 mar)

- Código Concorrente.

- WHEN, SELECT, GENERATE;

- Exemplo 5.1 + 5.2 mux: com 4 tipos de arquiteturas (com operadores, com WHEN, com SELECT, com IF),

- Uso de CONFIGURATION para selecionar um entre várias arquiteturas.

CONFIGURATION which_mux OF mux IS

FOR with_OPERATOR END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

-- FOR with_IF END FOR;

END CONFIGURATION;

- Exemplo 5.3 ALU: modificação do opcodes: "0011" -> a NAND b, "0100" -> "a OR b, "1111" => a * b. É necessário mudar a ENTITY, dobrando o número de bits da saída devido a multiplicação, e adaptar o código para a nova quantidade de bits.

- Ver pag. 121 a 129 de [2]

- Aula 16 (19 mar)

- Código Concorrente.

- Aula 17 (20 mar)

- Código Concorrente.

- Aula 18 (25 mar)

- Código Concorrente.

Unidade 5

- Aula 19 (26 mar)

- Código Sequencial.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

- Instrução IF

- Exemplos: DFFs with Reset and Clear (Variação Ex 6.1), Basic Counter (Ex. 6.2), Shift Register (Ex. 6.3)

- Instrução WAIT: WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II).

- Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT.

- Ver pag. 161 a 160 de [2]

- Aula 20 (27 mar)

- Código Sequencial.

- Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

- Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4), Leading Zeros (LOOP com EXIT) (Ex 6.5)

- Instrução CASE

- Exemplo: Contador de 0 a 9 segundos com saída SSD (Ex 6.6)

- Exemplo: Projeto ruim com CASE incompleto (Ex. 6.7)

- Ver pag. 161 a 171 de [2]

Recursos de Laboratório

Quartus/Modelsim/QSIM

Nos laboratórios do IFSC, os softwares Quartus/Modelsim/QSIM estão disponíveis diretamente na plataforma LINUX. Utilize preferencialmente a versão 13.0sp1 (32 bits), pois ela tem suporte para os FPGAs mais antigos como a familia Cyclone I.

Para uso fora do IFSC dos recursos computacionais com licença educacional, o IFSC disponibiliza para seus alunos o IFSC-CLOUD. Atualmente a forma mais eficiente de acesso é através do Cliente X2GO. O procedimento de instalação/ configuração e uso do Quartus/Modelsim/QSIM está descrito em Acesso ao IFSC-CLOUD#Cliente X2GO (recomendado).

Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a plataforma Sharelatex do IFSC-CLOUD. Utilize preferencialmente o modelo de artigo no padrão ABNT.

Atividades extra

JÁ ENCERRADAS

| AE1 - Estudo do tipo de programação dos FPGA (prazo 20/02/2015) |

|---|

|

| AE2 - Estudo do Quartus II e Dispositivos FPGA (prazo 27/02/2015) |

|---|

|

| AE3 - Uso de operadores e tipos de dados (Prazo de entrega 23/03/2015) |

|---|

entity bin2bcd is

port (

num_bin : in std_logic_vector(9 downto 0);

C_bcd : out std_logic_vector(3 downto 0);

D_bcd : out std_logic_vector(3 downto 0);

U_bcd : out std_logic_vector(3 downto 0));

end entity;

|

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

| Estrutura do VHDL |

|---|

|

| Estudo dos atributos em VDHL |

|---|

entity atributte_test_array is

port(

x1, x2, x3, x4, x5, x6: out integer range 0 to 15;

x7, x8: out boolean;

m12, m44, m47: out bit);

end entity;

architecture ifsc of atributte_test_array is

TYPE matrix IS ARRAY (1 TO 4, 7 DOWNTO 0) OF BIT;

SIGNAL test: matrix := (('0', '1', '1', '0', '0', '1', '1', '0'), "01110100", ('1', others => '0'), (4 => '0', others => '1'));

begin

--------------------------------------------------------------------------

x1 <= matrix'LEFT(1); --result=1 (type of x1 must be INTEGER or eq.)

x2 <= matrix'LEFT(2); --result=7 (type of x2 must be INTEGER or eq.)

x3 <= matrix'RIGHT(1); --result=4 (type of x3 must be INTEGER or eq.)

x4 <= matrix'RIGHT(2); --result=0 (type of x4 must be INTEGER or eq.)

x5 <= matrix'LENGTH(1); --result=4 (type of x5 must be INTEGER or eq.)

x6 <= matrix'LENGTH(2); --result=8 (type of x6 must be INTEGER or eq.)

x7 <= matrix'ASCENDING(1); --result=TRUE (type of x7 must be BOOLEAN)

x8 <= matrix'ASCENDING(2); --result=FALSE (type of x8 must be BOOLEAN)

m12 <= test(1,2); -- result = '1' - Acess the element of 'test' row(1), columm(2) (type of m11 must be bit)

m47 <= test(4,7); -- result = '1' - Acess the element of 'test' row(7), columm(7) (type of m11 must be bit)

m44 <= test(4,4); -- result = '0' - Acess the element of 'test' row(4), columm(4) (type of m11 must be bit)

--------------------------------------------------------------------------

end architecture;

|

| Resolução dos exercícios do Cap 3 |

|---|

|

| Resolução dos exercícios do Cap 4 |

|---|

|

| Resolução dos exercícios do Cap 5 |

|---|

|

| Projetar Conversor de binário para 7 segmentos |

|---|

|

Projetar em VHDL dois conversores de binário para 7 segmentos a) usando código concorrente (SELECT) e b) usando código sequencial (CASE).

ENTITY ssd IS

PORT (

bin: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

ssd: OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END ENTITY;

|

PARA ENTREGAR

| AE4 - Uso de código concorrente - ALU multiplicadora (Prazo de entrega 01/04/2015) | ||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

a, b: IN STD_LOGIC_VECTOR(N-1 DOWNTO 0);

opcode: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

valid: out STD_LOGIC;

y: OUT STD_LOGIC_VECTOR(2*N-1 DOWNTO 0));

END ENTITY;

|

Links auxiliares

Livros/Resumos sobre VHDL

- VHDL Handbook - Hardi (apenas VHDL’87 e VHDL’93)

- VHDL QUICK REFERENCE CARD - Qualis (r2.1)

- VHDL 1164 PACKAGES QUICK REFERENCE CARD - Qualis (r2.2)

- Listagem dos packages

- Palavras reservadas

- Atributos predefinidos

Fabricantes de DLPs

Padrões IEEE para o VDHL

Os padrões IEEE [1]estão disponíveis para consulta se você estiver na rede do IFSC. Para a linguagem VHDL consulte os padrões: 1164,1076

- IEEE Standard Multivalue Logic System for VHDL Model Interoperability (Std_logic_1164)

- IEEE Std 1076.1: Behavioural languages – Part 1-1: VHDL language reference manual REDLINE

- IEEE Std 1076.1: Behavioural languages – Part 6: VHDL Analog and Mixed-Signal Extensions

- IEEE Std 1076.1.1™-2011 - IEEE Standard for VHDL Analog and Mixed-Signal Extensions—Packages for Multiple Energy Domain Support, REDLINE

- IEEE Standard for VHDL Register Transfer Level (RTL) Synthesis

- IEEE Standard VHDL Analog and Mixed-Signal Extensions

- IEEE Standard VHDL Synthesis Packages

- IEEE Std 1076-2002: IEEE Standard VHDL Language Reference Manual

- IEEE Std 1076.2-1996: IEEE Standard VHDL Mathematical Packages

Referências Bibliográficas:

- ↑ 1,0 1,1 1,2 PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335