Mudanças entre as edições de "Circuito Somador Carry Ripple - Pedroni"

Ir para navegação

Ir para pesquisar

(Criou página com '__NOTOC__ ==Estrutura== * ==Código VHDL== <syntaxhighlight lang=vhdl> --Book: Pedroni/488 --8 bits library ieee; use ieee.std_logic_1164.all; entity carry_ripple_adder is generic (n: integer ...') |

|||

| (19 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

__NOTOC__ | __NOTOC__ | ||

==Estrutura== | ==Estrutura== | ||

| − | * | + | *Unidades de somadores completos (FAs) conectadas em série através do carry out. |

| − | == | + | *Possui um processo sensível as entradas a, b e carry in. Incrementa as funções de propagação da saída e do carry out através de um for loop. |

| + | |||

| + | ==VHDL== | ||

| + | {{Collapse top | Código}} | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

--Book: Pedroni/488 | --Book: Pedroni/488 | ||

| Linha 24: | Linha 27: | ||

variable carry: std_logic_vector (n downto 0); | variable carry: std_logic_vector (n downto 0); | ||

begin | begin | ||

| + | carry(0) := cin; | ||

| + | |||

for i in 0 to n-1 loop | for i in 0 to n-1 loop | ||

s(i) <= a(i) xor b(i) xor carry(i); | s(i) <= a(i) xor b(i) xor carry(i); | ||

| Linha 32: | Linha 37: | ||

end architecture; | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | {{Collapse bottom}} | ||

| + | ==Testbench== | ||

| + | {{Collapse top | Código}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --rising_edge( clock ) then | ||

| + | -- Testbench created online at: | ||

| + | -- www.doulos.com/knowhow/perl/testbench_creation/ | ||

| + | -- Copyright Doulos Ltd | ||

| + | -- SD, 03 November 2002 | ||

| + | library IEEE; | ||

| + | use IEEE.Std_logic_1164.all; | ||

| + | use IEEE.Numeric_Std.all; | ||

| + | |||

| + | entity carry_ripple_adder_tb is | ||

| + | generic (Nbits: integer := 4); | ||

| + | end; | ||

| + | architecture bench of carry_ripple_adder_tb is | ||

| + | component carry_ripple_adder is | ||

| + | generic (n: integer := 4); | ||

| + | port (a,b : in std_logic_vector (n-1 downto 0); | ||

| + | cin: in std_logic; | ||

| + | s: out std_logic_vector (n-1 downto 0); | ||

| + | cout: out std_logic); | ||

| + | end component; | ||

| + | signal a: std_logic_vector (Nbits-1 downto 0); | ||

| + | signal b: std_logic_vector (Nbits-1 downto 0); | ||

| + | signal cin: std_logic; | ||

| + | signal s: std_logic_vector (Nbits-1 downto 0); | ||

| + | signal cout: std_logic; | ||

| + | begin | ||

| + | -- Insert values for generic parameters !! | ||

| + | uut: carry_ripple_adder generic map (n => Nbits) | ||

| + | port map ( a => a, | ||

| + | b => b, | ||

| + | cin => cin, | ||

| + | s => s, | ||

| + | cout => cout); | ||

| + | stimulus: process | ||

| + | begin | ||

| + | a <= "0100"; | ||

| + | b <= "0101"; | ||

| + | cin <= '0'; | ||

| + | wait for 100 ns ; | ||

| + | cin <= '1'; | ||

| + | wait for 100 ns ; | ||

| + | end process; | ||

| + | |||

| + | end; | ||

| + | </syntaxhighlight> | ||

| + | {{Collapse bottom}} | ||

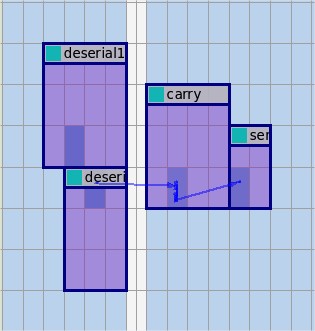

| − | + | *Logic Block: | |

| − | * | + | [[Arquivo: carry_ripple_chip.png | 200px]] |

| − | |||

==Simulações== | ==Simulações== | ||

| Linha 41: | Linha 95: | ||

! colspan="1" style="background: #efefef;" | Nº Bits | ! colspan="1" style="background: #efefef;" | Nº Bits | ||

! colspan="1" style="background: #efefef;" | ALMs | ! colspan="1" style="background: #efefef;" | ALMs | ||

| − | ! colspan="1" style="background: #efefef;" | | + | ! colspan="1" style="background: #efefef;" | Potência (mW) |

| − | ! colspan="1" style="background: #efefef;" | | + | ! colspan="1" style="background: #efefef;" | Report Path |

| − | | | + | ! colspan="1" style="background: #efefef;" | Report Timing |

| − | | | + | ! colspan="1" style="background: #efefef;" | Caminho crítico |

| + | ! colspan="1" style="background: #efefef;" | Logic Block | ||

| + | ! colspan="1" style="background: #efefef;" | Optimization | ||

| + | ! colspan="1" style="background: #efefef;" | Seed | ||

|- | |- | ||

| − | | | + | | 4 || 40 || 142.58 || 4.021 || 4.253 || deserial0-dout[0]-internal[3] || S || Balanced || 1 |

|- | |- | ||

| − | | | + | | 32 || 287 || 184.61 || 18.954 || 19.186 || deserial1-dout[0]-internal[31] || S || Balanced || 1 |

|- | |- | ||

| − | | | + | | 128 || 1.041 || 307.58 || 64.238 || 64.791 (VIOLATED) || deserial0-dout[0]-internal[127]|| Auto || Balanced || 1 |

|- | |- | ||

|} | |} | ||

| + | |||

| + | |||

| + | <math> \uparrow </math> | ||

Edição atual tal como às 14h36min de 12 de abril de 2016

Estrutura

- Unidades de somadores completos (FAs) conectadas em série através do carry out.

- Possui um processo sensível as entradas a, b e carry in. Incrementa as funções de propagação da saída e do carry out através de um for loop.

VHDL

| Código |

|---|

--Book: Pedroni/488

--8 bits

library ieee;

use ieee.std_logic_1164.all;

entity carry_ripple_adder is

generic (n: integer := 8); --number of bits

port (a,b : in std_logic_vector (n-1 downto 0);

cin: in std_logic;

s: out std_logic_vector (n-1 downto 0);

cout: out std_logic);

end carry_ripple_adder;

architecture structure of carry_ripple_adder is

begin

process (a,b,cin)

variable carry: std_logic_vector (n downto 0);

begin

carry(0) := cin;

for i in 0 to n-1 loop

s(i) <= a(i) xor b(i) xor carry(i);

carry(i+1) := (a(i) and b(i)) or (a(i) and carry(i)) or (b(i) and carry(i));

end loop;

cout <= carry(n);

end process;

end architecture;

|

Testbench

| Código |

|---|

--rising_edge( clock ) then

-- Testbench created online at:

-- www.doulos.com/knowhow/perl/testbench_creation/

-- Copyright Doulos Ltd

-- SD, 03 November 2002

library IEEE;

use IEEE.Std_logic_1164.all;

use IEEE.Numeric_Std.all;

entity carry_ripple_adder_tb is

generic (Nbits: integer := 4);

end;

architecture bench of carry_ripple_adder_tb is

component carry_ripple_adder is

generic (n: integer := 4);

port (a,b : in std_logic_vector (n-1 downto 0);

cin: in std_logic;

s: out std_logic_vector (n-1 downto 0);

cout: out std_logic);

end component;

signal a: std_logic_vector (Nbits-1 downto 0);

signal b: std_logic_vector (Nbits-1 downto 0);

signal cin: std_logic;

signal s: std_logic_vector (Nbits-1 downto 0);

signal cout: std_logic;

begin

-- Insert values for generic parameters !!

uut: carry_ripple_adder generic map (n => Nbits)

port map ( a => a,

b => b,

cin => cin,

s => s,

cout => cout);

stimulus: process

begin

a <= "0100";

b <= "0101";

cin <= '0';

wait for 100 ns ;

cin <= '1';

wait for 100 ns ;

end process;

end;

|

- Logic Block:

Simulações

| Nº Bits | ALMs | Potência (mW) | Report Path | Report Timing | Caminho crítico | Logic Block | Optimization | Seed |

|---|---|---|---|---|---|---|---|---|

| 4 | 40 | 142.58 | 4.021 | 4.253 | deserial0-dout[0]-internal[3] | S | Balanced | 1 |

| 32 | 287 | 184.61 | 18.954 | 19.186 | deserial1-dout[0]-internal[31] | S | Balanced | 1 |

| 128 | 1.041 | 307.58 | 64.238 | 64.791 (VIOLATED) | deserial0-dout[0]-internal[127] | Auto | Balanced | 1 |