Mudanças entre as edições de "Experimento 11 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 20: | Linha 20: | ||

*Após salvar o arquivo como registrador.bdf em uma pasta vazia com nome Exp11, e crie um projeto registrador.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE22F17C6. Após isso compile o projeto. | *Após salvar o arquivo como registrador.bdf em uma pasta vazia com nome Exp11, e crie um projeto registrador.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE22F17C6. Após isso compile o projeto. | ||

| − | == Gerar formas de onda para entrada de simulação== | + | ==Gerar formas de onda para entrada de simulação== |

*Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf. | *Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf. | ||

[[Imagem:Exp11_entrada.png|900px]] | [[Imagem:Exp11_entrada.png|900px]] | ||

| Linha 37: | Linha 37: | ||

*Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático. | *Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático. | ||

| − | =Gravando o projeto no FPGA= | + | ==Gravando o projeto no FPGA== |

*Use a porta USB-Blaster para fazer a programação na placa DE0-NANO; | *Use a porta USB-Blaster para fazer a programação na placa DE0-NANO; | ||

*No Quartus vá em (Tools > Programmer) para abrir a página de programação; | *No Quartus vá em (Tools > Programmer) para abrir a página de programação; | ||

**Selecione o Hardware (Hardware Setup > USB-Blaster); | **Selecione o Hardware (Hardware Setup > USB-Blaster); | ||

**Utilize o modo JTAG e clique em Start para começar a programação; | **Utilize o modo JTAG e clique em Start para começar a programação; | ||

Edição das 08h04min de 8 de agosto de 2014

Experimento 11

- Objetivos

- Entender o funcionamento de um Registrador de deslocamento:

- Inserir diagrama esquemático de um circuito lógico com o Quartus II;

- Gerar formas de onda para entrada de simulação;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Preparar o circuito lógico para gravação em um kit de desenvolvimento;

- Gravando o projeto no FPGA;

- Materiais necessários

- CI 74X74 (disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DEO-NANO;

Inserir diagrama esquemático de um circuito lógico com o Quartus II

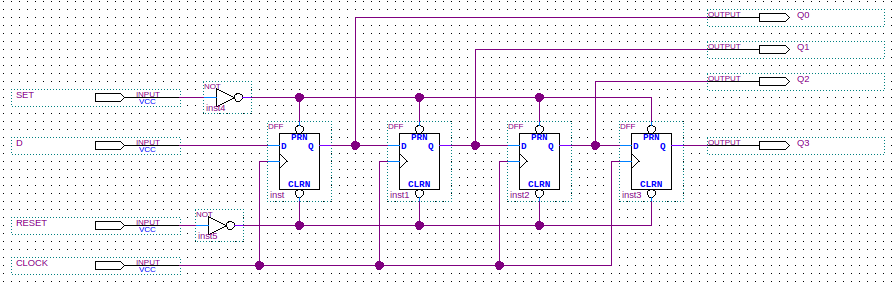

- Abra o Quartus II (versão 13.1) e insira o diagrama esquemático conforme a figura abaixo.

- Após salvar o arquivo como registrador.bdf em uma pasta vazia com nome Exp11, e crie um projeto registrador.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE22F17C6. Após isso compile o projeto.

Gerar formas de onda para entrada de simulação

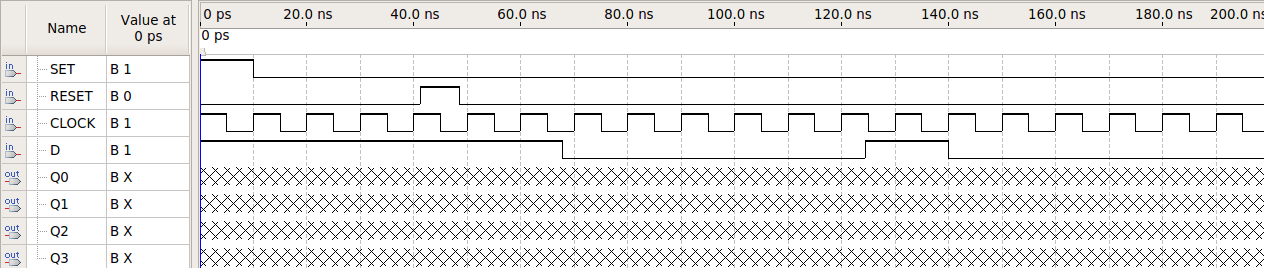

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf.

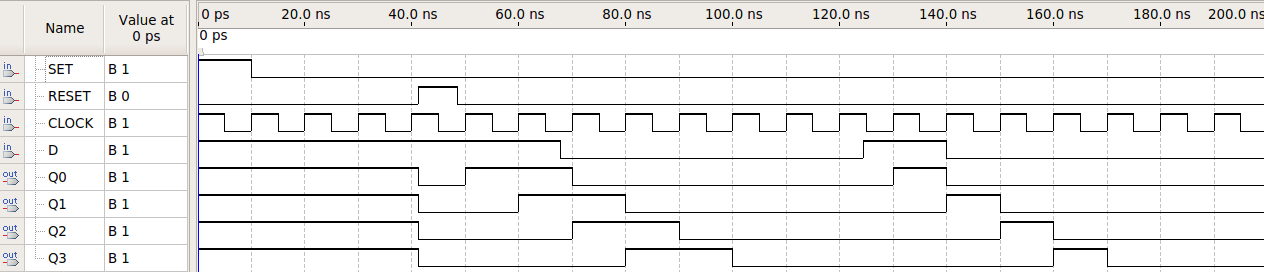

Obter o sinal de saída simulado usando o QSIM - diagrama funcional

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.

Preparar o circuito lógico para gravação em um kit de desenvolvimento

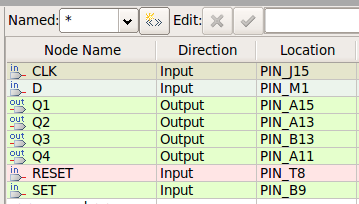

- Atribua os pinos conforme a pinagem do kit DE0-Nano

- Utilize como entradas a chave KEY[0] como CLK, DIPswitch[0] como D, DIPswitch[1] como RESET e DIPswitch[2] como SET.

- Utilize como saída os leds LED[0] a LED[3](verdes) de Q0-Q3.

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático.

Gravando o projeto no FPGA

- Use a porta USB-Blaster para fazer a programação na placa DE0-NANO;

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;