Mudanças entre as edições de "Experimento 9 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 10: | Linha 10: | ||

#Flip-FLop D (disponível na bilbioteca da ALTERA) | #Flip-FLop D (disponível na bilbioteca da ALTERA) | ||

#Computador com software Quartus II da Altera. | #Computador com software Quartus II da Altera. | ||

| − | |||

==Inserir diagrama esquemático de um circuito lógico com o QuartusII de um Contador UP/DOWN== | ==Inserir diagrama esquemático de um circuito lógico com o QuartusII de um Contador UP/DOWN== | ||

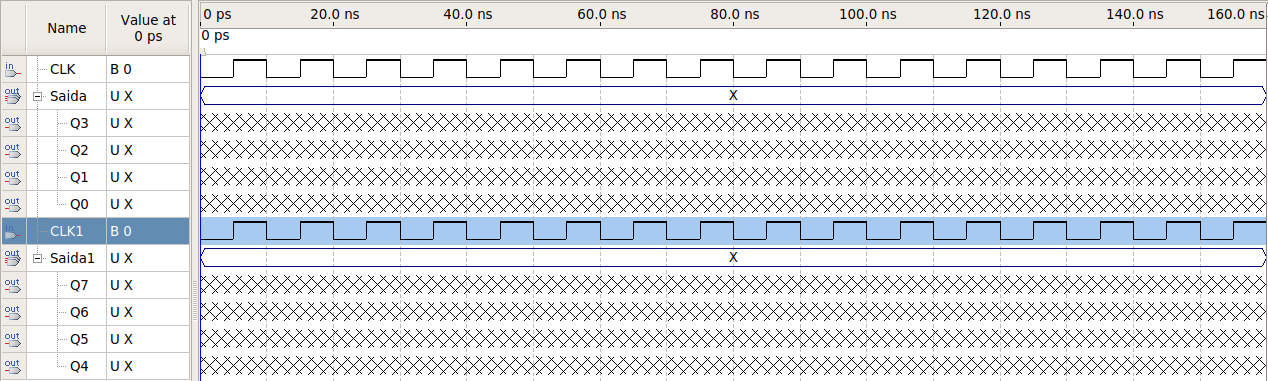

| + | Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com os circuitos contadores assíncrono UP/DOWN conforme a figura abaixo. | ||

[[Imagem:Exp9_diag.png|800px]] | [[Imagem:Exp9_diag.png|800px]] | ||

| + | |||

| + | Após salvar o arquivo como cont.bdf em uma pasta vazia com nome Exp2, e crie um projeto cont.qpf utilizando a família family='''Cyclone ''' com o dispositivo device='''EP1C3T100A8'''. Após isso compile o projeto. | ||

==Gerar formas de onda para entrada de simulação== | ==Gerar formas de onda para entrada de simulação== | ||

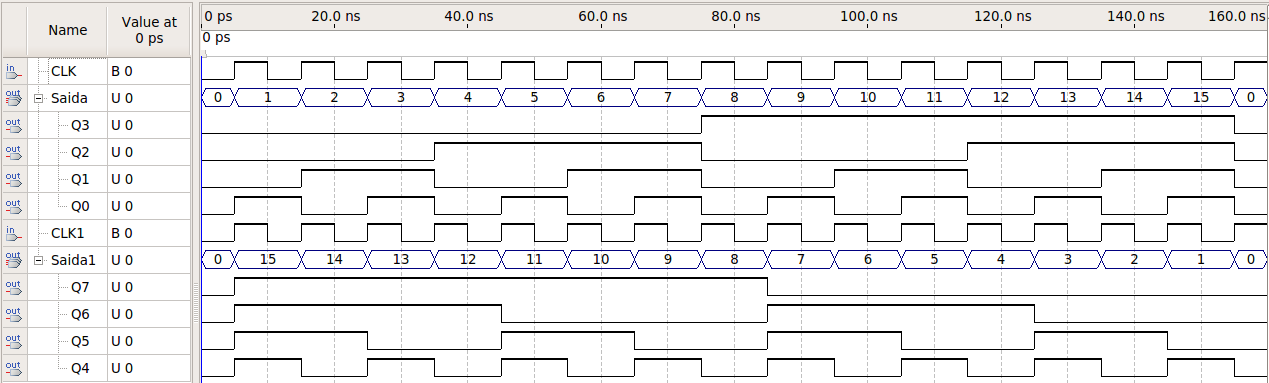

| + | *Faça o agrupamento das entradas, selecione-as (Botão direito do mouse > Grouping > Group > Name "Entradas" > Radix: Unsigned Decimal > OK) | ||

| + | *Desenhe a forma de onda dos sinais de entrada selecionando a linha do agrupamento("Entradas") e clicando [[Imagem:cont.png |Count Value]](Count type > Gray code > OK) gerando assim o sinal exibido na figura abaixo, e salve com o nome EntradaFunc.vwf. | ||

| + | |||

[[Imagem:Exp9_entrada.png|900px]] | [[Imagem:Exp9_entrada.png|900px]] | ||

==Fazer a simulação funcional de um circuito com o QSIM== | ==Fazer a simulação funcional de um circuito com o QSIM== | ||

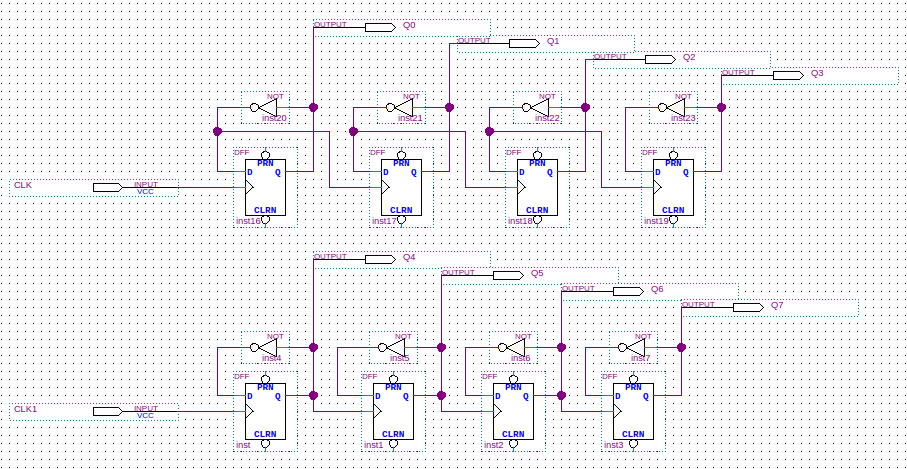

| + | *Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK). | ||

| + | *Indique como a simulação será feita (Simulation > Run Functional Simulation). | ||

| + | *Verifique se o resultado obtido corresponde a respostas do circuito implementado. | ||

[[Imagem:Exp9_saida.png|900px]] | [[Imagem:Exp9_saida.png|900px]] | ||

==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ==Preparar o circuito lógico para gravação em um kit de desenvolvimento== | ||

| + | |||

==Verificar os resultados obtidos== | ==Verificar os resultados obtidos== | ||

Edição das 17h46min de 4 de agosto de 2014

Experimento 9

- Objetivos

- Inserir diagrama esquemático de um circuito lógico com o Quartus II de um Contador UP/DOWN (circuito discreto);

- Gerar formas de onda para entrada de simulação;

- Fazer a simulação funcional de um circuito com o QSIM;

- Preparar o circuito lógico para gravação em um kit de desenvolvimento;

- Verificar os resultados obtidos;

- Materiais necessários

- Flip-FLop D (disponível na bilbioteca da ALTERA)

- Computador com software Quartus II da Altera.

Inserir diagrama esquemático de um circuito lógico com o QuartusII de um Contador UP/DOWN

Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com os circuitos contadores assíncrono UP/DOWN conforme a figura abaixo.

Após salvar o arquivo como cont.bdf em uma pasta vazia com nome Exp2, e crie um projeto cont.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

Gerar formas de onda para entrada de simulação

- Faça o agrupamento das entradas, selecione-as (Botão direito do mouse > Grouping > Group > Name "Entradas" > Radix: Unsigned Decimal > OK)

- Desenhe a forma de onda dos sinais de entrada selecionando a linha do agrupamento("Entradas") e clicando

(Count type > Gray code > OK) gerando assim o sinal exibido na figura abaixo, e salve com o nome EntradaFunc.vwf.

(Count type > Gray code > OK) gerando assim o sinal exibido na figura abaixo, e salve com o nome EntradaFunc.vwf.

Fazer a simulação funcional de um circuito com o QSIM

- Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK).

- Indique como a simulação será feita (Simulation > Run Functional Simulation).

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.