Mudanças entre as edições de "Experimento 4 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 48: | Linha 48: | ||

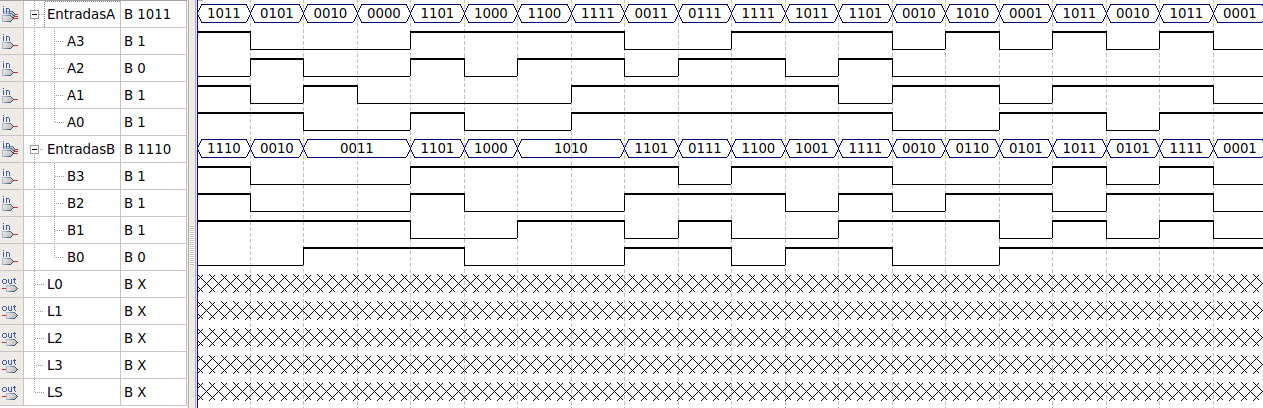

==Obter o sinal de saída simulado usando o QSIM - diagrama funcional== | ==Obter o sinal de saída simulado usando o QSIM - diagrama funcional== | ||

| + | [[Imagem:Exp4_entrada.png|900px]] | ||

| + | |||

==Definir a pinagem de saída== | ==Definir a pinagem de saída== | ||

==Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade)== | ==Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade)== | ||

==Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito== | ==Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito== | ||

Edição das 07h42min de 21 de julho de 2014

Experimento 4

- Objetivos

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas XOR e XNOR;

- Compreender o funcionamento das portas XOR e XNOR;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Definir a pinagem de saída;

- Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade); DE2-115

- Entender o preenchimento da tabela verdade seguindo o resultado apresentado pelo circuito;

- Materiais necessários

- CI 74X386 XOR(disponível na biblioteca da ALTERA)

- CI 74X266 XNOR(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DE2-115;

Porta Xor

- Símbolo:

- Expressão booleana:

- Tabela verdade:

| Entradas | Saídas | |

|---|---|---|

| A | B | S |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

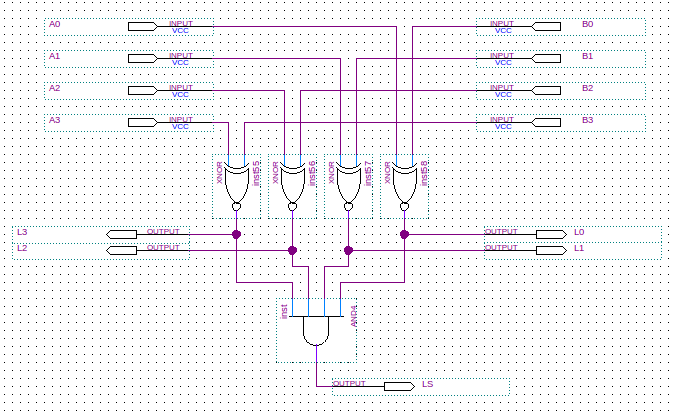

Diagrama Esquemático do comparador de igualdade

Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com portas XNor, conforme a figura abaixo.

Após salvar o arquivo como portaXNor.bdf em uma pasta vazia com nome Exp1, e crie um projeto portasXNor.qpf utilizando a família family=Cyclone IV com o dispositivo device=EP4CE115F29C7. Após isso compile o projeto.