Mudanças entre as edições de "Experimento 2 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| Linha 38: | Linha 38: | ||

==Uso do cursor para a medição do atraso de propagação== | ==Uso do cursor para a medição do atraso de propagação== | ||

| + | (...) | ||

| + | |||

| + | =Compreender o funcionamento das portas OR, NOT e NOR= | ||

| + | *Verifique que as saídas AB, ABC, ABCD se comportam, respectivamente como portas OR, NOT e NOR aplicadas nas entradas 2, 3 e 4. | ||

| + | |||

| + | =Obtenção da tabela verdade de circuitos lógicos= | ||

| + | *Preencha a tabela verdade de acordo com a resposta obtida com a simulação do arquivo de entrada. | ||

| + | |||

| + | <center> | ||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | ! colspan="4" style="background: #efefef;" | Entradas | ||

| + | ! colspan="3" style="background: #ffdead;" | Saídas | ||

| + | |- | ||

| + | !width="30"| A | ||

| + | !width="30"| B | ||

| + | !width="30"| C | ||

| + | !width="30"| D | ||

| + | !width="50"| AB | ||

| + | !width="50"| ABC | ||

| + | !width="50"| ABCD | ||

| + | |- | ||

| + | | 0 || 0 || 0 || 0 || || | || | ||

| + | |- | ||

| + | | 0 || 0 || 0 || 1 || || | || | ||

| + | |- | ||

| + | | 0 || 0 || 1 || 0 || || | || | ||

| + | |- | ||

| + | | 0 || 0 || 1 || 1 || || | || | ||

| + | |- | ||

| + | | 0 || 1 || 0 || 0 || || | || | ||

| + | |- | ||

| + | | 0 || 1 || 0 || 1 || || | || | ||

| + | |- | ||

| + | | 0 || 1 || 1 || 0 || || | || | ||

| + | |- | ||

| + | | 0 || 1 || 1 || 1 || || | || | ||

| + | |- | ||

| + | | 1 || 0 || 0 || 0 || || | || | ||

| + | |- | ||

| + | | 1 || 0 || 0 || 1 || || | || | ||

| + | |- | ||

| + | | 1 || 0 || 1 || 0 || || | || | ||

| + | |- | ||

| + | | 1 || 0 || 1 || 1 || || | || | ||

| + | |- | ||

| + | | 1 || 1 || 0 || 0 || || | || | ||

| + | |- | ||

| + | | 1 || 1 || 0 || 1 || || | || | ||

| + | |- | ||

| + | | 1 || 1 || 1 || 0 || || | || | ||

| + | |- | ||

| + | | 1 || 1 || 1 || 1 || || | || | ||

| + | |- | ||

| + | |} | ||

| + | </center> | ||

Edição das 10h07min de 13 de junho de 2014

- Objetivos

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas OR, NOT e NOR;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Obter o sinal de saída simulado usando o QSIM - diagrama temporal (uso de cursores para medições);

- Compreender o funcionamento das porta OR, NOT e NOR;

- Entender a tabela verdade de circuitos lógicos;

- Materiais necessários

- CI 74X32 OR(disponível na biblioteca da ALTERA)

- CI 74X04 NOT(disponível na biblioteca da ALTERA)

- CI 74X02 NOR(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

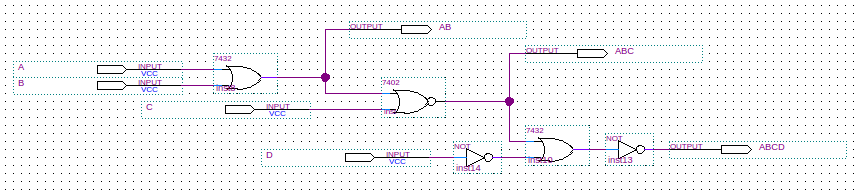

Diagrama Esquemático

Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com portas OR/NOR/NOT, conforme a figura abaixo.

Após salvar o arquivo como portasOrNorNot.bdf em uma pasta vazia com nome Exp1, e crie um projeto portasOrNorNot.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

Obter o sinal de saída simulado usando o QSIM - diagrama funcional

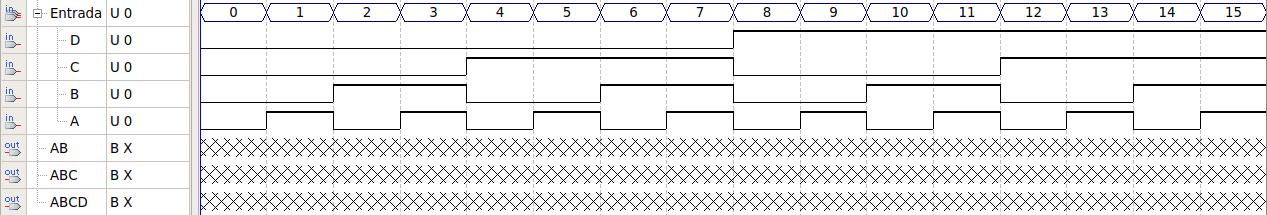

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome EntradaFunc.vwf.

- Para fazer o agrupamento das entradas, selecione-as (Botão Direito do mouse > Grouping > Group > Name "Entradas" > Radix: Unsigned Decimal > OK)

- Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK).

- Indique como a simulação será feita (Simulation > Run Functional Simulation).

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.

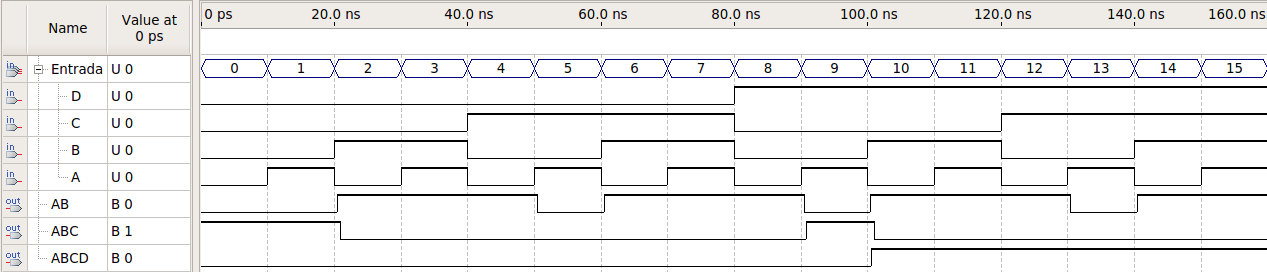

Obter o sinal de saída simulado usando o QSIM - diagrama temporal

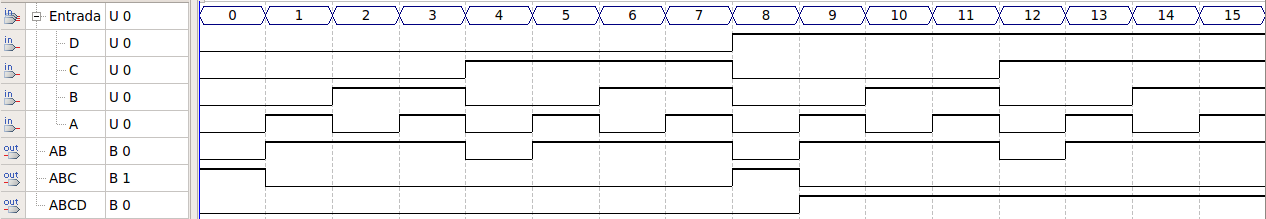

- Selecione o Quartus II como simulador (Simulation > Options > Quartus II Simulator > OK).

- Indique como a simulação será feita (Simulation > Run Timing Simulation).

- Verifique se o resultado obtido corresponde a respostas do circuito implementado.

- Analise o atraso de propagação indicado na simulação.

Uso do cursor para a medição do atraso de propagação

(...)

Compreender o funcionamento das portas OR, NOT e NOR

- Verifique que as saídas AB, ABC, ABCD se comportam, respectivamente como portas OR, NOT e NOR aplicadas nas entradas 2, 3 e 4.

Obtenção da tabela verdade de circuitos lógicos

- Preencha a tabela verdade de acordo com a resposta obtida com a simulação do arquivo de entrada.

| Entradas | Saídas | |||||

|---|---|---|---|---|---|---|

| A | B | C | D | AB | ABC | ABCD |

| 0 | 0 | 0 | 0 | |||

| 0 | 0 | 0 | 1 | |||

| 0 | 0 | 1 | 0 | |||

| 0 | 0 | 1 | 1 | |||

| 0 | 1 | 0 | 0 | |||

| 0 | 1 | 0 | 1 | |||

| 0 | 1 | 1 | 0 | |||

| 0 | 1 | 1 | 1 | |||

| 1 | 0 | 0 | 0 | |||

| 1 | 0 | 0 | 1 | |||

| 1 | 0 | 1 | 0 | |||

| 1 | 0 | 1 | 1 | |||

| 1 | 1 | 0 | 0 | |||

| 1 | 1 | 0 | 1 | |||

| 1 | 1 | 1 | 0 | |||

| 1 | 1 | 1 | 1 | |||