Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 516: | Linha 516: | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ==Avaliações== | ||

| + | Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues: | ||

| + | <!-- | ||

| + | *[[Media:VHDL_QRC-Qualis.pdf | VHDL QUICK REFERENCE CARD]] - Qualis | ||

| + | *[[Media:VHDL1164_QRC-Qualis.pdf | VHDL 1164 PACKAGES QUICK REFERENCE CARD]] Qualis | ||

| + | --> | ||

| + | *[[Media:VHDL_QRC-SynthWorks.pdf | VHDL Quick Reference]] - SynthWorks | ||

| + | *[[Media:VHDL_Type_Operators_QR-SynthWorks.pdf | VHDL Types and Operators Quick Reference]] - SynthWorks | ||

| + | *[[Media:ModelSim_QR-SynthWorks.pdf |ModelSim Quick Reference]] - SynthWorks | ||

| + | *[[Media:Tabelas_Pedroni.pdf | Tabelas das figuras 3.6, 3.10 e 4.1]] do livro do Pedroni. | ||

| + | *[[Arquivo:Numeric_std_conversions.png | Diagrama de conversões de tipos numéricos no pacote Numeric_std ]] | ||

| + | ::Dica use também como fonte de consulta os '''templates''' do Quartus. | ||

| + | ::Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados. | ||

| + | |||

| + | == ATIVIDADE EXTRA-CLASSE (AE) == | ||

| + | A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo. | ||

| + | {{collapse top |expand=1| bg=lightyellow | AE1 - Palavras-cruzadas INTRODUÇÃO}} | ||

| + | ===AE1 - Palavras-cruzadas INTRODUÇÃO=== | ||

| + | ;BÔNUS: | ||

| + | *0,3 pontos na avaliação A1 - | ||

| + | *0,2 pontos na avaliação A1 - | ||

| + | *0,1 pontos na avaliação A1 - | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | <!-- | ||

| + | {{collapse top |expand=1| bg=lightyellow | AE2 - Uso de operadores e tipos de dados}} | ||

| + | |||

| + | ===AE2 - Uso de operadores e tipos de dados=== | ||

| + | ;Atividade: | ||

| + | *Baseado no exemplo do conversor de binário para BCD - Binary-coded decimal de dois dígitos decimais (00 a 99), mostrado em aula, projete um conversor para 3 dígitos (000 a 999). | ||

| + | :*Escreva o código em VHDL, que dada uma entrada C (entre 0 e 999), fornece nas saídas os dígitos da centena (sc), dezena (sd) e unidade (su). | ||

| + | :*Anote a quantidade de elementos lógicos que são necessários. | ||

| + | :*Procure reduzir essa quantidade, aproveitando resultados intermediários e evitando a realização de uma nova divisão pelo uso do operador REM. | ||

| + | :*É obrigatório o uso de um dispositivo da família Cyclone (I). O tamanho do dispositivo pode ser escolhido entre as várias opções disponíveis. | ||

| + | |||

| + | :*Para facilitar os testes a ENTITY do projeto deverá ter o seguinte formato: | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity bin2bcd is | ||

| + | port ( | ||

| + | C : in std_logic_vector(9 downto 0); | ||

| + | sc : out std_logic_vector(3 downto 0); | ||

| + | sd : out std_logic_vector(3 downto 0); | ||

| + | su : out std_logic_vector(3 downto 0)); | ||

| + | |||

| + | end entity; | ||

| + | |||

| + | architecture example of bin2bcdCDU is | ||

| + | --declaração de sinais auxiliares | ||

| + | |||

| + | begin | ||

| + | --descrição do hardware | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | :*Para mostrar que o conversor funciona faça a simulação funcional do projeto usando o QSIM. Use dados de entrada que permitam verificar o funcionamento do conversor. | ||

| + | :*Para ver os máximo atraso de propagação entre a entrada e saída, veja o link [https://wiki.sj.ifsc.edu.br/wiki/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Tempo_de_Propaga.C3.A7.C3.A3o_entre_entrada_e_sa.C3.ADda]. | ||

| + | |||

| + | {{fig|AE1.a|Exemplo de simulação funcional| bin2bcd_SIM_fucional.png| 600 px |}} | ||

| + | {{fig|AE1.b|Exemplo de simulação temporal| bin2bcd_SIM_temporal.png| 600 px |}} | ||

| + | {{fig|AE1.c|Exemplo de número de elementos (166) | bin2bcd_logic_elements_basico.png| 600 px |}} | ||

| + | {{fig|AE1.d|Exemplo de número de elementos (166) | bin2bcd_logic_elements_melhorado.png| 600 px |}} | ||

| + | {{fig|AE1.e|Exemplo de tempo máximo de propagação (60,588 ns) | bin2bcd_propagation_delay.png| 600 px |}} | ||

| + | |||

| + | '''Nota''': Existe um algoritmo [https://en.wikipedia.org/wiki/Double_dabble Double Dabble] que possibilita fazer essa conversão com menos hardware, mas esse algoritmo não poderá ser utilizado neste exercício. | ||

| + | |||

| + | ;Entregas: | ||

| + | #Envie o QAR contendo todos os arquivos necessário para compilar e simular o projeto, a impressão da tela do RTL, simulação funcional do projeto e simulação temporal do projeto. Se preferir as imagens podem ser enviadas em separado. | ||

| + | #No comentário do Moodle indique o número de elementos lógicos e a atraso máximo de propagação entre os bits de entrada e as saídas do projeto | ||

| + | |||

| + | ;Bônus em A1: | ||

| + | * (0,5 pontos) O '''primeiro''' estudante que entregar o projeto. | ||

| + | * (0,5 pontos) O estudante que entregar o projeto com o menor '''número de elementos lógicos'''. | ||

| + | * (0,5 pontos) O estudante que entregar o projeto com o menor '''tempo máximo de propagação'''. | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | |||

| + | {{collapse top| expand=1 | bg=lightyellow | AE3 - Implemente um circuito de incrementador Gray}} | ||

| + | |||

| + | ===AE3 - Implemente um circuito de incrementador Gray=== | ||

| + | *[https://moodle.ifsc.edu.br/mod/assign/view.php?id=286383 AE3 - Implemente um circuito de incrementador Gray] | ||

| + | :*Implemente um incrementador Gray, o qual dada uma entrada de N bits em código Gray fornece na saída o valor seguinte em [[Código Gray]]. | ||

| + | ::Use como base o modelo de entidade abaixo: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity inc_gray is | ||

| + | port | ||

| + | ( | ||

| + | gray_in : in std_logic_vector(____) | ||

| + | gray_out : out std_logic_vector(____) | ||

| + | ) | ||

| + | end entity | ||

| + | |||

| + | architecture ____ of inc_gray is | ||

| + | begin | ||

| + | |||

| + | end architecture | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::Por exemplo: se a entrada de 4 bits for 2 = "0011" a saída será o 3 = "0010". | ||

| + | :* Mostre que o circuito funciona, fazendo a sua simulação funcional (use o QSIM ou Modelsim). | ||

| + | ;BÔNUS: O primeiro aluno(a) que entregar o circuito funcionando receberá um '''bônus de 0,4 na avaliação A1'''. | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top| expand=1 | bg=lightyellow | AE4 - ALU modificada }} | ||

| + | ===AE4 - ALU modificada=== | ||

| + | 1) Faça um novo circuito que inclua um sinal que indica "erro" quando ocorrer overflow/underflow nas operações de soma, incremento ou decremento. | ||

| + | |||

| + | 2) Faça um novo circuito que sature o sinal de saída no máximo positivo ou negativo nas situações de erro. | ||

| + | |||

| + | Para ambos circuitos modificados: | ||

| + | *Faça simulações funcionais com Modelsim (ou QSIM) utilizando 3 bits, mostrando tanto o funcionamento normal como as situações de erro. É necessário fazer os testes para os diferentes OPCODES. No caso do OPCODES lógicos um ou dois testes são suficientes, mas no caso do incremento, decremento, é recomendado que envolva os limites "000" e "111" nas entradas. | ||

| + | *Deve ser feita a mesma simulação para o circuito original e as duas versões modificadas. | ||

| + | *Escreva o código VHDL e analise o número de elementos lógicos necessários. | ||

| + | |||

| + | ;Bonus: | ||

| + | *(0.5 pontos na avaliação A1) para o primeiro aluno que entregar o código com a indicação de erro | ||

| + | *(0.5 pontos na avaliação A1) para o primeiro aluno que entregar o código com a saturação da saída. | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top| expand=true | bg=lightyellow | AE5 - Laboratório de programação de FPGA - Timer 00 a 99 segundos sem o uso de componente - versão 1}} | ||

| + | ===AE5 - Laboratório de programação de FPGA - Timer 00 a 99 (versão 1)=== | ||

| + | *[https://moodle.ifsc.edu.br/course/view.php?id=9091 AE5 - Laboratório de programação de FPGA - Timer 00 a 99 segundos em componente versão 1] | ||

| + | Projete um contador BCD de 00 a 99 configurável com saída em 2 mostradores de 7 segmentos. | ||

| + | *Utilize o timer 0 a 9 desenvolvido em aula como base, substituindo o contador 0 a 9 pelo contador BCD 00 a 99. | ||

| + | *O contador deve ser configurável para contar qualquer valor entre 01 até 99. | ||

| + | *Efetue a simulação funcional (Usando Modelsim) fazendo a contagem de 00 a 11 e também de 00 a 23 (para hora), de 00 a 59 (para minutos e segundos), e de 00 a 99. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity Timer00_99seg is | ||

| + | port ( | ||

| + | clk50MHz : in std_logic; | ||

| + | clk1seg : out std_logic; | ||

| + | SSD_Useg : out std_logic_vector(0 to 6); | ||

| + | SSD_Dseg : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | * Configure o FPGA do kit Mercúrio IV para implementar este circuito. Utilize os mostradores ssd DISP0_D e DISP1_D. | ||

| + | * Após verificar que o circuito funciona "simulado", configurar o FPGA do '''kit Mercúrio IV''' para implementar este circuito. | ||

| + | * As informações necessárias para configurar o dispositivo e seus pinos estão em [[Preparando para gravar o circuito lógico no FPGA]]. | ||

| + | * Projeto e simulação com Modelsim do sistema Timer00-99 com display de 7 segmentos e divisor de clock. | ||

| + | * Na simulação definir o clk50MHz como 100ms para produzir um clk1sec com duração de 1 segundo. | ||

| + | * Corrigir o primeiro período de clock de clk1sec. É necessário fazer com que o sinal seja alto primeiro e depois vá para baixo de modo a garantir que a transição positiva ocorra depois de 1 segundo. | ||

| + | *'''IMPORTANTE''': Também é necessário incluir um RESET em cada circuito que seja sequencial. Também é necessário iniciar o circuito com um reset de 10 ps na simulação. | ||

| + | * Perceber a necessidade de parametrizar o conversor de bcd2ssd para permitir displays do tipo CA e AA. (ler [[Display de 7 segmentos]]) | ||

| + | * Perceber a necessidade de incluir um sinal que indique o final da contagem no counter00_99. Esse sinal poderá ser usado como clock no relógio a ser projetado. | ||

| + | --> | ||

| + | <!-- | ||

| + | ;Bonus: | ||

| + | *(1 pontos na avaliação A2) para o primeiro estudante que entregar o QAR com o código e as simulações feitas | ||

| + | *(0.5 pontos na avaliação A2) para o primeiro estudante que entregar o arquivo SOF fazendo a contagem corretamente no kit da Macnica Mercúrio IV. | ||

| + | *(1 ponto na avaliação A2) para o primeiro estudante que entregar o arquivo SOF que além de fazer a contagem, mostre a matriz de leds indicando o valor BCD da dezena na primeira linha e o valor BCD da unidade na segunda linha. Dicas de como fazer ver [[Como utilizar a matriz de leds do kit Mercurio IV da Macnica]] | ||

| + | --> | ||

| + | <!-- | ||

| + | <center> {{#ev:youtube|orjy0GURH_U}} </center> | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | {{collapse top |expand=1| bg=lightyellow | AE6 - Laboratório de programação de FPGA - Timer 00 a 99 (versão 2)}} | ||

| + | ===AE6 - Laboratório de programação de FPGA - Timer 00 a 99 (versão 2)=== | ||

| + | *[https://moodle.ifsc.edu.br/course/view.php?id=9091 AE6 - Laboratório de programação de FPGA - Timer 00 a 99 segundos usando componentes - versão 2] | ||

| + | |||

| + | ;Atividade: | ||

| + | Envie nesta atividade o projeto do Timer 00 a 99 segundos, com saída em display de 7 segmentos. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity timer00_99seg IS | ||

| + | generic (fclk2 : natural := 50, D : natural := 5; U : natural := 9); | ||

| + | port | ||

| + | ( | ||

| + | clk50MHz : in STD_LOGIC; | ||

| + | clk_1seg: out STD_LOGIC; | ||

| + | ssd_D : out STD_LOGIC_VECTOR(0 TO 6); | ||

| + | ssd_U : out STD_LOGIC_VECTOR(0 TO 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | |||

| + | O projeto deve ser dividido em pelo menos os seguintes componentes (ver exemplo do RTL abaixo) | ||

| + | {{fig|AE6.a|RTL do Timer 00 a 99 segundos| Rtl_timer99sec.png| 800 px |}} | ||

| + | |||

| + | *Componente 1 - Divisor de Clock, com o valor da divisão configurável pelo parâmetro '''fclk2'''. O sinal de saída será usado como "enable" ou "clock" a cada 1 segundo para o componente '''count00_99'''. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component div_clk is | ||

| + | generic (fclk2 : natural := 50); -- frequecia para simulacao | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic | ||

| + | ); | ||

| + | end component; | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | *Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos parâmetros '''D e U''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component count00_99 is | ||

| + | generic (D : natural := 9; U : natural := 9); | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Componente 3 - Conversor de BIN para SSD, com um parâmetro configurável '''ac_ccn''' para selecionar Anodo ou Catodo Comum. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component bin2ssd is | ||

| + | generic (ac_ccn : natural := 0); | ||

| + | port ( | ||

| + | bin_in : in std_logic_vector(3 downto 0); | ||

| + | ssd_out : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;OBS: | ||

| + | *O valor ac_ccn é utilizado para configurar o circuito entre ativo alto para display de catodo comum (ac_ccn=0), ou ativo baixo para display de anodo comum (ac_ccn=1). | ||

| + | |||

| + | * Simulação do timer com ModelSim. Na simulação definir o clk50MHz com duração de 10 ms. Faça uma simulação de pelo menos 60 segundos. O projeto deve ser simulado por componente e após isso ser feita a integração dos componentes (Ver exemplo de teste de simulação abaixo) | ||

| + | |||

| + | {{fig|AE6.b|Simulação funcional do Timer 00 a 99 segundos| Sim_timer99sec.png| 800 px |}} | ||

| + | |||

| + | *Após a verificação do funcionamento por simulação funcional, utilizar o lab home office para enviar o hardware para o kit e comunicar ao professor para verificar se funcionou corretamente. | ||

| + | |||

| + | *É recomendável inserir um sinal de RESET em todos os circuitos sequenciais e ao iniciar a simulação do circuito começar com RESET ativo durante 10 ps. | ||

| + | |||

| + | *Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. | ||

| + | |||

| + | * Se utilizar o kit DE2-115 da TERASIC, utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0-5[0-6]: PIN_G18 - PIN_H22 ...). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <pre> | ||

| + | </pre> | ||

| + | {{collapse bottom}} | ||

| + | *Se utilizar o kit Mercúrio IV da MACNICA, utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | |||

| + | {{collapse top| definição dos pinos}} | ||

| + | <pre> | ||

| + | set_location_assignment PIN_T1 -to clk50MHz | ||

| + | set_location_assignment PIN_V21 -to rst_in | ||

| + | set_location_assignment PIN_R5 -to ssd_D[0] | ||

| + | set_location_assignment PIN_T5 -to ssd_D[1] | ||

| + | set_location_assignment PIN_T3 -to ssd_D[2] | ||

| + | set_location_assignment PIN_T4 -to ssd_D[3] | ||

| + | set_location_assignment PIN_M6 -to ssd_D[4] | ||

| + | set_location_assignment PIN_N7 -to ssd_D[5] | ||

| + | set_location_assignment PIN_N6 -to ssd_D[6] | ||

| + | set_location_assignment PIN_V2 -to ssd_U[0] | ||

| + | set_location_assignment PIN_V1 -to ssd_U[1] | ||

| + | set_location_assignment PIN_U2 -to ssd_U[2] | ||

| + | set_location_assignment PIN_U1 -to ssd_U[3] | ||

| + | set_location_assignment PIN_Y2 -to ssd_U[4] | ||

| + | set_location_assignment PIN_Y1 -to ssd_U[5] | ||

| + | set_location_assignment PIN_W2 -to ssd_U[6] | ||

| + | set_location_assignment PIN_W1 -to clk_1seg | ||

| + | </pre> | ||

| + | {{collapse bottom}} | ||

| + | * Analise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O [[Display de 7 segmentos]] da DE2-115 é do tipo cátodo comum, enquanto que na MERCURIO IV ele é do tipo ânodo comum. | ||

| + | |||

| + | ;Entregas: | ||

| + | Nesta atividade devem ser entregues os seguintes arquivos. | ||

| + | *O QAR do projeto com todos os componentes usados. | ||

| + | *A imagem das simulações feitas. | ||

| + | *O arquivo SOF usado na programação do FPGA. | ||

| + | *A imagem do RTL do projeto (com os componentes), não é necessário expandir os componentes. | ||

--> | --> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição das 22h43min de 20 de outubro de 2021

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 3 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 5 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Exemplo de descrição de um multiplexador de 4 entradas entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

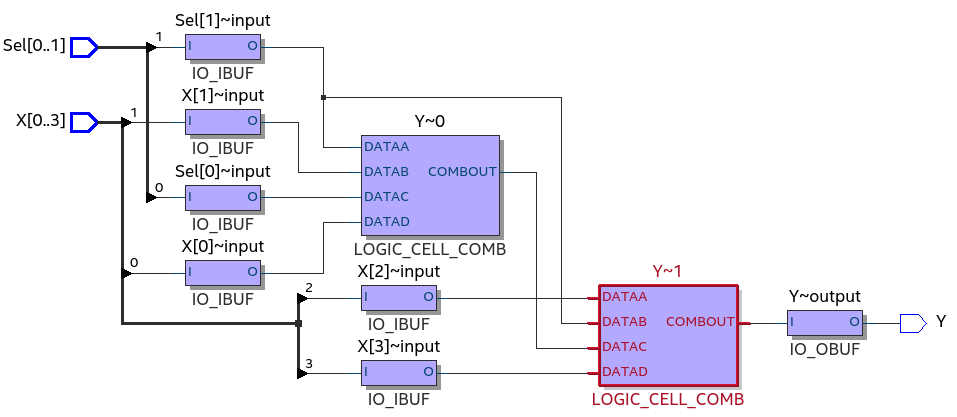

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

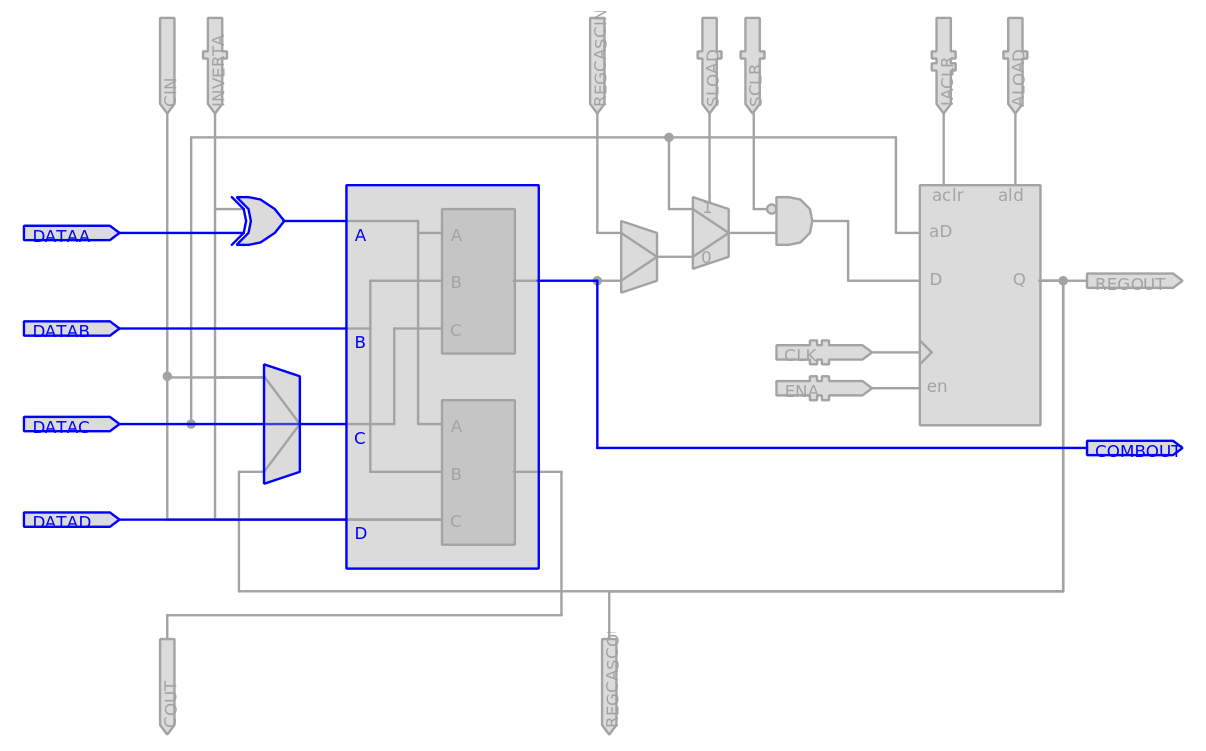

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

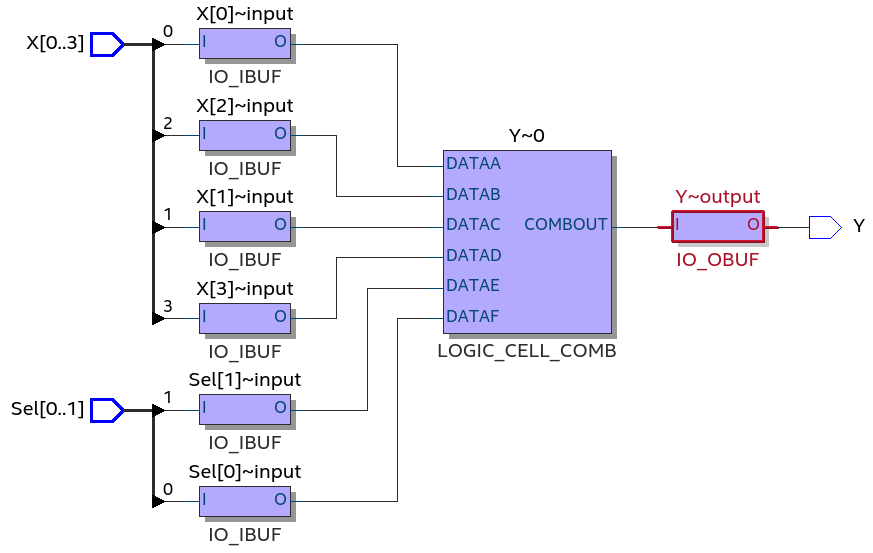

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF  |

Avaliações

Nas avaliações A1 e A2 serão realizadas de forma presencial e vocês poderão consultar apenas as folhas entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 25% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

| AE1 - Palavras-cruzadas INTRODUÇÃO |

|---|

AE1 - Palavras-cruzadas INTRODUÇÃO

|

|}