DLP29006-Engtelecom(2017-2) - Prof. Marcos Moecke: mudanças entre as edições

Ir para navegação

Ir para pesquisar

| Linha 203: | Linha 203: | ||

===Unidade 3=== | ===Unidade 3=== | ||

{{collapse top| Unidade 3}} | |||

;Aula 6 (17 Ago): | ;Aula 6 (17 Ago): | ||

*Tipos de Dados em VHDL. | *Tipos de Dados em VHDL. | ||

| Linha 371: | Linha 372: | ||

:* Exercício 4.17: Desafio para a implementação com menor numero de elementos lógicos (BONUS 1 e 0.5) ver detalhes no [https://moodle.sj.ifsc.edu.br/mod/assign/view.php?id=3483 Moodle]. | :* Exercício 4.17: Desafio para a implementação com menor numero de elementos lógicos (BONUS 1 e 0.5) ver detalhes no [https://moodle.sj.ifsc.edu.br/mod/assign/view.php?id=3483 Moodle]. | ||

:: Ver pag. 108 a 119, 140 a 142 de <ref name="PEDRONI2010b"/> | :: Ver pag. 108 a 119, 140 a 142 de <ref name="PEDRONI2010b"/> | ||

{{collapse bottom}} | |||

===Unidade 4=== | ===Unidade 4=== | ||

Edição das 08h41min de 26 de outubro de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

1 Registro on-line das aulas

1.1 Unidade 1

1.2 Unidade 2

| Unidade 2 |

|---|

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

|

1.3 Unidade 3

| Unidade 3 | ||

|---|---|---|

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_multiplier IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE type_conv_arch OF signed_multiplier IS

BEGIN

y <= std_LOGIC_VECTOR(SIGNED(a) * SIGNED(b));

END ARCHITECTURE;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

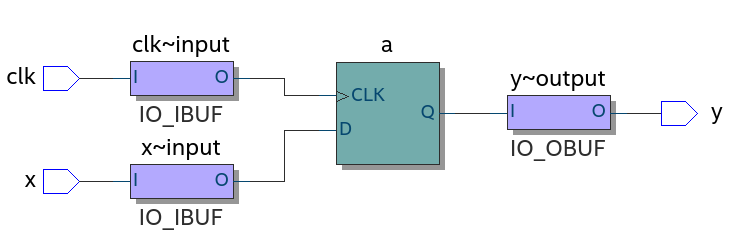

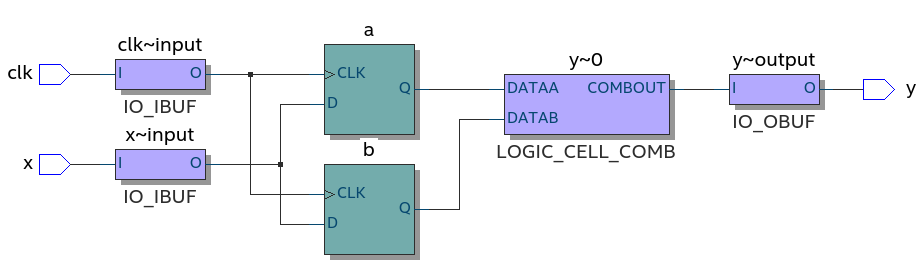

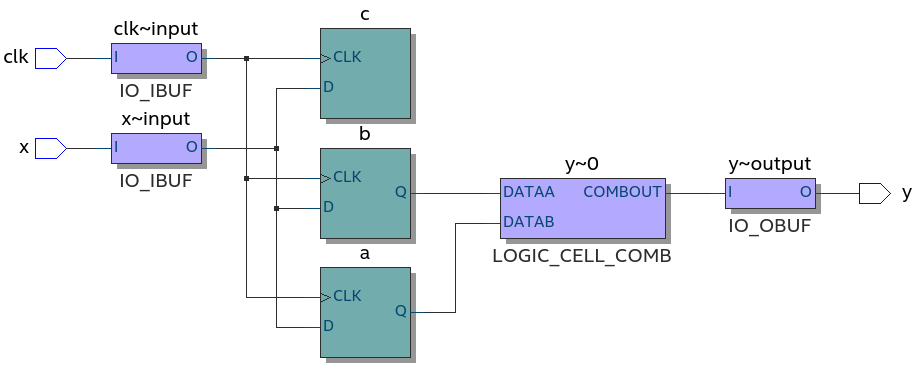

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

1.4 Unidade 4

- Código Concorrente.

- Uso de Operadores

- WHEN, SELECT;

- Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com portas, com WHEN-ELSE, com WITH-SELECT)

- Verifique os três circuitos considerando as entradas x0 a x3 e a saída y com apenas um elemento.

- Modifique os circuitos para que tenham as entradas x0 a x3 e a saída y com 4 elementos.

- No caso do uso de WHEN-ELSE e WITH-SELECT é só alterar o tamanho dos vetores STD_LOGIC_VECTOR.

- Qual é a solução para a descrição com portas?

- Ver pag. 121 a 127 de [2]

- Aula 14 (14 Set)

-

- Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION.

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

- Código Concorrente.

- Exemplo de uso de operadores e SELECT.

- Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU).

- Alteração do código da ALU:

- Inclusão de um sinal que indica "erro" quando ocorre overflow/underflow nas operações de soma, incremento ou decremento.

- Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro.

- Teste da ALU usando simulação funcional.

- Aula 15 (20 Set)

-

- Uso de FOR-GENERATE

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

</syntaxhighlight>

- Exemplo 5.4 - Decodificador genérico de endereços.

- Ver pag. 127 a 134 de [2]

- Implementação de circuitos aritméticos com operadores.

- Para o uso dos operadores o mais adequado é utilizar o padrão industrial STD_LOGIC_VECTOR. Internamente os valores das portas devem ser convertidos ou para valores INTEGER ou para UNSIGNED/SIGNED. para tal é necessário utilizar a biblioteca numeric_std.

- Também é fundamental considerar a faixa de valores coberta por bits. Para tipos UNSIGNED a faixa é de até , enquanto que para SIGNED a faixa é de até . Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED.

- Para uso adequado dos operadores também é necessário considerar o tamanho (número de bits) requerido para o resultado em função do tamanho dos operandos.

- Ver a declaração das funções "+", "-", "*" e "/" no PACKAGE Numeric std.vhd

function "+" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Adds two UNSIGNED vectors that may be of different lengths.

function "-" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Subtracts two UNSIGNED vectors that may be of different lengths.

function "*" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED((L'LENGTH+R'LENGTH-1) downto 0).

-- Result: Performs the multiplication operation on two UNSIGNED vectors

-- that may possibly be of different lengths.

function "/" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(L'LENGTH-1 downto 0)

-- Result: Divides an UNSIGNED vector, L, by another UNSIGNED vector, R.

-- NOTE: If second argument is zero for "/" operator, a severity level of ERROR is issued.

- Para operações de "+" ou "-": O tamanho do resultado é igual ao tamanho do maior operando.

- Exemplo: r[7..0] = a[7..0] + b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8 bits.

- Para a operações "*": O tamanho do resultado é igual a soma do tamanho dos dois operandos.

- Exemplo: r[12..0] = a[7..0] * b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8+5 = 13 bits.

- Para "/": O tamanho do resultado é igual ao tamanho do numerador.

- Exemplo: r[5..0] = a[5..0] / b[8..0]; a -> 6 bits; b -> 9 bits então r -> 6 bits.

- No caso da operações de "*" e "/" não ocorre overflow, no entanto no caso da "+" e "-", o overflow/underflow pode ocorrer e precisa ser tratado. Isso pode ser feito acrescentando um bit adicional a saída para conter o overflow ou então sinalizar a sua ocorrência com um bit na saída do circuito. Note que no caso em que ocorrem sucessivas somas, é impraticável ficar aumentando o número de bits para evitar o overflow, de modo que a sinalização do overflow ou uso de escalas, ou representação em ponto fixo ou ponto flutuante podem ser as soluções a serem adotadas.

- No caso das operações de "+" e "-" também pode ser necessário tratar os sinais de carry in e carry out, que permitem ampliar o tamanho de um somador realizando a sua conexão em cascata, ao mesmo tempo que tratam o overflow.

- Exemplo 5.7 - Somador/Subtrator Recomendado.

- Aula 16 (21 Set)

- Código Concorrente.

- Aula de exercícios:

- 5.3 - Porta AND e NAND Genérica.

- 5.4 - Gerador de Paridade Genérico.

- Aula 17 (25 Set)

- Código Concorrente.

- Aula de exercícios:

- 5.6 - Conversor Binario-Gray Genérico.

- (28 Set, 2 e 5 Out)

- Professor em licença.

- Alunos liberados para desenvolver atividade extra AE1

- Aula 18 (11 Out)

- Código Concorrente.

- Escreve um código VHDL genérico que implemente os seguintes circuitos:

- Ex1 - Conversor de Binário para Gray genérico;

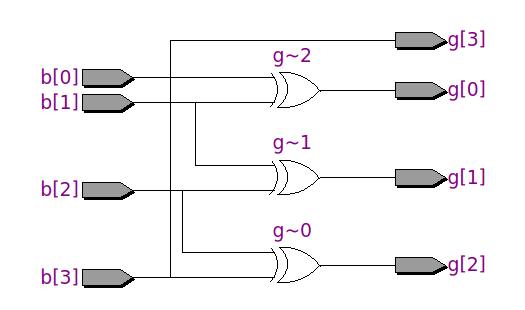

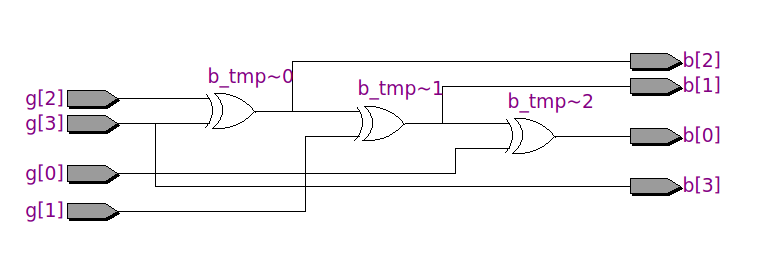

Fig 16. código RTL do conversor binário para Gray - Ex2 - Conversor de Gray para Binário genérico;

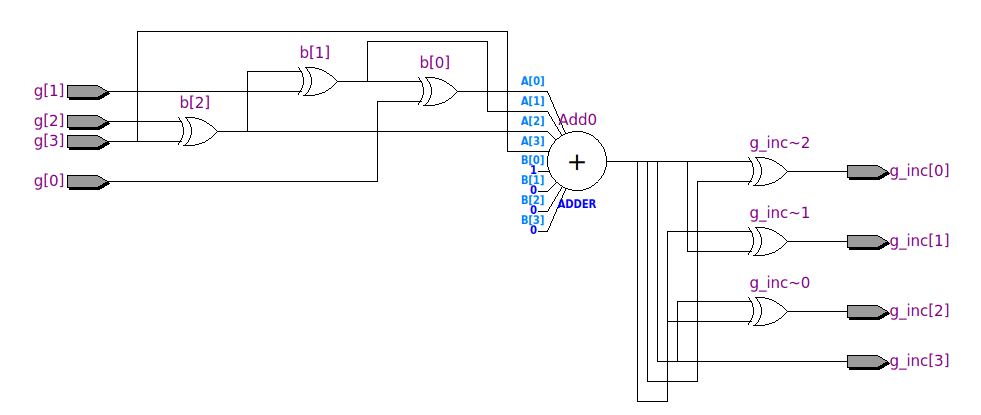

Fig 17. código RTL do conversor Gray para binário - Ex3 - Utilizando os dois circuitos anteriores e um incrementador binário escreva um código VHDL que implemente um incrementador Gray;

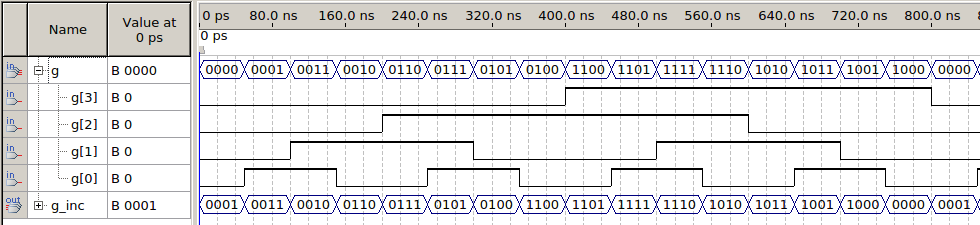

Fig 18. código RTL do incrementador de código Gray - Realize a simulação do incrementador Gray.

Fig 19. Simulação Funcional do incrementador de código Gray - Ver também Código Gray;

- Aula de exercícios:

- 5.7 - Peso de Hamming

- 5.8 - Ordenador binário

- 5.15 - Multiplicador Unsigned

- Aula 19 (16 Out)

- Avaliação A1 - UN2, UN3, UN4

1.5 Unidade 5

- Aula 20 (17 Out)

- Realização da SAD - Avaliação Docente pelos Discentes

- Correção da Avaliação A1. Conceitos na Avaliação

- Código Sequencial.

- Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial

- Diferenças entre os objetos SIGNAL e VARIABLE

- Tipos de elementos de memória: Latch x Flip-flop

- Latch D

- Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono

- Seção de código sequencial PROCESS: lista de sensibilidade

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

- Instrução IF

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

- Exemplos: DFFs with Reset and Clear (Variação Ex 6.1), Basic Counter (Ex. 6.2), Shift Register (Ex. 6.3)

- Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT.

- Ver pag. 161 a 160 de [2]

- Aula 21 (23 Out)

- Uso do Modelsim para simulação.

- Contador Básico 0-N (baseado no Ex.6.2)

- Registrador de deslocamento (Ex.6.3)

- Ver também

- Seguindo o tutorial da ALTERA para o MODELSIM, para utilizar o básico do MODELSIM.

- Pedroni VHDL 2ed Tutorial of ModelSim 10.1d

- ModelSim Video Tutorial - Kirk Weedman

- Documentação do ModelSim, para conhecer mais a fundo o MODELSIM.

- Aula 22 (25 Out)

- Aula substituída pela "Apresentação trabalhos técnicos científicos Telecomunicações" na Semana Nacional de Ciência e Tecnologia (SNCT), conforme solicitação da coordenação do curso.

1.5.1 ATUAL

- Aula 23 (26 abr)

- Código Sequencial.

- Instrução WAIT: WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II).

- Algumas instruções de WAIT serão utilizadas na criação de TestBench em VHDL para a simulação com o MODELSIM.

- Instruções do tipo LOOP: LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT

- LOOP incondicional:

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- FOR-LOOP:

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- WHILE-LOOP:

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com EXIT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

- LOOP com NEXT:

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

- Exemplos: Carry-Ripple Adder (FOR-LOOP) (Ex 6.4),

- Ver pag. 161 a 164 de [2]

2 Avaliações

- Avaliação A1 - Unidade 2 a 4 (XX/XX/2017) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2017) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD, e as tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2017) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

- Autoinscrição na Plataforma Moodle de DLP29006 (engtelecom) - ATENÇÃO! MUDEI O AMBIENTE PARA PRESERVAR O ACESSO DOS ALUNOS ANTERIORES.

AE0 - Resumo estendido de Artigo (Entrega e Prazo ver Moodle)

- Ler e fazer um resumo estendido do artigo de 1 a 2 páginas Dispositivos Lógicos Programáveis de Kamila Rose da Silva, IFSC.

- Para a geração de documentação/relatórios técnicos/artigos, está disponibilizada a Plataforma Sharelatex. Utilize preferencialmente o modelo de artigo no padrão ABNT em 1 coluna.

- A entrega do resumo deverá ser feita na Plataforma Moodle de DLP29006, dentro do prazo indicado.

AE1 - Uso de código concorrente - ALU modificada (Entrega e Prazo ver Moodle)

- Implemente em VHDL uma Unidade de Lógica e Aritmética que tem como entrada os sinais A e B e que execute as seguintes instruções lógicas e aritméticas conforme o opcode de entrada:

- Unidade Lógica

Instrução

Operação

opcode

GRUPOS

Complemento de A

Y = not A

0000

1, 2, 3

Complemento de B

Y = not B

0001

4, 5, 6

And

Y = A nand B

0010

1, 3

Nand

Y = A and B

0011

2, 4

Or

Y = A nor B

0100

5, 6

Nor

Y = A or B

0101

1, 4

Xor

Y = A xor B

0110

2, 5

Xnor

Y = A xnor B

0111

3, 6

- Unidade Aritmética

- (onde os valores de A e B podem ser positivos ou negativos)

Instrução

Operação

opcode

GRUPOS

Transfere A

Y = A

1000

1, 2, 3, 4, 5, 6

Transfere B

Y = B

1001

1, 2, 3, 4, 5, 6

complemento-2 de A

Y = -A

1010

1, 2, 3

complemento-2 de B

Y = -B

1010

4, 5, 6

Incrementa A

Y = A + 1

1011

1, 4

Decrementa A

Y = A - 1

1011

2, 5

Incrementa B

Y = B + 1

1100

3, 6

Soma A e B

Y = A + B

1101

1, 2

Subtrai B de A

Y = A - B

1110

3, 4

Subtrai A de B

Y = B - A

1110

5, 6

Dobra o valor A

Y = A * 2

1111

1, 2, 3

Dobra o valor B

Y = B * 2

1111

4, 5, 6

- A ENTITY deverá ter a seguinte interface:

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

A, B: IN STD_LOGIC_VECTOR (N-1 DOWNTO 0);

OPCODE: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

ERRO: OUT STD_LOGIC;

Y: OUT STD_LOGIC_VECTOR (N-1 DOWNTO 0));

END ENTITY;

- Verifique qual é o seu grupo, você apenas precisa implementar e simular as funções indicadas para o ele.

- Proponha uma ARCHITECTURE que implemente a ALU (Dica: utilize internamente o tipo de dado tipo integer ou do tipo "SIGNED").

- Se na operação realizada o resultado em Y não estiver correto, a saída ERRO deve ser setada.

- Anote o número de Elementos Lógicos (ou ALUTs) utilizados [Compilation Report > Flow Summary].

- Verifique o código RTL gerado [Tools > Netlist Viewers > RTL Viewer]

- Faça a simulação funcional no QSIM usando os valores mínimos e máximos e outros pares de valores representáveis e verifique se o resultado das operações está correto. Teste cada instrução (opcode) em separado. Analise os resultados obtidos para entradas com 4 bits e verifique os casos em que há ERRO.

- Escreva um relatório de no máximo 15 páginas contendo: título, identificação, introdução, o desenvolvimento da atividade e resultados, conclusão. O relatório deve conter as simulações funcionais feitas e a análise dos resultados obtidos. Também é fundamental relate o número de elementos lógicos necessários, o tipo de FPGA utilizado, e o máximo tempo de propagação deste circuito.

- Salve a imagem do circuito RTL e envie com arquivo .PNG.

- A entrega do relatório em .PDF e do arquivo .QAR e .PNG deverá ser feita na Plataforma Moodle de DLP29006, dentro do prazo indicado.

2.1 ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

EL0 - Resolução dos exercícios do Cap 2

- Resolva os exercícios do capítulo 2 (1, 2, 3) pag. 28 a 30

- Exercise 2.1

- Multiplexer:

- Complete o código VHDL abaixo para que ele seja correspondente a um multiplexador que selecione a entrada A quando sel ="01", B quando sel ="10", coloque "0...0" na saída quando sel ="00" e mantenha a saída em alta impedância "Z...Z" quando sel="11".

- Compile o código e em seguida faça a simulação, para verificar se o circuito funciona conforme

especificado.

- Anote as mensagens de warning do compilador.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

EL1 - Uso de tipos de dados e operadores

- Implementar em VHDL um circuito que efetue a operação , utilizando portas do tipo STD_LOGIC_VECTOR para valores de entrada e com sinal e ocupando 4 bits, utilize na saída 8 bits.

- Repita o circuito com as mesmas características, utilizando no entanto portas do tipo INTEGER com range de -8 a 7 nas entradas e range de -128 a 127 na saída.

- Repita o circuito com as mesmas características, utilizando no entanto portas do tipo INTEGER com range de -8 a 7 nas entradas e range de -256 a 255 na saída.

- Em todos os casos faça a simulação funcional do circuito. Teste o circuito no minimo com , e . Note que para valores maiores de entrada e pode ocorrer overflow devido a limitação do número de bits da saída.

- Determine o número de elementos lógicos e pinos e verifique o código RTL obtido. Compare com os colegas.

EL2 - Resolução dos exercícios do Cap 3

- Resolva os exercícios do capítulo 3 (1, 2, 9, 11, 12, 13, 14-17, 18, 20, 22, 23-30) pag. 81 a 89

AR2- Conversor de Binário para BCD

- Considere um número decimal entre 000 e 999. Usando operadores predefinidos, obtenha na saída os dígitos decimais separados.

- Escreva o código VHDL e analise o número de elementos lógicos necessários.

- Faça a simulação funcional do circuito.

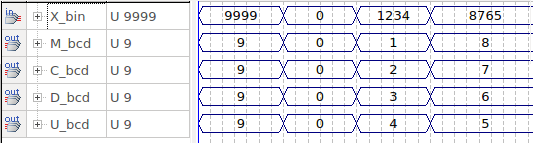

Fig. 20 - Simulação da conversão de binário para BCD

- Compare sua implementação com os outros estudantes e analise as diferenças, observe o código RTL, o número de elementos lógicos e também o tempo de propagação.

- Para separar os dígitos decimais do número de entrada pense nos operadores de "+", "-", "*", "/", "REM" e "MOD", shift.

- Para facilitar os testes e a troca de informações entre as equipes, a ENTITY deverá ter o seguinte formato:

entity bin2bcd is

port (

X_bin : in std_logic_vector(13 downto 0); -- 000 a 999

C_bcd : out std_logic_vector(3 downto 0); -- Centena

D_bcd : out std_logic_vector(3 downto 0); -- Dezena

U_bcd : out std_logic_vector(3 downto 0)); -- Unidade

end entity;

architecture example of bin2bcd is

--declaração de sinais auxiliares

begin

--descrição do hardware

end architecture;

- Note que com X_bin 10 bits é possível representar números sem sinal entre 0 e . No entanto, os testes devem ser limitados a números entre 000 e 999, pois não há especificação para valores maiores que 999.

- Existe um algoritmo Double Dabble que possibilita fazer essa conversão com menos hardware.

- Dica para converter de INTEGER para STD_LOGIC_VECTOR de 4 bits.

M_bcd <= std_logic_vector(to_unsigned(M,4));

EL4 - Resolução dos exercícios do Cap 4

- Resolva os exercícios do capítulo 4 (4-8, 9, 10-11, 13, 15-16, 17 ) pag. 115 a 120

EL5 - Resolução dos exercícios do Cap 5

- Resolva os exercícios do capítulo 5 (1, 2, 3, 4, 6, 7, 8-9, 10-11, 14-16, 17-18, 19 ) pag. 144 a 150

AR3 - Unidade somadora e subtratora

- Implementar em VHDL uma unidade de processamento que efetue a operação de soma ou subtração considerando valores SIGNED e UNSIGNED. As características do circuito são:

- As portas de entrada e saída são todas do tipo STD_LOGIC(_VECTOR)

- As entradas e devem ter N bits, e a saída N+1 bits.

- O circuito tem uma entrada , a qual define se os valores das entradas e saídas devem ser considerados UNSIGNED ou SIGNED. indica UNSIGNED , e indica SIGNED.

- O circuito tem uma entrada , a qual define se a operação a ser feita deve ser uma soma ou uma subtração. indica soma, e indica subtração.

- O circuito tem além da saída , uma saída adicional que indica quando o resultado é zero.

- Faça a simulação funcional do circuito, testando o circuito usando no mínimo com

- , - SOMA UNSIGNED

- , - SUBTRAÇÂO UNSIGNED

- , - SOMA SIGNED

- , - SUBTRAÇÂO SIGNED

- , - SOMA SIGNED

- ; - SUBTRAÇÂO SIGNED

onde são respectivamente valores numéricos positivos e negativos.

- Note que alguns valores de entrada ainda pode ocorrer erro, mesmo tendo um bit a mais na saída. Em que situação isso pode ocorrer? Mostre uma situação em que isso ocorre na simulação.

3 Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335