Mudanças entre as edições de "DLP29006-Engtelecom(2019-1) - Prof. Marcos Moecke"

| Linha 1 237: | Linha 1 237: | ||

:* Remodelar o projeto do contador 0 a 9 com saída SSD para usar um componente para o contador e outro para o conversor de BCD para SSD. | :* Remodelar o projeto do contador 0 a 9 com saída SSD para usar um componente para o contador e outro para o conversor de BCD para SSD. | ||

| − | |||

:* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

Assim a entity Timer00_99 | Assim a entity Timer00_99 | ||

| Linha 1 289: | Linha 1 288: | ||

::*Exemplo: Detector de Paridade Ex. 8.3 | ::*Exemplo: Detector de Paridade Ex. 8.3 | ||

:* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ; Aula 32 e 33 (13 e 16 mai): | ||

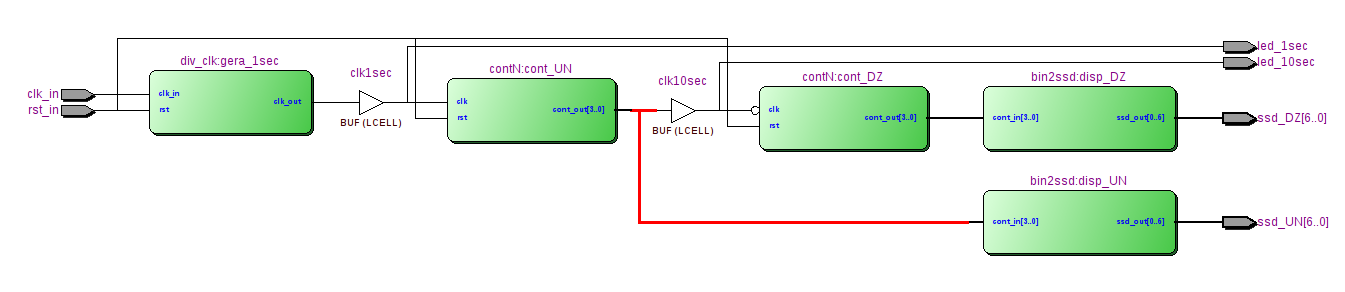

| + | *Implementar o timer00a99 em projeto hierarquico | ||

| + | <center> | ||

| + | [[Arquivo:timer00a99RTL.png]] | ||

| + | </center> | ||

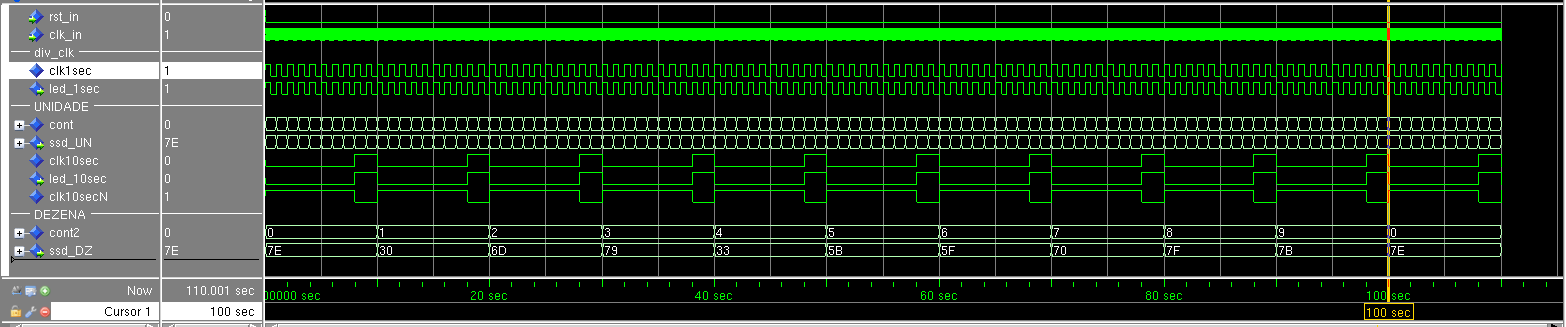

| + | *Fazer a simulação de 110 segundos usando o MODELSIM. | ||

| + | :*Use um clock compativel com o divisor utilizado no div_clock | ||

| + | <center> | ||

| + | [[Arquivo:timer00a99SIM.png]] | ||

| + | </center> | ||

| + | *Testar o timer00a99 no kit DE2-115 | ||

| + | :* Usar uma chave PUSH-BOTTON como reset. | ||

| + | :* Usar o clk de 50 MHz da placa | ||

| + | :* Usar dois displays SSD para mostrar a contagem de 00 a 99 segundos | ||

| + | :* Usar um led para mostrar o segundo e outro para mostrar a dezena de segundos. | ||

| + | *Verificar se o circuito funciona como esperado. | ||

| + | :*Anote os problemas ocorridos e as soluções adotadas. | ||

| + | |||

| + | |||

| + | |||

<!-- | <!-- | ||

Edição das 17h48min de 13 de maio de 2019

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

-- Isso eh uma linha de comentario y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b

caracter: 'A' 'x' '#' (com aspas simples) string de caracteres: "IFSC" "teste" "teste123"

bit único: '0' '1' 'Z' (com aspas simples) vetor de bits: "0110" "101001Z" (com aspas duplas) vetor de 1 bit: "0" "1" (com aspas duplas) inteiros: 5 1101 1102 (sem aspas)

0 -> '0' 7 -> "0111" ou b"0111" ou B"0111" 1023 -> "001111111111" ou b"1111111111" ou B"1111111111"

44 -> 5*8^1 + 4*8^0 -> O"54" ou o"54" 1023 -> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777#

1023 -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF#

1023 -> 1023 ou 1_023 1000 -> 1000 ou 1_000 ou 1E3

5#320# (3*5^2 + 2*5^1 + 0*5^0) -> 85 3#201#E4 (2*3^2+0*3^1+1*3^0)*3^4 -> 1539

package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

Ver pag. 60 a 73 de [2]

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY operadores IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

div: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

);

END ENTITY;

ARCHITECTURE type_conv_arch OF operadores IS

BEGIN

-- Inserir o código e definir o tamanho das saidas.

END ARCHITECTURE;

OBS: uso da função resize(object,size) --============================================================================

-- RESIZE Functions

--============================================================================

-- Id: R.1

function RESIZE (ARG: SIGNED; NEW_SIZE: NATURAL) return SIGNED;

-- Result subtype: SIGNED(NEW_SIZE-1 downto 0)

-- Result: Resizes the SIGNED vector ARG to the specified size.

-- To create a larger vector, the new [leftmost] bit positions

-- are filled with the sign bit (ARG'LEFT). When truncating,

-- the sign bit is retained along with the rightmost part.

-- Id: R.2

function RESIZE (ARG: UNSIGNED; NEW_SIZE: NATURAL) return UNSIGNED;

-- Result subtype: UNSIGNED(NEW_SIZE-1 downto 0)

-- Result: Resizes the SIGNED vector ARG to the specified size.

-- To create a larger vector, the new [leftmost] bit positions

-- are filled with '0'. When truncating, the leftmost bits

-- are dropped.

Atributos em VHDL.

Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em:

type fruit is (apple, orange, pear, mango);

attribute enum_encoding : string;

attribute enum_encoding of fruit : type is "11 01 10 00";

entity foo is

port (sel : in std_logic;

data : in std_logic_vector(3 downto 0);

o : out std_logic);

end foo;

architecture rtl of foo is

attribute chip_pin : string;

attribute chip_pin of sel : signal is "C4";

attribute chip_pin of data : signal is "D1, D2, D3, D4";

begin

-- Specify additional code

end architecture;

O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. .

signal a,b,c : std_logic;

attribute keep: boolean;

attribute keep of a,b,c: signal is true;

signal a,b,c : std_logic;

attribute preserve: boolean;

attribute preserve of a,b,c: signal is true;

signal reg1: std_logic;

attribute noprune: boolean;

attribute noprune of reg1: signal is true;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

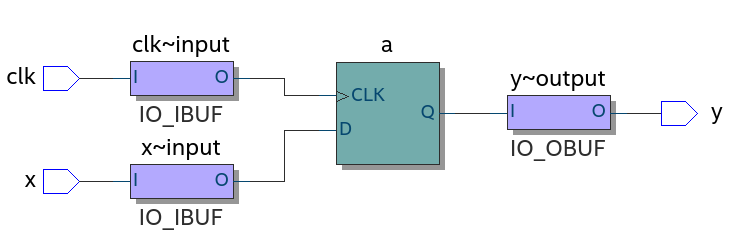

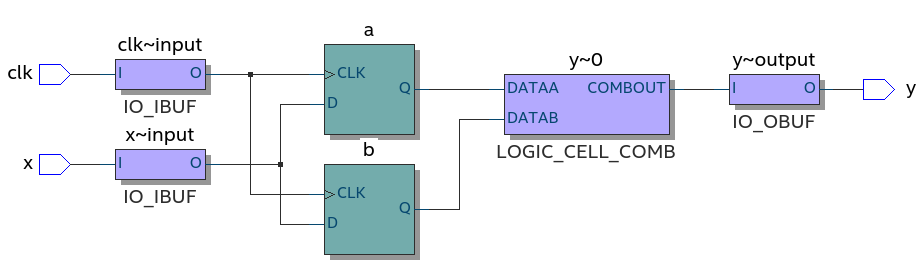

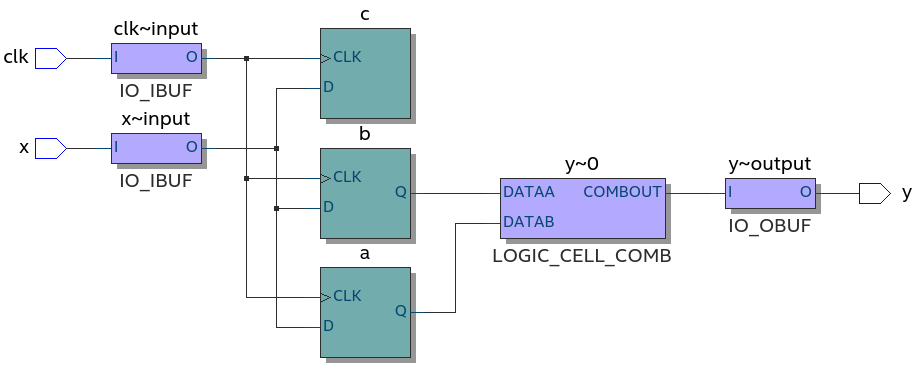

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

attribute attribute_name: attribute_type;

attribute attribute_name of entity_tag [signature]: entity_class is value;

Exemplo:

Uso da instrução ALIAS.

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

---------------------

-- FILE my_pkg.vhd --

---------------------

library ieee;

use ieee.std_logic_1164.all;

package my_pkg is

type a_slv is array(natural range <>) of std_logic_vector (3 downto 0);

end package;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

library ieee work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.my_pkg.all;

entity vector_adder is

generic (N : natural := 4);

port (

a : in a_slv (0 to N-1);

soma : out std_logic_vector (3 downto 0));

end entity;

-- Versão que realiza a soma diretamente, mas que precisa modificar o código de acordo com o número de entradas.

architecture ifsc_v1 of vector_adder is

signal soma_sig : signed(3 downto 0);

begin

-- soma_sig <= signed(a(0)) + signed(a(1))

-- soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2))

soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2)) + signed(a(3));

soma <= std_logic_vector(soma_sig);

end architecture;

-- Versão que realiza a soma usando um FOR GENERATE

architecture ifsc_v2 of vector_adder is

begin

end architecture;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

configuration ifsc_cfg of vector_adder is

-- for ifsc_v1 end for;

for ifsc_v2 end for;

end configuration;

entity bin2gray is

generic (N : natural := 4 )

port

(

b : in std_logic_vector(____)

g : out std_logic_vector(____)

)

end entity

architecture ifsc of ____ is

begin

end architecture

entity gray2bin is

generic (N : natural := 4 )

port

(

g : in std_logic_vector(____)

b : out std_logic_vector(____)

)

end entity

architecture ifsc of ____ is

begin

end architecture

function "+" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Adds two UNSIGNED vectors that may be of different lengths.

function "-" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Subtracts two UNSIGNED vectors that may be of different lengths.

function "*" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED((L'LENGTH+R'LENGTH-1) downto 0).

-- Result: Performs the multiplication operation on two UNSIGNED vectors

-- that may possibly be of different lengths.

function "/" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(L'LENGTH-1 downto 0)

-- Result: Divides an UNSIGNED vector, L, by another UNSIGNED vector, R.

-- NOTE: If second argument is zero for "/" operator, a severity level of ERROR is issued.

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

Avaliação A1 - UN2, UN3, UN4

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

|

| Unidade 6 - Projeto a nível de Sistema |

|---|

|

Unidade 6 - Projeto a nível de Sistema

Assim a entity Timer00_99 ENTITY timer00_99seg

GENERIC (D : INTEGER;

fclock : INTEGER;

U : INTEGER);

PORT (clk50MHz : IN STD_LOGIC;

RST : IN STD_LOGIC;

clk1seg : OUT STD_LOGIC;

SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6);

SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6));

END ENTITY;

Será declarada como um COMPONENT COMPONENT timer00_99seg

GENERIC (D : INTEGER;

fclock : INTEGER;

U : INTEGER);

PORT (clk50MHz : IN STD_LOGIC;

RST : IN STD_LOGIC;

clk1seg : OUT STD_LOGIC;

SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6);

SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6));

END COMPONENT;

comp1 : timer00_99seg

GENERIC MAP (2, 10, 3)

PORT MAP (clk50MHz,RST, clk1seg, SSD_Dseg, SSD_Useg);

comp1 : timer00_99seg

GENERIC MAP ( D => 2, U => 3,

fclock => 10,

PORT MAP ( clk50MHz => clk50MHz,

RST => RST,

clk1seg => clk1seg,

SSD_Dseg => SSD_Dseg,

SSD_Useg => SSD_Useg);

|

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 7 - Maquinas de Estado Finitas

|

| Unidade 8 - Testbench |

|---|

Unidade 8 - Testbench

|

| Unidade 9 - Projeto Final |

|---|

Unidade 9 - Projeto Final

|

Avaliações

Atividade Relâmpago (AR)

As atividades relâmpago são atividades avaliativas opcionais que darão BôNUS adicionais ao aluno na próxima avaliação. Elas normalmente consistem de soluções simples para algum problema ou sistema. Elas são enunciadas na aula, e o prazo e a entrega serão definidos no Moodle. Não são aceitas entregas tardias, e apenas 2 alunos podem receber o bonus. A pontuação das atividades é informada a cada atividade.

Avaliação A1

- Conteúdo avaliado serão as unidades 2 a 4 (cap 1 - 5)

- Data da avaliação (25/04/2019) - Local: LabSiDi.

Avaliação A2

- Conteúdo avaliado serão as unidades 5 a 7 (Cap 6 a 9)

- Data da avaliação () - Local: LabSiDi.

Recuperação R12

- Esta avaliação somente será realizada se necessária, e deverá ser feita na última semana letiva do semestre

- Conteúdo avaliado será as unidades 2 a 7

- Data da avaliação () - Local: LabSiDi.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

Projeto Final (PF)

- O projeto final é uma atividade de avaliação desenvolvida em equipe, e consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a no mínimo 45% do peso no conceito final. São avaliados no projeto final os quesitos: 1) Sistema desenvolvido (projeto, simulação e realização, demostração do harware); 2) Relatório com a documentação completa do projeto; 3) A avaliação individual do aluno durante o desenvolvimento do projeto e/ou entrevista (avaliação oral).

Atividades Extraclasse (AE)

- Entrega dos Atividades Extraclasse ao longo do semestre AE(0) a AE(N). A entrega, detalhes e prazos serão indicados na plataforma Moodle.

Estudos livres sem entrega de documentação (EL)

- Os estudos livres são fortemente recomendados aos alunos como forma de melhor compreender o assunto estudado em cada unidade. Nas listas de exemplos e exercícios, os essenciais estão destacados em negrito. Não há prazos nem entregas desses estudos no Moodle, mas pede-se que os alunos realizem esses estudos e tirem suas dúvidas nas aulas destinadas a resolução de exercícios, ou nos minutos iniciais das aulas.

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL3 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL4 - Resolução dos exercícios do Cap 5 |

|---|

|

Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335