Mudanças entre as edições de "DIG222802 2017 2 AULA14"

(Criou página com '=Apresentação= Olá Alunos, Nas semanas que passaram realizamos os laboratórios de Modelsim/Quartus. Hoje vamos mostrar algum conceitos sobre FPGA, o que são estes disposit...') |

|||

| Linha 319: | Linha 319: | ||

=Conclusão= | =Conclusão= | ||

| − | A adoção da tecnologia FPGA vem aumentando assim como o nível das ferramentas que fornecem benefícios para engenheiros e cientistas de todas as áreas. Para mais informações sobre como o FPGA pode ser usado em variadas | + | A adoção da tecnologia FPGA vem aumentando ano após ano, assim como o nível das ferramentas que fornecem benefícios para engenheiros e cientistas de todas as áreas. Para mais informações sobre como o FPGA pode ser usado em variadas aplicações na indústria, pesquise em informações adicionais. |

=Referências= | =Referências= | ||

Edição das 12h19min de 27 de novembro de 2017

Apresentação

Olá Alunos,

Nas semanas que passaram realizamos os laboratórios de Modelsim/Quartus. Hoje vamos mostrar algum conceitos sobre FPGA, o que são estes dispositivos integrados, suas principais características e como funcionam. Desta forma, finalizamos nossas atividades de aulas teóricas de novos conteúdos.

Preparem-se para as últimas avaliações!

Prof. Douglas A.

Objetivo

- Apresentar o FPGA.

FPGA

- O artigo que vocês verão a seguir, foi retirado na íntegra do site da National Instruments e que trata da tecnologia FPGA (Field-Programmable Gate Array).

Desde sua invenção em 1984 pela Xilinx, os FPGAs passaram de um simples chip de lógica personalizada até realmente substituir circuitos integrados de aplicações específicas (application-specific integrated circuits – ASIC) personalizadas para processamento de sinais e aplicações de controle. Por que essa tecnologia foi tão bem sucedida? Este artigo fornece uma introdução ao FPGA e destaca alguns dos benefícios que fazem FPGAs únicos.

O que é um FPGA?

FPGAs são chips de silício reprogramáveis que usa blocos lógicos programáveis pré-construídos que tem recursos de roteamento, você pode configurar esses chips para implementar funcionalidades personalizadas de hardware, sem nunca ter que pegar em uma placa de montagem ou ferro de solda. Você desenvolve tarefas de computação digital em software e as compila em um arquivo de configuração ou bitstream que contém informações sobre como os componentes devem ser ligados entre si. Além disso, os FPGAs são totalmente reconfiguráveis e imediatamente assumem uma nova "personalidade" quando você recompila uma nova configuração de circuito. No passado, a tecnologia FPGA só estava disponível para engenheiros com uma profunda compreensão do projeto de hardware digital. O surgimento de ferramentas de projeto de alto nível, no entanto, está mudando as regras da programação FPGA, com as novas tecnologias que convertem diagramas de blocos gráficos ou mesmo código em C em circuitos de hardware digital.

A adoção de chips FPGA em todos os setores é dirigida pelo fato dos FPGAs combinarem as melhores partes do ASIC a sistemas baseados em processador. Os FPGAs oferecem confiabilidade e velocidade na temporização por hardware, mas não exigem grandes volumes para justificar o grande gasto inicial de um projeto ASIC personalizado. O silício reprogramável também tem a mesma flexibilidade de um software rodando em um sistema baseado em processador, mas não é limitado pelo número de núcleos de processamento disponível. Ao contrário de processadores, os FPGAs são verdadeiramente paralelos por natureza, de modo que diferentes operações de processamento não têm que cosumir os mesmos recursos. Cada tarefa independente de processamento é atribuído a uma seção dedicada do chip, e pode funcionar de forma autônoma, sem qualquer influência de outros blocos lógicos. Como resultado, o desempenho de uma parte da aplicação não é afetada quando um processamento adicional é inserido.

Benefícios da tecnologia FPGA

Os benefícios da tecnologia FPGA podem, basicamente, ser divididos em cinco grupos: Desempenho, Tempo de mercado, Custo, Confiabilidade e Manutenção a longo prazo.

Desempenho

Aproveitando-se do paralelismo do hardware, os FPGAs excedem o poder dos processadores digitais de sinais (digital signal processors – DSPs) quebrando o paradigma de execução sequencial e realizando mais por um ciclo de clock. A BDTI, uma notável empresa de realização de benchmarks, lançou benchmarks mostrando como os FPGAs podem oferecer muitas vezes o poder de processamento por dólar de uma solução DSP em algumas aplicações. Controlar entradas e saídas (E/S) no nível do hardware fornece tempos de resposta muito mais rápidos devido à funcionalidades especializadas para aproximar aos requisitos da aplicação.

Tempo de mercado

A tecnologia FPGA oferece flexibilidade e rapidez na capacidade de prototipagem em face as crescentes preocupações sobre o tempo de mercado. Você pode testar uma idéia ou conceito e verificar no hardware sem passar pelo longo processo de fabricação de um projeto personalizado com ASIC. Você pode então implementar mudanças incrementais e interagir com o projeto de FPGA em poucas horas em vez de semanas. Os Hardware de mercado (Commercial off-the-shelf - COTS) também estão disponíveis com diferentes tipos de E/S já conectados a um chip FPGA. A crescente disponibilidade de ferramentas de software de alto nível, diminui a curva de aprendizado com as camadas de abstração e, frequentemente, incluem valiosos núcleos IP (funções pré-construidas) para o controle avançado e processamento de sinais.

Custo

A engenharia não recorrente (nonrecurring engineering – NRE) de despesas em projeto personalizados com ASIC excede em muito comparada às soluções de hardware baseado em FPGA. O grande investimento inicial em ASICs é fácil de justificar para os envios de milhares de chips OEMs por ano, mas muitos usuários finais precisam de funcionalidades personalizadas de hardware para as dezenas a centenas de sistemas em desenvolvimento. A própria natureza do silício programável significa que não há nenhum custo para a fabricação ou um longo prazo para a montagem. Como os requisitos do sistema mudam frequentemente ao longo do tempo, o custo de fazer mudanças incrementais para projetos FPGA é insignificante quando comparado com a grande despesa de reprogramar um ASIC.

Confiabilidade

Enquanto as ferramentas de software fornecem o ambiente de programação, os circuitos FPGA são fáceis de implementar para a execução do programa. Sistemas baseados em processador geralmente envolvem várias camadas de abstração para ajudar a agendar tarefas e compartilhar recursos entre vários processos. A camada de driver controla os recursos de hardware e o sistema operacional gerencia a memória e a largura de banda do processador. Para qualquer núcleo do processador, apenas uma instrução pode executar por vez, e os sistemas baseados em processadores estão continuamente em risco devido a tarefas de tempo crítico que antecipam umas as outras. Os FPGAs, que não utilizam sistemas operacionais, minimizam as preocupações com a confiabilidade da execução paralela e ao hardware determinístico dedicado a cada tarefa.

Manutenção a longo prazo

Como mencionado anteriormente, os chips FPGA são atualizáveis e não exigem tempo e dinheiro para reprojetar como no ASIC. Protocolos de comunicação digital, por exemplo, têm especificações que podem mudar ao longo do tempo, e interfaces baseadas em ASIC podem causar adiantamento de desafios de compatibilidade e manutenção. Por serem reconfiguráveis, os chips FPGA são capazes de acompanhar as modificações futuras que possam ser necessárias. Conforme um produto ou sistema amadurece, você pode fazer melhorias funcionais sem gastar tempo reprojetando hardware ou modificando o layout da placa.

Escolhendo um FPGA

Ao analisar as especificações de um chip FPGA, note que elas são divididas em blocos lógicos configuráveis, células lógicas, lógica de função fixa como multiplicadores e recursos de memória como bloco de RAM integrada. Há muitos outros componentes do chip FPGA, mas estes são normalmente os mais importantes para selecionar e comparar FPGAs para uma determinada aplicação.

| Virtex-II

1000 |

Virtex-II

3000 |

Spartan-3

1000 |

Spartan-3

2000 |

Virtex-5

LX30 |

Virtex-5

LX50 |

Virtex-5

LX85 |

Virtex-5

LX110 | |

|---|---|---|---|---|---|---|---|---|

| Portas | 1 milhão | 3 milhões | 1 milhão | 2 milhões | ----- | ----- | ----- | ----- |

| Flip-Flops | 10,24 | 28,672 | 15,36 | 40,96 | 19,2 | 28,8 | 51,84 | 69,12 |

| LUTs | 10,24 | 28,672 | 15,36 | 40,96 | 19,2 | 28,8 | 51,84 | 69,12 |

| Multiplicadores | 40 | 96 | 24 | 40 | 32 | 48 | 48 | 64 |

| Bloco de RAM (kb) | 720 | 1,728 | 432 | 720 | 1,152 | 1,728 | 3,456 | 4,608 |

A Tabela 1 apresenta as especificações dos recursos utilizados para comparar chips FPGA Xilinx dentro de várias famílias. O número de portas lógicas tem sido tradicionalmente uma forma de comparar o tamanho dos chips FPGA e a tecnologia ASIC, mas não acaba descrevendo realmente o número de componentes individuais dentro de um FPGA. Esta é uma das razões para que a Xilinx não especifique o número de portas do sistema para a nova família Virtex-5.

Preparando para gravar o circuito lógico no FPGA

- Exemplo de uma aplicação

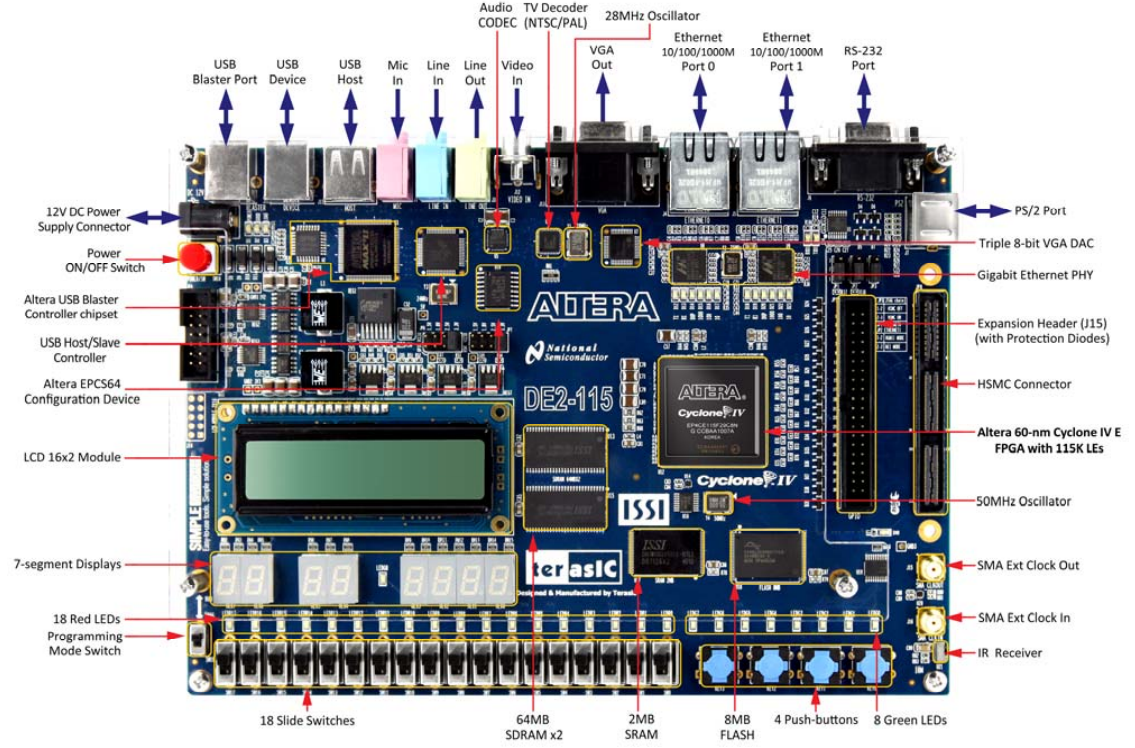

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone II] e selecione EP2C35F672C6.

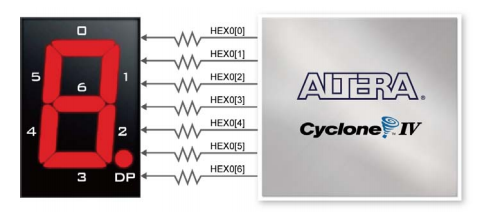

- Utilize o display HEX0 do kit para mostrar a contagem:

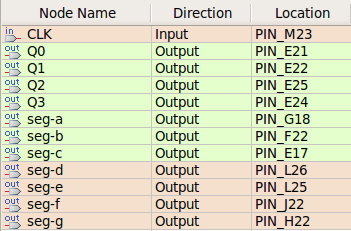

- Utilize os leds de LED0 a LED3 (verdes) para mostrar a contagem em binário.

- Utilize a chave KEY0 para gerar o sinal de CLK.

- Atribua os pinos conforme a Pinagem: pinagem do kit DE2.

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.

Programando o FPGA através da USB-Blaster

Para utilizar o Software Quartus II para programar o FPGA, siga as seguintes etapas:

- Conecte o kit através do cabo USB fornecido junto com o mesmo. Uma extremidade do cabo deve ser conectada a uma porta do computador e a outro ao conecter USB-Blaster do kit (verifique o manual do kit para identificar essa porta). No caso da DE2-115 conecte também a fonte de alimentação.

- Ligue o kit posicionando a chave LIGA em [ON]#Inicie o software Quartus II.

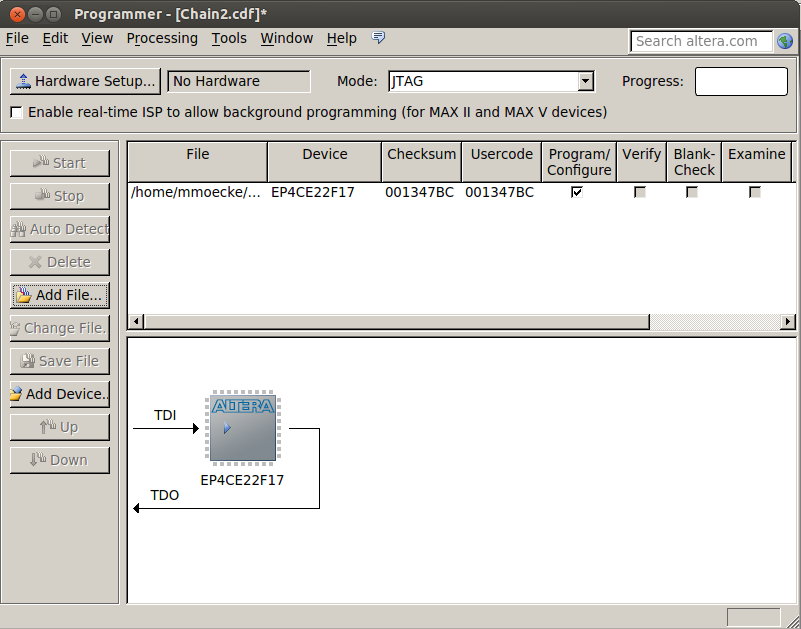

- Escolha {Tools > Programmer} (ver Fig.1).

- Caso a coluna File esteja vazia, é necessário encontrar o arquivo .sof do projeto:

- Clique em Add File... (menu lateral esquerdo), procure pelo arquivo nome_do_projeto.sof. Normalmente ele se encontra na pasta output_files, mas as vezes ele está na pasta do próprio projeto ou alguma outra.

- Clique em [Hardware Setup]. A guia de configurações de hardware da caixa de diálogo de configuração de hardware é exibida (ver Fig.2).

- A partir do menu drop-down, selecione a USB-Blaster disponível [USB-Blaster N-M], N e M indicam a porta USB a qual o kit foi conectado.

- Clique em [Close] para fechar a caixa de diálogo de configuração de Hardware.

- Na lista Modo, selecione o modo [JTAG].

- Mude a chave RUN/PROG para a posição RUN.

- Para programar, é necessário apenas selecionar {Processing > Star}. Após alguns segundos, o cursor Progress: indicará [100% Successful].

- OBS: É bem provável que ao abrir o programador, as etapas 5 a 8 já estejam configuradas corretamente.

- FONTE: Setting up Programming Hardware in Quartus II Software,ALTERA,2013

Programando DE2

http://labdegaragem.com/profiles/blogs/tutorial-introducao-a-fpga-101

Programando_o_FPGA_através_da_USB-Blaster

Instalando JTAG - USB-Blaster

Configuração_da_USB_para_programação_do_FPGA_via_JTAG

Exemplo

O exemplo abaixo serve para montar um cronometro de segundos e é dividido em três partes:

| cronometro.vhd |

|---|

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY cronometro IS

PORT( clock : IN STD_LOGIC;

disp_uni : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

disp_dez : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END cronometro;

ARCHITECTURE teste OF cronometro IS

SIGNAL clock1Hz : STD_LOGIC := '0';

SIGNAL valor : INTEGER RANGE 0 TO 59 := 0;

SIGNAL BCD_unidade : INTEGER RANGE 0 TO 9 := 0;

SIGNAL BCD_dezena : INTEGER RANGE 0 TO 9 := 0;

COMPONENT divisor_de_clock

GENERIC( freq_entrada : INTEGER := 27000000;

freq_saida : INTEGER := 1

);

PORT( clock27MHz : IN STD_LOGIC;

clock1Hz : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT BCD_7seg_AC

PORT( BCD : IN INTEGER;

segmentos : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) --abcdefg

);

END COMPONENT;

BEGIN

divisor1 : divisor_de_clock

GENERIC MAP(27000000,1)

PORT MAP(clock,clock1Hz);

PROCESS(clock1Hz)

BEGIN

IF RISING_EDGE(clock1Hz) THEN

IF valor = 59 THEN

valor <= 0;

ELSE

valor <= valor + 1;

END IF;

END IF;

END PROCESS;

BCD_unidade <= valor MOD 10;

BCD_dezena <= valor / 10;

DISP1 : BCD_7seg_AC

PORT MAP(BCD_unidade,disp_uni);

DISP2 : BCD_7seg_AC

PORT MAP(BCD_dezena,disp_dez);

END teste;

|

| divisor_de_clock.vhd |

|---|

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY divisor_de_clock IS

GENERIC( freq_entrada : INTEGER := 27000000; -- Contador de Pulsos de 27MHz

freq_saida : INTEGER := 1

);

PORT( clock27MHz : IN STD_LOGIC;

clock1Hz : OUT STD_LOGIC

);

END divisor_de_clock;

ARCHITECTURE teste OF divisor_de_clock IS

CONSTANT maximo : INTEGER := (freq_entrada / (freq_saida * 2)) - 1;

SIGNAL contagem : INTEGER RANGE 0 TO maximo;

SIGNAL aux : STD_LOGIC := '0';

BEGIN

PROCESS(clock27MHz)

BEGIN

IF RISING_EDGE(clock27MHz) THEN

IF contagem = maximo THEN

contagem <= 0;

aux <= NOT aux;

ELSE

contagem <= contagem + 1;

END IF;

END IF;

END PROCESS;

clock1Hz <= aux;

END teste;

|

| BCD_7seg_AC |

|---|

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY BCD_7seg_AC IS

PORT( BCD : IN INTEGER;

segmentos : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) --abcdefg

);

END BCD_7seg_AC;

ARCHITECTURE teste OF BCD_7seg_AC IS

BEGIN

WITH BCD SELECT

segmentos <= "0000001" WHEN 0,

"1001111" WHEN 1,

"0010010" WHEN 2,

"0000110" WHEN 3,

"1001100" WHEN 4,

"0100100" WHEN 5,

"1100000" WHEN 6,

"0001111" WHEN 7,

"0000000" WHEN 8,

"0001100" WHEN 9,

"1111111" WHEN OTHERS;

END teste;

|

Conclusão

A adoção da tecnologia FPGA vem aumentando ano após ano, assim como o nível das ferramentas que fornecem benefícios para engenheiros e cientistas de todas as áreas. Para mais informações sobre como o FPGA pode ser usado em variadas aplicações na indústria, pesquise em informações adicionais.

Referências

[1] http://www.ni.com/white-paper/6984/pt/