Mudanças entre as edições de "Experimento 14 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| (2 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 2: | Linha 2: | ||

== Arimética binária (Somador Comercial)== | == Arimética binária (Somador Comercial)== | ||

;Objetivos: | ;Objetivos: | ||

| − | * Compreender o funcionamento do circuito aritmético somador | + | * Compreender o funcionamento do circuito aritmético somador comercial; |

* Obter o sinal de saída simulado usando o QSIM - diagrama temporal; | * Obter o sinal de saída simulado usando o QSIM - diagrama temporal; | ||

* Analisar os tempos de propagação; | * Analisar os tempos de propagação; | ||

| Linha 25: | Linha 25: | ||

[[Arquivo:ArqEntradaSomador.png|800 px]] | [[Arquivo:ArqEntradaSomador.png|800 px]] | ||

| − | *Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0) | + | *Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0) |

| − | + | *Note que os bits das entradas estão agrupados e definidos como RADIX "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = A] > [Radix = Unsigned Decimal] > [OK]. Repita o procedimento para as entradas B. | |

| − | + | *Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = S] > [Radix = Unsigned Decimal] > [OK]. | |

| − | *Note que os bits das entradas estão agrupados e definidos como RADIX " | + | *Reverta a ordem dos bits de cada grupo. [Edit > Reverse Group or Bus Bits Order) |

| − | *Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = | + | *Faça a simulação temporal do circuito lógico usando o sinal criado (Simulation > Run Timing Simulation). |

| + | [[Arquivo:saidasomardor.png|800 px]] | ||

| − | |||

==Análise dos resultados== | ==Análise dos resultados== | ||

| + | *Verifique se o resultado obtido corresponde a um somador de 4 bits. | ||

| + | *Meça os atrasos de propagação através do uso de cursores. | ||

| + | *Compare o circuito Somador de 4 bits discreto com o comercial e indique qual simulação é a mais rápida. | ||

Edição atual tal como às 21h16min de 31 de março de 2015

Arimética binária (Somador Comercial)

- Objetivos

- Compreender o funcionamento do circuito aritmético somador comercial;

- Obter o sinal de saída simulado usando o QSIM - diagrama temporal;

- Analisar os tempos de propagação;

- Verificar os resultados obtidos;

- Materiais necessários

- 74X83(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

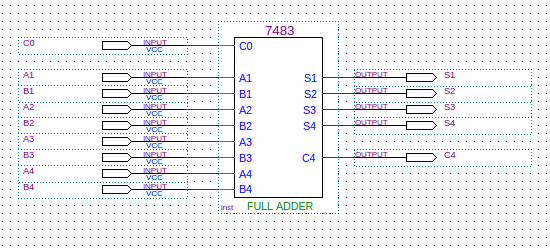

Diagrama Esquemático

- Abra o Quartus II e insira o diagrama esquemático do somador comercial, conforme a figura abaixo.

- Salve o arquivo como Somador.bdf em uma pasta vazia com nome Exp14, e crie um projeto Somador.qpf utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8. Após isso compile o projeto.

Simulação temporal com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

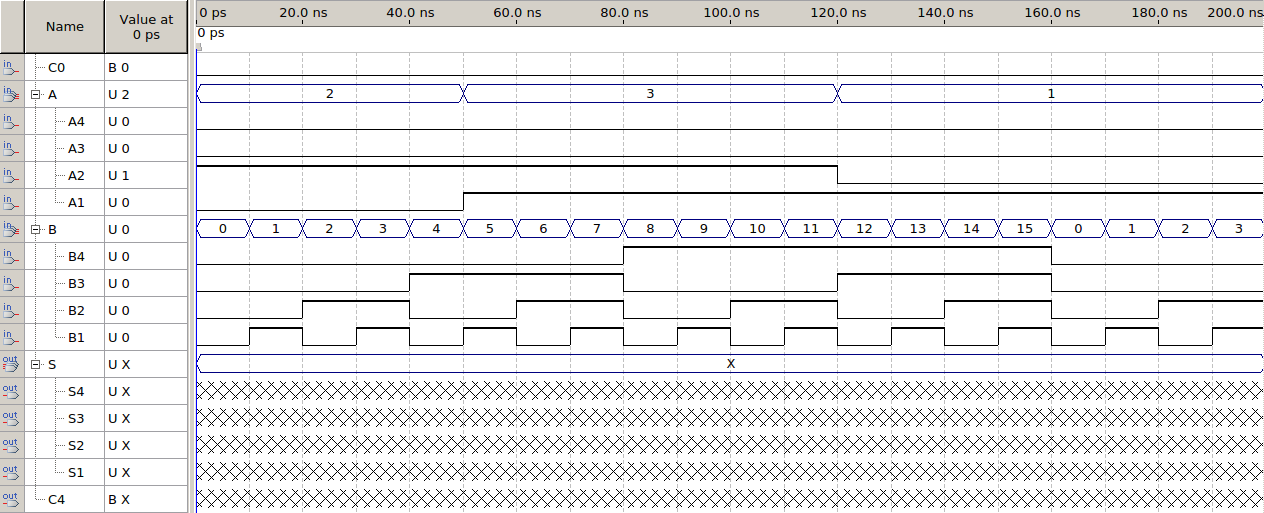

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome ArqEntrada.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

- Note que os bits das entradas estão agrupados e definidos como RADIX "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = A] > [Radix = Unsigned Decimal] > [OK]. Repita o procedimento para as entradas B.

- Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = S] > [Radix = Unsigned Decimal] > [OK].

- Reverta a ordem dos bits de cada grupo. [Edit > Reverse Group or Bus Bits Order)

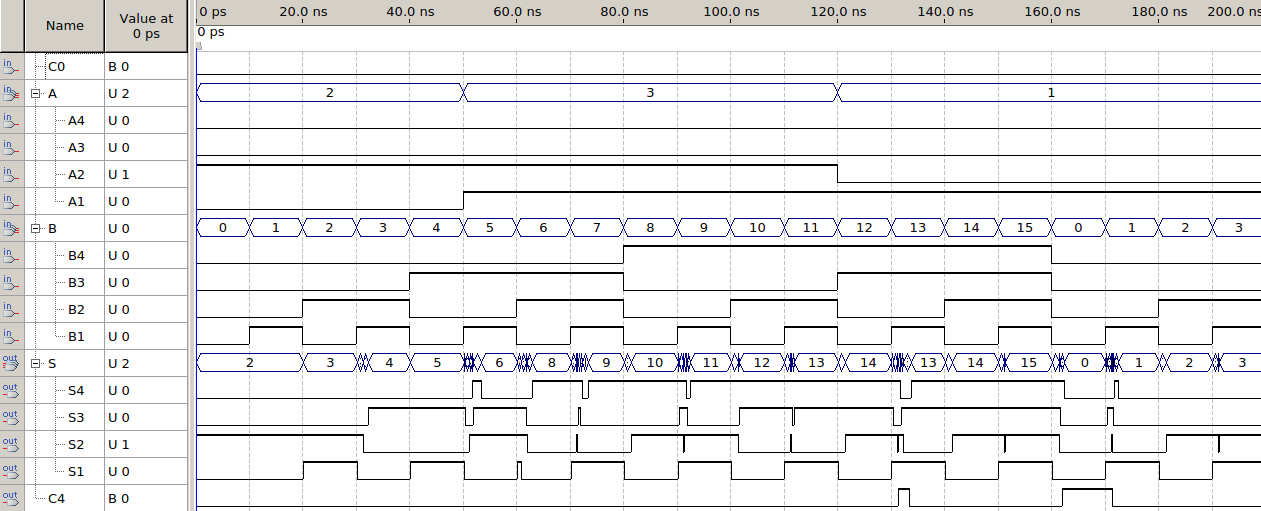

- Faça a simulação temporal do circuito lógico usando o sinal criado (Simulation > Run Timing Simulation).

Análise dos resultados

- Verifique se o resultado obtido corresponde a um somador de 4 bits.

- Meça os atrasos de propagação através do uso de cursores.

- Compare o circuito Somador de 4 bits discreto com o comercial e indique qual simulação é a mais rápida.