Mudanças entre as edições de "DLP29006-Engtelecom(2020-1) - Prof. Marcos Moecke"

| (74 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 4: | Linha 4: | ||

* 3 AULAS | * 3 AULAS | ||

| − | {{collapse top | + | {{collapse top | Unidade 1 - Introdução a disciplina}} |

;Aula 1 (10 fev): | ;Aula 1 (10 fev): | ||

| Linha 19: | Linha 19: | ||

::* CPLDs | ::* CPLDs | ||

{{collapse top | Exemplos de PLDs}} | {{collapse top | Exemplos de PLDs}} | ||

| − | + | {{fig|1.1|Macrobloco do PLD EP300 da ALTERA| ep310_macrocell.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | |

| − | |||

| − | |||

| − | + | {{fig|1.2|Macrocélula dos PLDs Clássicos EP600, EP900, EP1800 da ALTERA (1999)| Macrocell_EP900.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} | |

| − | |||

| − | |||

| − | + | {{fig|1.3a|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | |

| − | |||

| − | |||

| − | |||

| − | + | {{fig|1.3b|Architetura do PLD EP1800 da ALTERA| ep1800_block_diagram2.jpg| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf}} | |

| − | + | ||

| − | + | {{fig|1.5|Pinagem e tipos de encapsulamento do PLD EP1800 da ALTERA| PackagePinOut_EP1810.png| 400 px | https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/ds/archives/classic.pdf }} | |

| + | |||

| + | |||

| + | {{fig|1.6|Architetura do CPLD MAX 5000 da ALTERA| max_5000_architecture.jpg| 400 px | https://www.altera.com/solutions/technology/system-design/articles/_2013/in-the-beginning.html}} | ||

| − | |||

| − | |||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| Linha 84: | Linha 77: | ||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

* 3 AULAS | * 3 AULAS | ||

| − | {{collapse top| expand=true| | + | {{collapse top| expand=true | Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} |

| − | ;Aula 4 (19 | + | ;Aula 4 (19 mai): |

* Introdução ao VHDL e ambiente EDA - QUARTUS | * Introdução ao VHDL e ambiente EDA - QUARTUS | ||

* Estrutura do código VHDL | * Estrutura do código VHDL | ||

| Linha 139: | Linha 132: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | <!-- | ||

;Aula 5 (21 fev): | ;Aula 5 (21 fev): | ||

* Exemplo 2.2 (VHDL) - programação de um flip-flop | * Exemplo 2.2 (VHDL) - programação de um flip-flop | ||

| Linha 167: | Linha 161: | ||

:* Após a [[criação do projeto em VHDL]] utilizando a descrição de hardware acima, [[compile o código VHDL]]. | :* Após a [[criação do projeto em VHDL]] utilizando a descrição de hardware acima, [[compile o código VHDL]]. | ||

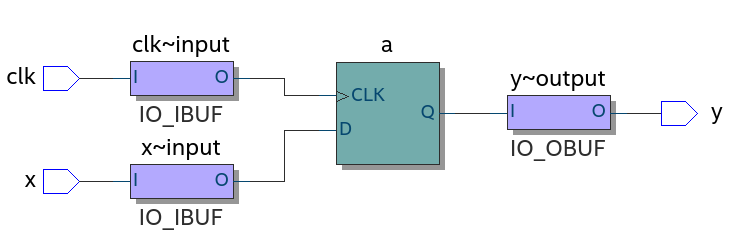

:* Use o [[RTL Viewer]] para ver a descrição RTL do circuito. | :* Use o [[RTL Viewer]] para ver a descrição RTL do circuito. | ||

| − | + | {{fig|2.2|Código RTL do Exemplo 2.2| RTL_Ex2_2_Pedronib.png| 400 px |}} | |

| − | |||

| − | |||

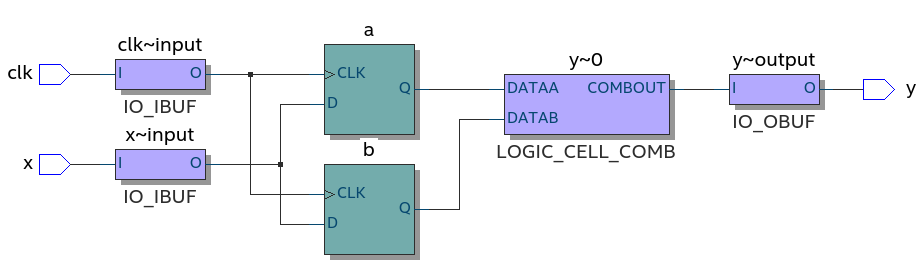

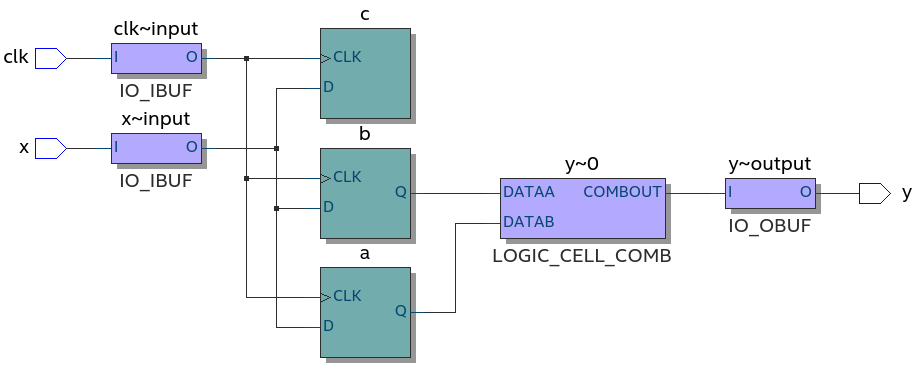

:* Use o [[Technology Map Viewer]] para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8) | :* Use o [[Technology Map Viewer]] para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8) | ||

| − | + | {{fig|2.3|Technology Map do Exemplo 2.2| TM_Ex2_2_Pedronib.png| 400 px |}} | |

| − | |||

| − | |||

:* Abra o [[Chip Planner]] e observe no [[Node Properties]] como esse circuito é conectado dentro do dispositivo FPGA selecionado | :* Abra o [[Chip Planner]] e observe no [[Node Properties]] como esse circuito é conectado dentro do dispositivo FPGA selecionado | ||

| − | + | {{fig|2.4|Chip Planner do Exemplo 2.2| ChipPlanner_Ex2_2_Pedronib.png| 400 px |}} | |

| − | |||

:* Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops | :* Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops | ||

| − | + | {{fig|2.5|RTL 4 FF| RTL_4FF.png| 400 px |}} | |

| − | |||

;Aula 6 e 7 (26 e 28 fev): | ;Aula 6 e 7 (26 e 28 fev): | ||

| Linha 250: | Linha 238: | ||

| − | + | ||

;Aula 7 e 8 (14 e 16 ago): | ;Aula 7 e 8 (14 e 16 ago): | ||

| Linha 256: | Linha 244: | ||

:*Realize as simulações funcional e temporal do circuito usando o QSIM. | :*Realize as simulações funcional e temporal do circuito usando o QSIM. | ||

| + | {{fig|2.6|Simulação Funcional de 4 FF 100ns| SIM1_4FF.png| 400 px |}} | ||

| − | + | {{fig|2.7|Simulação Temporal de 4 FF 100ns| SIM2_4FF.png| 800 px |}} | |

| − | |||

| − | |||

| − | |||

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. | Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. | ||

| Linha 319: | Linha 305: | ||

Clique sobre o sinal q na janela Objects e solte-o na janela Wave. Ao final desses passos a janela Wave deverá estar conforme mostrado abaixo: | Clique sobre o sinal q na janela Objects e solte-o na janela Wave. Ao final desses passos a janela Wave deverá estar conforme mostrado abaixo: | ||

| − | + | {{fig|2.8|Edição do Waveform de 4 FF 1000ns no Modelsim| MODELSIM_4FF_Edit.png| 800 px |}} | |

| − | |||

| − | |||

*'''PASSO 3''': Realize a simulação de 1000 ps | *'''PASSO 3''': Realize a simulação de 1000 ps | ||

| Linha 333: | Linha 317: | ||

Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned]. A janela Wave deverá estar conforme mostrado abaixo: | Selecione com o shift_clique_esquerdo do mouse os sinas d e q (barramentos de 4 bits) e em seguida clique_direito e selecione [radix > unsigned]. A janela Wave deverá estar conforme mostrado abaixo: | ||

| − | + | {{fig|2.9|Simulação funcional de 4 FF 1000ns no Modelsim| MODELSIM_4FF_Simul.png| 800 px |}} | |

| − | |||

| − | |||

*Note que a saída q está com (Forcing Unknown - (X em vermelho) entre 0 e 20 ps. Isso ocorre pois antes de aplicar o RESET o Flip Flop tem valor desconhecido. Por isso é sempre importante aplicar um RESET logo ao iniciar a simulação de um circuito sequencial. | *Note que a saída q está com (Forcing Unknown - (X em vermelho) entre 0 e 20 ps. Isso ocorre pois antes de aplicar o RESET o Flip Flop tem valor desconhecido. Por isso é sempre importante aplicar um RESET logo ao iniciar a simulação de um circuito sequencial. | ||

| Linha 423: | Linha 405: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

:: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador QSIM e realize novas simulações funcional e temporal. | :: Acrescente saídas para o sinal '''sum''' e para o sinal '''comp''', de modo a poder observar estes sinais no simulador QSIM e realize novas simulações funcional e temporal. | ||

| − | + | {{fig|2.10|Código RTL do Exemplo 2.3| RTL_Ex2_3_Pedronib.png| 400 px |}} | |

| − | |||

| − | |||

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso nestas mudanças. | Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso nestas mudanças. | ||

| Linha 441: | Linha 421: | ||

* 7 AULAS | * 7 AULAS | ||

| − | {{collapse top | + | {{collapse top | Unidade 3 - Tipos de Dados e Operadores em VHDL}} |

;Aula 8 (3 mar): | ;Aula 8 (3 mar): | ||

| Linha 708: | Linha 688: | ||

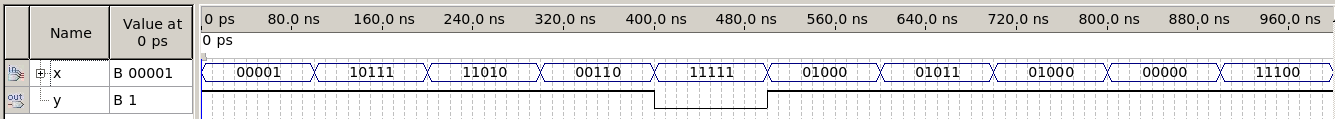

* '''Desafio''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 5 vagas. Cada entrada x(n) está alta '1' se a vaga está vazia. A saída y estará alta '1' sempre que houver uma ou mais vagas vazias. | * '''Desafio''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 5 vagas. Cada entrada x(n) está alta '1' se a vaga está vazia. A saída y estará alta '1' sempre que houver uma ou mais vagas vazias. | ||

*Faça a simulação do circuito para ver se está funcionando, | *Faça a simulação do circuito para ver se está funcionando, | ||

| − | + | {{fig|3.1| Simulação de contador de vagas | vagas5.png | 800 px |}} | |

:: Ver função resize | :: Ver função resize | ||

:: Ver pag. 73 a 78 de <ref name="PEDRONI2010b"/> | :: Ver pag. 73 a 78 de <ref name="PEDRONI2010b"/> | ||

| Linha 875: | Linha 855: | ||

end configuration; | end configuration; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | + | {{fig|3.2| RTL do conversor de Binário para BCD com 2 digitos | bin2bcdDU_RTL.png | 600 px |}} | |

| − | + | ||

| − | + | {{fig|3.3| Simulação do conversor de Binário para BCD com 2 digitos | bin2bcdDU_modelsim.png | 1000 px |}} | |

| − | |||

| − | |||

| − | |||

| − | ==INICIO DAS AULAS REMOTAS SÍNCRONAS== | + | ====INICIO DAS AULAS REMOTAS SÍNCRONAS==== |

;Aula 13 (24 mar): | ;Aula 13 (24 mar): | ||

| Linha 981: | Linha 956: | ||

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o '''Technology Map''' dos circuitos gerados e verifique a localização dos FFs no '''Chip Planner'''. | Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o '''Technology Map''' dos circuitos gerados e verifique a localização dos FFs no '''Chip Planner'''. | ||

| − | + | {{fig|3.4| Technology Map do circuito compilado sem Attribute | Ex4_5_NoAttribute.png | 400 px |}} | |

| − | + | ||

| − | + | {{fig|3.5| Technology Map do Circuito com Attribute Preserve (or Keep) | Ex4_5_PreserveAttribute.png | 400 px |}} | |

| + | |||

| + | {{fig|3.6| Technology Map do Circuito com Attribute Noprune | Ex4_5_NopruneAttribute.png | 400 px |}} | ||

| + | |||

| + | :: Ver pag. 91 a 111 de <ref name="PEDRONI2010b"/> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| Linha 1 132: | Linha 1 111: | ||

* A implementação de circuitos aritméticos com operadores deve seguir as seguintes recomendações: | * A implementação de circuitos aritméticos com operadores deve seguir as seguintes recomendações: | ||

:* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar o pacote '''numeric_std''' da biblioteca '''ieee'''. | :* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar o pacote '''numeric_std''' da biblioteca '''ieee'''. | ||

| − | + | {{fig|3.7| Conversões entre tipos Integer, Unsigned, Signed, Std_logic_vector | Numeric_stdConvertions.gif | 600 px | [[Aritmética com vetores em VDHL]]}} | |

| − | + | ||

| − | |||

| − | |||

:* a conversão de um objeto (vetor)'''a_SLV''' do tipo STD_LOGIC_VECTOR para um objeto (vetor)'''a_UNS (a_SIG)''' do tipo UNSIGNED (SIGNED) é feita pela conversão de tipo '''UNSIGNED''' | :* a conversão de um objeto (vetor)'''a_SLV''' do tipo STD_LOGIC_VECTOR para um objeto (vetor)'''a_UNS (a_SIG)''' do tipo UNSIGNED (SIGNED) é feita pela conversão de tipo '''UNSIGNED''' | ||

a_UNS <= unsigned(a_SLV); | a_UNS <= unsigned(a_SLV); | ||

| Linha 1 236: | Linha 1 213: | ||

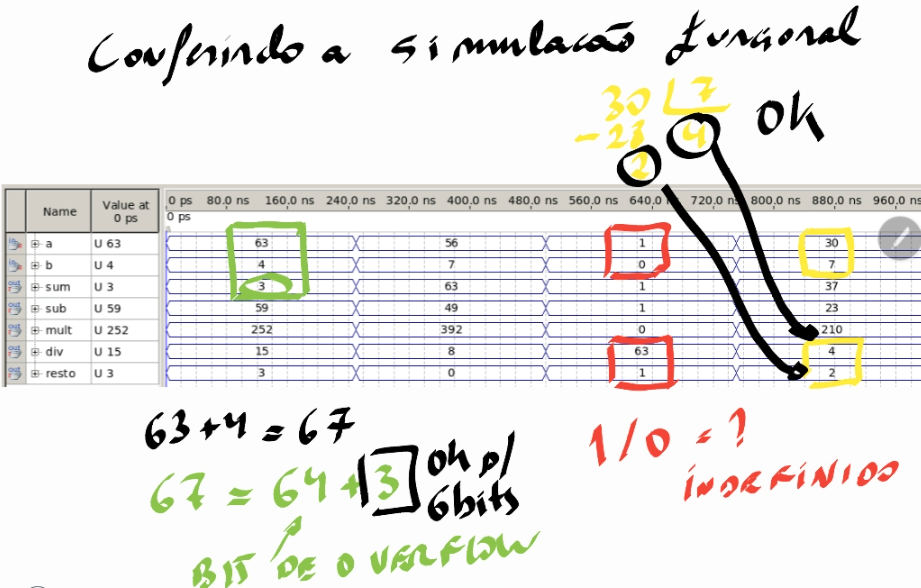

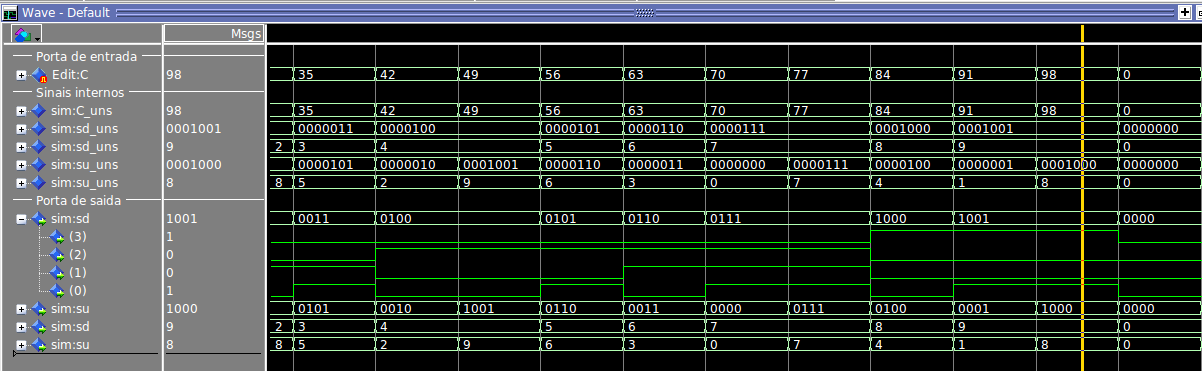

;Resultados da simulação funcional. | ;Resultados da simulação funcional. | ||

Após a simulação funcional, é necessário analisar os resultados obtidos em cada operação. A figura abaixo mostra 3 analises realizadas. | Após a simulação funcional, é necessário analisar os resultados obtidos em cada operação. A figura abaixo mostra 3 analises realizadas. | ||

| − | + | ||

| + | {{fig|3.8| Simulação funcional do Multiplicador/Divisor/Somador/Subtrator | OperadoresQSIM.png | 600 px |}} | ||

| + | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| Linha 1 411: | Linha 1 390: | ||

* 4 AULAS | * 4 AULAS | ||

| − | {{collapse top| | + | {{collapse top| Unidade 4 - Código Concorrente}} |

;Aula 19 (7 abr): | ;Aula 19 (7 abr): | ||

*Código Concorrente. | *Código Concorrente. | ||

| Linha 1 585: | Linha 1 564: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

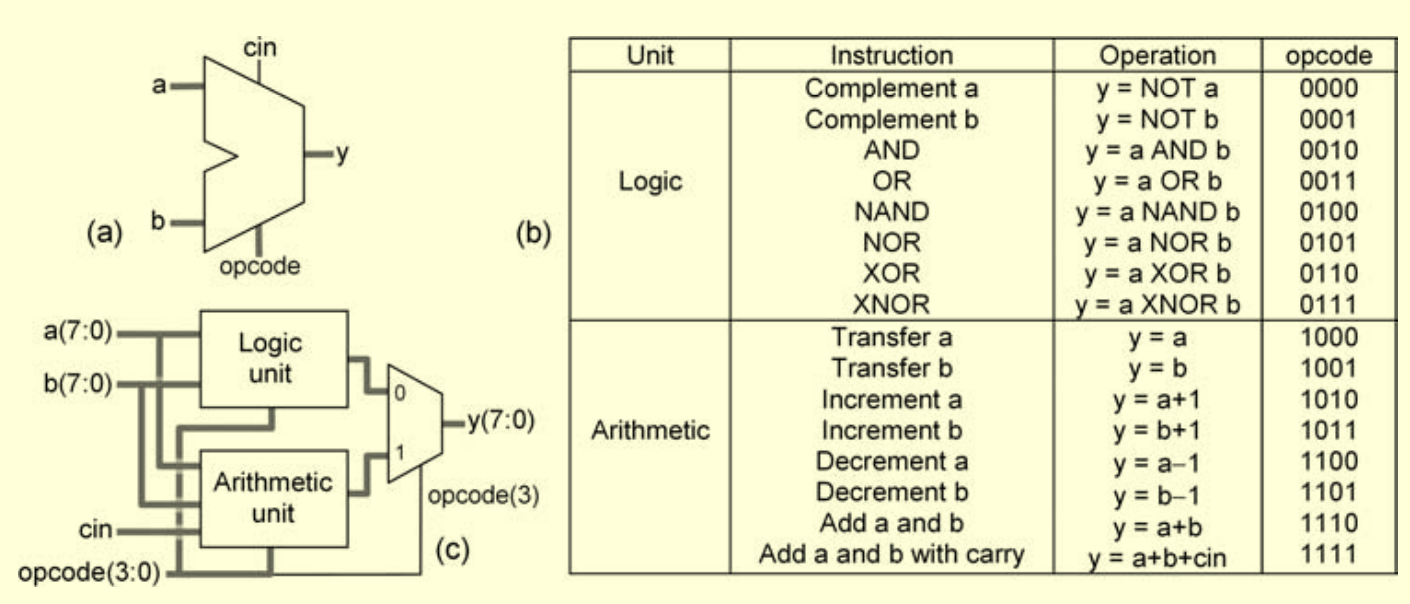

| − | + | {{fig|3.9| Unidade de Lógica e Artimética | Alu_pedroni.png | 600 px | pag. 127 <ref name="PEDRONI2010b"/>}} | |

| − | |||

::*Faça as seguintes alterações no código da ALU: | ::*Faça as seguintes alterações no código da ALU: | ||

| Linha 1 631: | Linha 1 609: | ||

===Unidade 5 - Código Sequencial=== | ===Unidade 5 - Código Sequencial=== | ||

* 7 AULAS | * 7 AULAS | ||

| − | {{collapse top | + | {{collapse top| Unidade 5 - Código Sequencial}} |

;Aula 22 (15 abr): | ;Aula 22 (15 abr): | ||

*Código Sequencial. | *Código Sequencial. | ||

| Linha 1 707: | Linha 1 685: | ||

:*Ver pag. 161 a 160 de <ref name="PEDRONI2010b"/> | :*Ver pag. 161 a 160 de <ref name="PEDRONI2010b"/> | ||

| − | |||

;Aula 23 (17 abr): | ;Aula 23 (17 abr): | ||

| − | + | * Simulação funcional do DFFs e do Latch | |

| + | |||

| + | * Porta paralela com N DFFs. | ||

| + | |||

| + | * Contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | ||

| + | :* Com overflow no valor máximo | ||

| − | + | ;Aula 24 (22 abr): | |

| + | * Contador crescente 0-N (baseado no Ex.6.2), com N =/= 2^Mbits (5, 10) | ||

| + | :* Com parada no valor máximo | ||

| + | :* Com overflow no valor máximo | ||

| − | + | * Contador decrescente 0-N (baseado no Ex.6.2), com N =/= 2^Mbits (5, 10) | |

| − | + | :* Com parada no valor mínimo | |

| − | * | + | :* Com underflow no valor máximo |

| − | + | * Projetar um contador em BCD entre 0 e 99, com entrada de clock, reset e saidas unidade(0 a 9) e dezena (0 a 9). | |

| − | * | + | :* versão 1 - contagem crescente. |

| − | :* | + | :* versão 2 - contagem decrescente. |

| − | :: | + | :* versão 3 - contagem crescente ou decrescente controlado por uma entrada DIR. Se DIR = '0' a contagem é crescente se DIR = '1' a contagem é decrescente. |

| − | :: | + | :'''Nota:''' |

| + | ::Antes de implementar a versão 3 verifique no RTL das versões 1 e 2 as diferenças, e pense nas possibilidades de reutilização do hardware. O que é comum entre elas e o que precisa ser acrescentado na versão 3. | ||

| + | ::Tente obter uma versão com o mínimo acréscimo em elementos lógicos. | ||

| − | |||

| − | + | ;Aula 25 (24 abr): | |

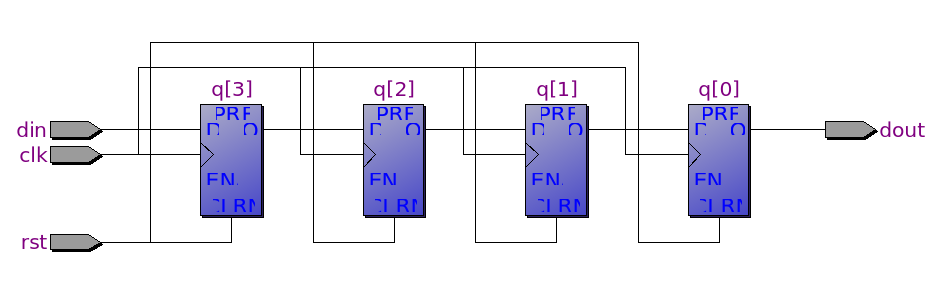

| − | : | + | * Registrador de deslocamento (Ex.6.3) |

| − | + | <center>[[Arquivo:ShifRegRight.png| 800px]]</center> | |

| − | < | ||

| − | [ | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | </ | ||

| − | : | + | :Versão 1 - Implementação com 4 FF D. |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | entity shift_reg4_right is | |

| − | + | port | |

| − | + | ( | |

| − | + | din, clk, rst : in std_logic; | |

| − | + | dout : out std_logic | |

| − | + | ); | |

| + | end entity; | ||

| − | + | architecture ifsc of shift_reg4_right is | |

| − | + | begin | |

| − | + | end architecture; | |

| − | |||

| − | |||

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | : | + | :Versão 2 - Implementação com for generate da conexão de FF D. |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | entity shift_reg_right is | |

| − | + | generic (N : integer := 4); | |

| − | + | port | |

| − | + | ( | |

| − | + | din, clk, rst : in std_logic; | |

| − | + | dout : out std_logic | |

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc of shift_reg_right is | ||

| + | begin | ||

| + | |||

| + | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | :Versão 3 - Implementação com formação de agregado via concatenação. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity shift_reg_right is | ||

| + | generic (N : integer := 4); | ||

| + | port | ||

| + | ( | ||

| + | din, clk, rst : in std_logic; | ||

| + | dout : out std_logic | ||

| + | ); | ||

| + | end entity; | ||

| − | :: | + | architecture ifsc of shift_reg_right is |

| − | + | begin | |

| − | + | process (clk, rst) | |

| − | + | variable q : std_logic_vector (N-1 downto 0); | |

| − | + | begin | |

| − | + | if (rst = '1') then | |

| − | + | q := (others => '0'); | |

| − | + | elsif (clk'EVENT and clk = '1') then | |

| − | + | q := din & q (N-1 downto 1); | |

| + | end if; | ||

| + | dout <= q(0); | ||

| + | end process; | ||

| + | end architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ;Aula 28 | + | ;Aula 26 (28 abr): |

| − | :* | + | Aproveitando a versão 3 ou 2 do Shift Register, projete e faça a simulação dos dois circuitos indicados a seguir: |

| + | |||

| + | * Embrião de um conversor serial para paralelo. | ||

| + | <center>[[Arquivo:Serial2Parallel.png| 800px]]</center> | ||

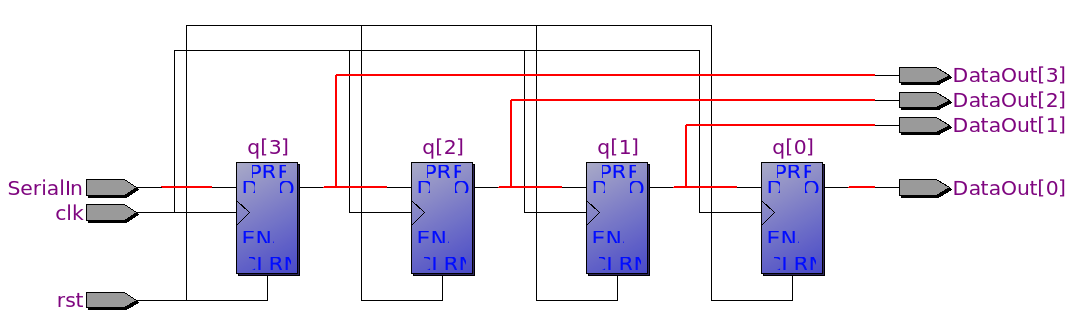

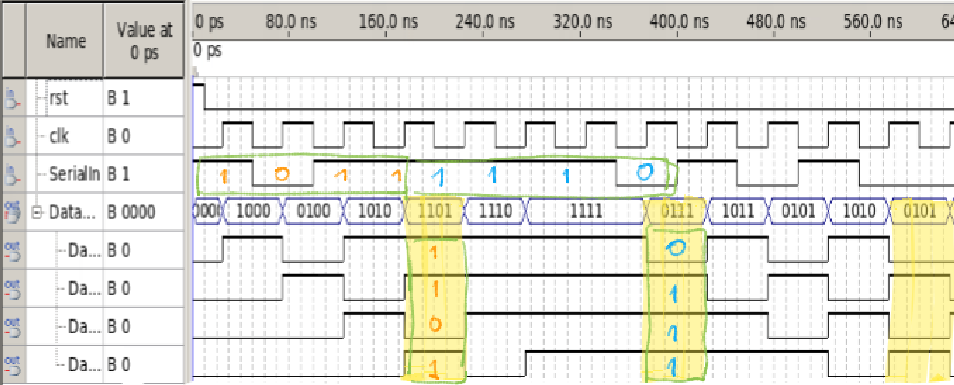

| + | :Para usar o hardware do ShifRegister como base para um conversor serial para paralelo, basta conectar as saidas dos FFD em portas '''DataOut'''(N-1) até '''DataOut'''(0). Assim, os sinais seriais da entrada '''SerialIn''' estarão disponíveis nestas saídas '''DataOut''' a cada N clocks. | ||

| + | |||

| + | <center>[[Arquivo:Serial2Parallel_SIM.png| 800px]]</center> | ||

| + | :Uma simulação com o QSIM é mostrada na figura acima. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | entity serial2parallel is | |

| − | + | port | |

| − | + | ( | |

| − | + | clk, rst : in std_logic; | |

| − | + | SerialIn : in std_logic; | |

| − | + | DataOut : out std_logic_vector(N-1 downto) | |

| − | + | ); | |

| + | end entity; | ||

| + | |||

| + | architecture ifsc of serial2parallel is | ||

| + | begin | ||

| − | + | end architecture; | |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | * Embrião de um conversor paralelo para serial. | |

| − | : | + | <center>[[Arquivo:Paralelo2Serial.png| 1200px]]</center> |

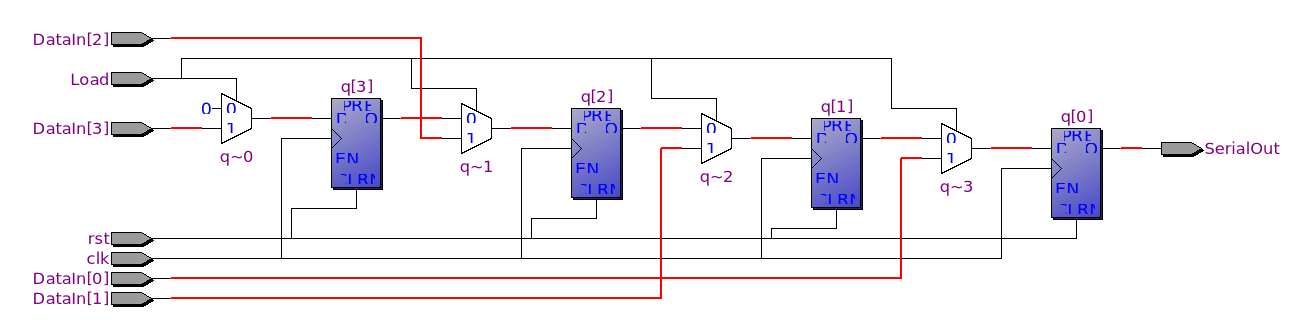

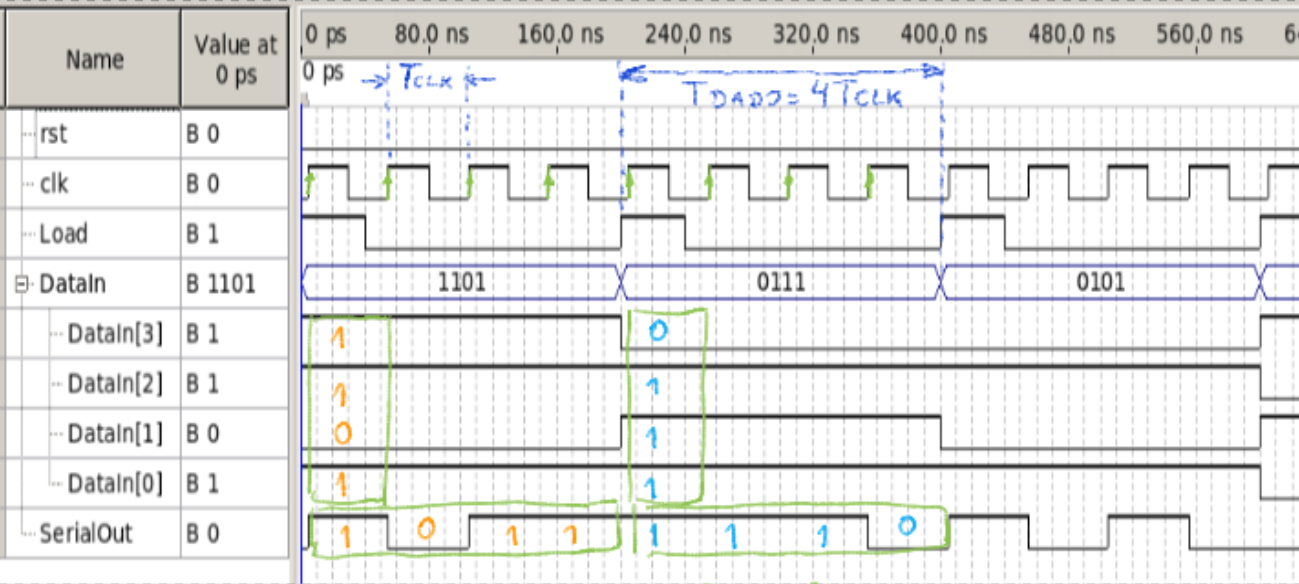

| − | + | :Para usar o hardware do ShiftRegister como base para um conversor paralelo para serial, é necessário carregar os dados paralelos do '''DataIn''' com o sinal '''Load''' nos FFD e em seguida fazer o deslocamento deles bit por bit durante N clocks. Na saída '''SerialOut''' do ShiftRegister os dados serão seriazados, aparecendo um cada clock. | |

| + | |||

| + | <center>[[Arquivo:Paralelo2Serial_SIM.png| 800px]]</center> | ||

| + | :Uma simulação com o QSIM é mostrada na figura acima. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity parallel2serial is | ||

| + | port | ||

| + | ( clk, rst : in std_logic; | ||

| + | Load : in std_logic; | ||

| + | DataIn : in std_logic_vector(N-1 downto); | ||

| + | SerialOut : out std_logic | ||

| + | ); | ||

| + | end entity; | ||

| − | + | architecture ifsc of parallel2serial is | |

| − | + | begin | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | ; | + | end architecture; |

| − | + | </syntaxhighlight> | |

| − | :* | + | |

| − | : | + | :*Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT |

| − | + | ::*LOOP incondicional: | |

| − | |||

| − | : | ||

| − | :* | ||

| − | |||

| − | |||

| − | |||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | [rótulo:] LOOP | |

| − | + | afirmação_sequencial; | |

| − | + | afirmação_sequencial; | |

| − | + | ... | |

| − | + | END LOOP [rótulo]; | |

| − | |||

| − | |||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ::*FOR-LOOP: | |

| − | :* | ||

| − | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | [rótulo:] FOR identificador IN faixa LOOP | |

| − | + | afirmação_sequencial; | |

| − | + | afirmação_sequencial; | |

| − | + | ... | |

| − | + | END LOOP [rótulo]; | |

| − | + | </syntaxhighlight> | |

| − | + | ||

| − | + | ::*WHILE-LOOP: | |

| − | </syntaxhighlight> | + | <syntaxhighlight lang=vhdl> |

| − | :: | + | [rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira |

| − | * | + | afirmação_sequencial; |

| − | + | afirmação_sequencial; | |

| − | + | ... | |

| − | *''' | + | END LOOP [rótulo]; |

| − | + | </syntaxhighlight> | |

| − | + | ||

| − | - | + | ::*LOOP com EXIT: |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | [rótulo:] [FOR identificador IN faixa] LOOP | |

| − | + | afirmação_sequencial; | |

| − | + | EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP" | |

| − | + | afirmação_sequencial; | |

| − | + | ... | |

| − | + | END LOOP [rótulo]; | |

| − | + | </syntaxhighlight> | |

| − | + | ||

| − | + | ::*LOOP com NEXT: | |

| − | + | <syntaxhighlight lang=vhdl> | |

| − | + | [rótulo:] [FOR identificador IN faixa] LOOP | |

| − | + | afirmação_sequencial; | |

| − | + | NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP" | |

| − | + | -- e incrementa o "identificador". | |

| − | + | afirmação_sequencial; | |

| − | + | ... | |

| − | + | END LOOP [rótulo]; | |

| + | </syntaxhighlight> | ||

| + | |||

| + | * Exemplos: | ||

| + | :* Leading Zeros (LOOP com EXIT) (Ex 6.5) - Esse circuito deve determinar quantos zeros tem em um vetor de entrada '''Vin''' antes do primeiro bit '1', começando da esquerda para a direita. | ||

| + | ::*Fazer a síntese do circuito; fazer simulação no Modelsim; analisar a forma como o compilador implementou o incrementador. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity leading_zeros is | ||

| + | generic (N : natural := 8); | ||

| + | port | ||

| + | ( Vin : in std_logic_vector(0 to N-1); | ||

| + | count : out integer range 0 to N | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc of leading_zeros is | ||

| + | begin | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Contador de zeros (FOR LOOP) - Esse circuito deve determinar quantos zeros tem em um vetor de entrada '''Vin'''. | ||

| + | ::*Fazer a síntese do circuito; fazer simulação no Modelsim; analisar a forma como o compilador implementou o incrementador. | ||

| + | |||

| + | *Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ;Aula 27 (29 abr): | ||

| + | * Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar. | ||

| + | :* Um somador do tipo carry ripple utiliza o bloco básico '''full adder''' para construir somadores de qualquer número de bits. Os bits carry são adicionados aos blocos posteriores, produzindo um hardware combinário. | ||

| + | :* O full adder é baseado nas funções. | ||

| + | ::<math> s_k = a_k \oplus b_k \oplus c_k </math> | ||

| + | ::<math> c_{k+1} = a_k . b_k + a_k . c_k + b_k . c_k </math> | ||

| + | :: onde <math> c_{k+1} </math> é o '''carry out''', <math> c_{k} </math> é o '''carry in''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity carry_ripple_adder is | ||

| + | generic (N : integer := 4); | ||

| + | port ( | ||

| + | a, b : std_logic_vector (N-1 downto 0); | ||

| + | cin : std_logic | ||

| + | s : out std_logic_vector (N downto 0); | ||

| + | cout : out std_logic; | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture estrutural of carry_ripple_adder | ||

| + | begin | ||

| + | -- Uso de um codigo sequencial para geracao de um circuito combinacional | ||

| + | process (a, b, cin) | ||

| + | variable c : std_logic_vector(N downto); | ||

| + | begin | ||

| + | c(0) := cin; | ||

| + | for i in 0 to N - 1 loop | ||

| + | -- Codigo de um full adder | ||

| + | -- soma de dois bits e carry_in do full adder anterior | ||

| + | s(i) <= a(i) xor b(i) xor c(i); | ||

| + | -- geraao do carry_out para o proximo full adder | ||

| + | c(i + 1) := (a(i) and b(i)) or (a(i) and c(i)) or (b(i) and c(i)); | ||

| + | end loop; | ||

| + | cout <= c(N); | ||

| + | end process; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Instrução '''CASE''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] CASE expressão IS | ||

| + | WHEN valor => atribuições; -- valor único | ||

| + | ... | ||

| + | WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores | ||

| + | ... | ||

| + | WHEN valor1 TO valor2 => atribuições; -- faixa de valores | ||

| + | ... | ||

| + | |||

| + | END CASE; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] WAIT UNTIL <condition>; | ||

| + | [rótulo:] WAIT ON sensitivity_list; | ||

| + | [rótulo:] WAIT FOR time_expression; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT. | ||

| + | :Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ||

| + | |||

| + | * Exemplo: Timer de 0 a 9 segundos com saída SSD (Ex 6.6). | ||

| + | :* Unir o código de um contador de 0 a 9 (código sequencial), e um conversor de binário para sete segmentos em código sequencial (usando CASE). | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity timer0_9 is | ||

| + | port ( | ||

| + | clk1seg,rst: in std_logic; | ||

| + | count_out : out std_logic_vector(3 downto 0); | ||

| + | ssd_out : out std_logic_vector(6 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of timer0_9 is | ||

| + | |||

| + | begin | ||

| + | process (rst, clk1seg) | ||

| + | -- processo do contador de 0 a 9 | ||

| + | end process; | ||

| + | |||

| + | process (count) | ||

| + | begin | ||

| + | -- processo do codificador de binario para display de sete segmentos | ||

| + | end process; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | |||

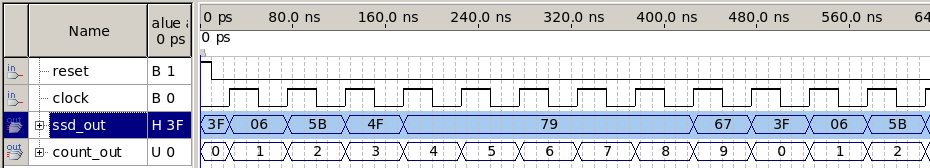

| + | A simulação funcional do circuito deverá produzir uma saída semelhante a mostrada abaixo: | ||

| + | <center>[[Arquivo:Timer0_9_SIM_FUNC.png| 800px]] </center> | ||

| + | |||

| + | A simulação com timing do circuito deverá produzir uma saída semelhante a mostrada abaixo: | ||

| + | <center>[[Arquivo:Timer0_9_SIM_TIME.png| 800px]] </center> | ||

| + | |||

| + | :* Depois acrescentar a esse circuito um módulo que permita a partir de um sinal de clock com frequência de fclk = 50MHz (T = 20 ns), obter um clock de f = 1 Hz (T = 1 s) | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | process (rst, clk50MHz) | ||

| + | -- processo do divisor de clock de 50MHz para 1 Hz | ||

| + | end process; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Implementar no FPGA o circuito com contador de 0 a 9 segundos com saída SSD e clk de entrada de 50MHz. | ||

| + | |||

| + | ::*PROBLEMA: Uso de um período de clock de 20 ns => 50 MHz, verificar a impossibilidade prática de uma simulação deste circuito (1 segundo => 5 minutos de simulação), devido ao tamanho do contador (count1) que conta de 0 a 50M-1. | ||

| + | ::*SOLUÇÃO: modificar o contador para um valor máximo menor (0 a 50-1). Notar que a simulação é extremamente rápida neste caso. | ||

| + | ::*Após verificar que o circuito funciona "simulado", configurar o FPGA do kit Mercúrio IV para implementar este circuito. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. Utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | ::* Como o conversor de binário para ssd realizado anteriormente tinha lógica negativa ('0' acende, '1' apaga), será necessário inverter todas as saídas | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ssd_out <= not ssd; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*Se quiser usar algum led na matriz de led do kit Mercúrio é necessário colocar '0' da coluna do Led e '1' na linha correspondente, ou seja utilizar um segundo pino para acender o led. | ||

| + | |||

| + | ;Dias 5, 6, 8 12, 13 e 15 mai: | ||

| + | *Parada Pedagógica sem aulas de acordo com a resolução do colegiado do campus de São José. | ||

| + | |||

| + | |||

| + | ;Dia 19 mai: | ||

| + | |||

| + | *Retorno às ANPs, <!--porém sem aula de acordo com mensagem recebida do chefe do DEPE. --> | ||

| + | *Foi solicitado que todos alunos se cadastram no workspace da disciplina no [https://join.slack.com/t/dlp29006/shared_invite/zt-eefed09w-tTRvXs7oImjvEhJIt7tN0Q SLACK]. | ||

| + | *Foi solicitado que todos alunos respondam a uma sondagem sobre as ANPs [https://forms.gle/Y6kTj2tvJDJPCsHc7 Volta às aulas não presenciais em tempo de pandemia]. | ||

| + | |||

| + | *Resultado das outras enquetes no SLACK: | ||

| + | :Você gostaria que a UC de DLP29006 tivesse continuidade através de ANPs durante a pandemia do corona virus? | ||

| + | :::sim | ||

| + | ::: | ||

| + | :::não | ||

| + | |||

| + | |||

| + | |||

| + | <!-- | ||

| + | ;Aula 29 (14 out): | ||

| + | *Uso do Modelsim para simulação funcional. | ||

| + | :*Use o Modelsim para fazer a simulação do circuito do timer de 0 a 9 segundos. | ||

| + | :*Ver [[Seguindo o tutorial da ALTERA para o MODELSIM]], para utilizar o básico do MODELSIM. | ||

| + | :* [http://www.vhdl.us/Book_VHDL_2ed_unrestricted/Pedroni_VHDL_2ed_tutorial_ModelSim_10.1d_v2.pdf Pedroni VHDL 2ed Tutorial of ModelSim 10.1d] | ||

| + | :* [https://www.youtube.com/watch?v=Z8whdGa7RtY ModelSim Video Tutorial] - Kirk Weedman | ||

| + | :*[[Media:modelsim_tut.pdf |ModelSim® Tutorial]] -v10.0d | ||

| + | :* [[Documentação do ModelSim]], para conhecer mais a fundo o MODELSIM. | ||

| + | --> | ||

| + | <!-- | ||

| + | *Projete um contador BCD de 00 a 99 configurável. | ||

| + | ::Efetue a simulação funcional (Usando o QSIM e o Modelsim) fazendo a contagem de 00 a 11 e 00 a 23 (para hora) , de 00 a 59 (para minutos e segundos), e de 00 a 99. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity Count00_99 is | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Implementação de um relógio contador BCD de segundos. | ||

| + | :*Utilizando o sistema anterior, inclua um contador em BCD de dois dígitos que permita fazer a contagem de 00 a 99, onde o valor final é configurável. | ||

| + | ::Efetue a simulação funcional (Usando o QSIM e o Modelsim) fazendo a contagem de 00 a 11 e 00 a 23 (para hora) , de 00 a 59 (para minutos e segundos), e de 00 a 99. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity Timer00_99seg is | ||

| + | port ( | ||

| + | clk50MHz : in std_logic; | ||

| + | clk1seg : out std_logic; | ||

| + | SSD_Useg : out std_logic_vector(0 to 6); | ||

| + | SSD_Dseg : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | ::configure o FPGA do kit Mercúrio IV para implementar este circuito. Utilize os mostradores ssd DISP0_D e DISP1_D. | ||

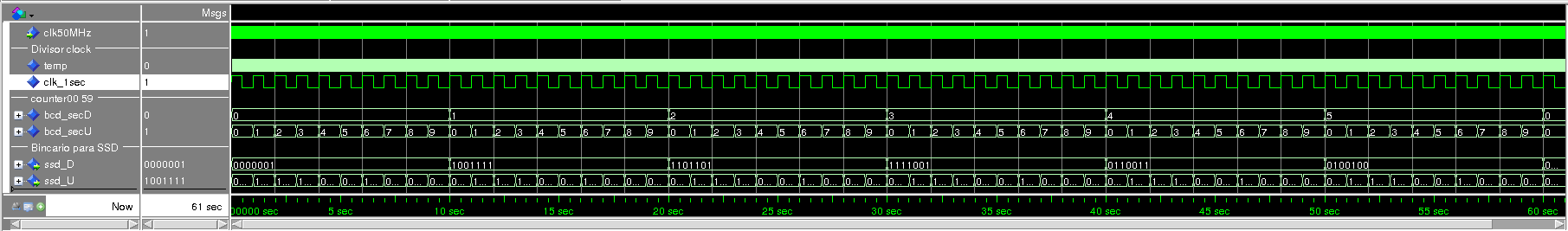

| + | *Projeto e simulação com Modelsim do sistema Timer00-99 com display de 7 segmentos e divisor de clock. | ||

| + | *Na simulação definir o clk50MHz como 100ms para produzir um clk1sec com duração de 1 segundo. | ||

| + | *Corrigir o primeiro período de clock de clk1sec. É necessário fazer com que o sinal seja alto primeiro e depois vá para baixo de modo a garantir que a transição positiva ocorra depois de 1 segundo. | ||

| + | *'''IMPORTANTE''': Também é necessário incluir um RESET em cada circuito que seja sequencial. Também é necessário iniciar o circuito com um reset de 10 ps na simulação. | ||

| + | *Perceber a necessidade de parametrizar o conversor de bcd2ssd para permitir displays do tipo CA e AA. (ler [[Display de 7 segmentos]]) | ||

| + | *Perceber a necessidade de incluir um sinal que indique o final da contagem no counter00_99. Esse sinal poderá ser usado como clock no relógio a ser projetado. | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 6 - Projeto a nível de Sistema=== | ||

| + | * 8 AULAS | ||

| + | {{collapse top| Unidade 6 - Projeto a nível de Sistema}} | ||

| + | |||

| + | ; Aula XX (9 e 10 jun): | ||

| + | *Projeto a nível de Sistema. | ||

| + | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| + | :* O '''COMPONENT''': declaração (cópia da '''ENTITY''') e instanciação. | ||

| + | Assim a entity Timer00_99 | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ENTITY timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END ENTITY; | ||

| + | </syntaxhighlight> | ||

| + | Será declarada como um COMPONENT | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | COMPONENT timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END COMPONENT; | ||

| + | </syntaxhighlight> | ||

| + | ::* Associação dos nomes das portas aos sinais. PORT -> '''PORT MAP''': | ||

| + | ::* Mapeamento por posição e nominal. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP (2, 10, 3) | ||

| + | PORT MAP (clk50MHz,RST, clk1seg, SSD_Dseg, SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP ( D => 2, U => 3, | ||

| + | fclock => 10, | ||

| + | PORT MAP ( clk50MHz => clk50MHz, | ||

| + | RST => RST, | ||

| + | clk1seg => clk1seg, | ||

| + | SSD_Dseg => SSD_Dseg, | ||

| + | SSD_Useg => SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | ::* Métodos de declaração de '''COMPONENT'''. | ||

| + | :::*Exemplo: Registrador Circular Ex. 8.2 | ||

| + | :* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | ||

| + | ::*Exemplo: Porta E com N entradas. | ||

| + | ::*Exemplo: Detector de Paridade Ex. 8.3 | ||

| + | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | |||

| + | :* Instanciação de '''COMPONENT''' com '''GENERATE'''. | ||

| + | |||

| + | :* Uso da instrução '''CONFIGURATION'''. | ||

| + | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

| + | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| + | |||

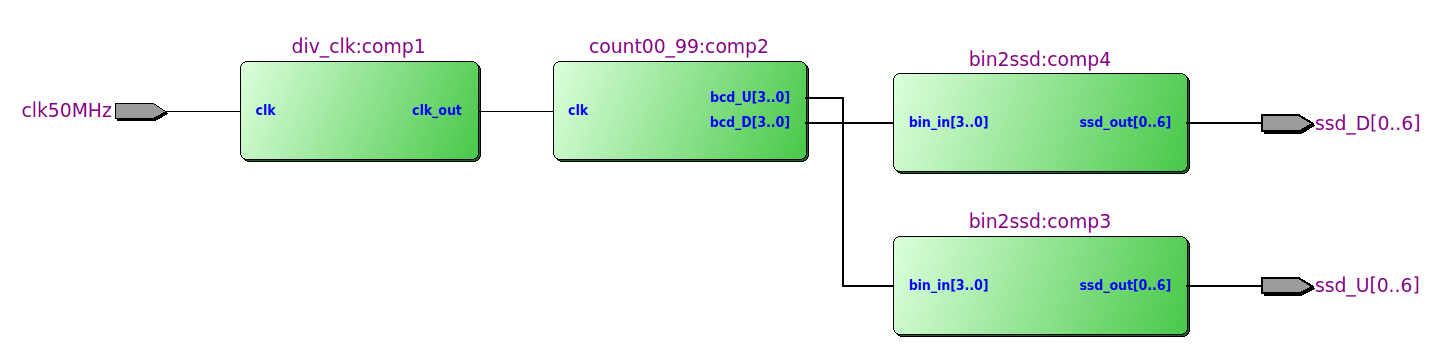

| + | * Implementação de um timer de 99 segundos usando componentes. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity timer00_99seg IS | ||

| + | generic (fclk2 : natural := 50, D : natural := 5; U : natural := 9); | ||

| + | port | ||

| + | ( | ||

| + | clk50MHz : in STD_LOGIC; | ||

| + | clk_1seg: out STD_LOGIC; | ||

| + | ssd_D : out STD_LOGIC_VECTOR(0 TO 6); | ||

| + | ssd_U : out STD_LOGIC_VECTOR(0 TO 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo parâmetro '''fclk2''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component div_clk is | ||

| + | generic (fclk2 : natural := 50); -- frequecia para simulacao | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic | ||

| + | ); | ||

| + | end component; | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | |||

| + | </syntaxhighlight> | ||

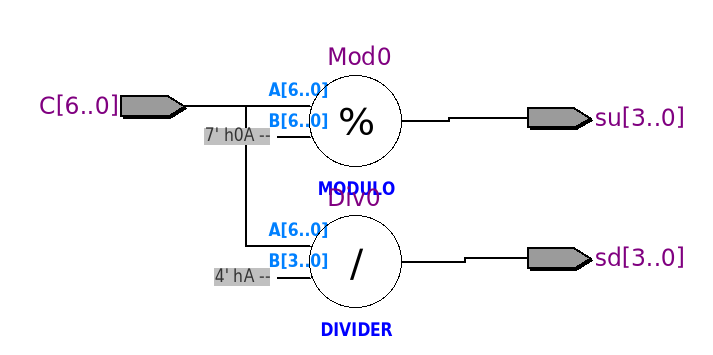

| + | : Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos parâmetros '''D e U''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component count00_99 is | ||

| + | generic (D : natural := 9; U : natural := 9); | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 3 - Conversor de BIN para SSD, com um parâmetro configurável '''ac_ccn''' para selecionar Anodo ou Catodo Comum. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component bin2ssd is | ||

| + | generic (ac_ccn : natural := 0); | ||

| + | port ( | ||

| + | bin_in : in std_logic_vector(3 downto 0); | ||

| + | ssd_out : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *O valor ac_ccn é utilizado para configurar o circuito entre ativo alto para display de catodo comum (ac_ccn=0), ou ativo baixo para display de anodo comum (ac_ccn=1). | ||

| + | |||

| + | |||

| + | O timer deve utilizar os componentes acima de modo a resultar em um RTL semelhante ao mostrado abaixo. | ||

| + | <center> | ||

| + | [[Arquivo:rtl_timer99sec.png | 600 px]] | ||

| + | </center> | ||

| + | * Simulação do timer com ModelSim. Na simulação definir o clk50MHz com duração de 10 ms. Faça uma simulação de pelo menos 60 segundos. | ||

| + | |||

| + | <center> | ||

| + | [[Arquivo:sim_timer99sec.png | 800 px]] | ||

| + | </center> | ||

| + | OBS: É recomendável inserir um sinal de RESET em todos os circuitos sequenciais e ao iniciar a simulação do circuito começar com RESET ativo durante 10 ps. | ||

| + | |||

| + | *Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. | ||

| + | :* Ao utilizar o kit DE2-115 da TERASIC, utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0-5[0-6]: PIN_G18 - PIN_H22 ...). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <code> | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | :*Ao utilizar o kit Mercúrio IV da MACNICA, utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <code> | ||

| + | set_location_assignment PIN_T1 -to clk50MHz | ||

| + | set_location_assignment PIN_V21 -to rst_in | ||

| + | set_location_assignment PIN_R5 -to ssd_D[0] | ||

| + | set_location_assignment PIN_T5 -to ssd_D[1] | ||

| + | set_location_assignment PIN_T3 -to ssd_D[2] | ||

| + | set_location_assignment PIN_T4 -to ssd_D[3] | ||

| + | set_location_assignment PIN_M6 -to ssd_D[4] | ||

| + | set_location_assignment PIN_N7 -to ssd_D[5] | ||

| + | set_location_assignment PIN_N6 -to ssd_D[6] | ||

| + | set_location_assignment PIN_V2 -to ssd_U[0] | ||

| + | set_location_assignment PIN_V1 -to ssd_U[1] | ||

| + | set_location_assignment PIN_U2 -to ssd_U[2] | ||

| + | set_location_assignment PIN_U1 -to ssd_U[3] | ||

| + | set_location_assignment PIN_Y2 -to ssd_U[4] | ||

| + | set_location_assignment PIN_Y1 -to ssd_U[5] | ||

| + | set_location_assignment PIN_W2 -to ssd_U[6] | ||

| + | set_location_assignment PIN_W1 -to clk_1seg | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | :* Análise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O [[Display de 7 segmentos]] da DE2-115 é do tipo cátodo comum, enquanto que na MERCURIO IV ele é do tipo ânodo comum. | ||

| + | |||

| + | ; Aula XX (19 Jun): | ||

| + | *Projeto a nível de Sistema. | ||

| + | FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | ||

| + | |||

| + | A instrução '''ASSERT''' é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a síntese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] assert condição_booleana | ||

| + | [report mensagem] | ||

| + | [severity nivel_severidade]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | A mensagem pode ser criada usando STRINGs que podem ser concatenadas. | ||

| + | |||

| + | O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [https://www.ics.uci.edu/~jmoorkan/vhdlref/assert.html]. | ||

| + | |||

| + | :* A '''FUNCTION''': declaração, uso, mapeamento posicional x nominal, PURE x IMPURE. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function nome_funçao (lista_parametros_entrada) return tipo_saida is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end function; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Uso de '''FUNCTION''' e '''ASSERT'''. | ||

| + | ::*No projeto do '''timer00_99''' | ||

| + | |||

| + | Abaixo segue um exemplo de cálculo do '''log2''' de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function log2c (n : integer) return integer is | ||

| + | variable m , p : integer; | ||

| + | begin | ||

| + | m := 0; | ||

| + | p : = 1; | ||

| + | while p < n loop | ||

| + | m : = m + 1; | ||

| + | p := p * 2; | ||

| + | end loop; | ||

| + | return m; | ||

| + | end log2c; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | |||

| + | |||

| + | ; Aula XX (23 Jun): | ||

| + | :*Uso de '''PROCEDURE'''. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end procedure; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::* Exemplo: Declaração de FUNCTION em ARCHITECTURE Ex.9.1 | ||

| + | ::* Exemplo: Declaração em FUNCTION PACKAGE Ex. 9.2 | ||

| + | ::* Exemplo: Declaração em FUNCTION ENTITY Ex. 9.3 | ||

| + | ::* Exemplo: min_max Ex.9.4 | ||

| + | ::* Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| + | :* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | ||

| + | |||

| + | |||

| + | ;Aula XX e XX (24 e 26 jun): | ||

| + | * Implementação de um serializador e um deserializador usando componentes. | ||

| + | |||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo '''generic N''' | ||

| + | entity div_clk is | ||

| + | entrada clk_in | ||

| + | saída clk_out | ||

| + | : Componente 2 - Registrador de deslocamento com entrada serial e paralelo e saída serial e paralelo com N FF, configurável pelo '''generic N''' | ||

| + | entity shift_reg is | ||

| + | entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in | ||

| + | saídas d_out[N-1..0], s_out | ||

| + | |||

| + | : Componente 3 - Porta paralela com N entradas, configurável pelo '''generic N'''. | ||

| + | entity parallel_reg is | ||

| + | entradas clk_in, rst, ena, d_in[N-1..0] | ||

| + | saídas d_out[N-1..0] | ||

| + | |||

| + | : Outros componentes necessários. | ||

| + | |||

| + | * Simular o serializador e deserializador com ModelSim. | ||

| + | * Implementar em um kit FPGA (Mercurio IV) usando o '''lab home office'''. | ||

| + | |||

| + | ;Aula XX XX (1 e 3 jul): | ||

| + | * Atividade extraclasse, ficou dividida em: | ||

| + | :*Equipe 1: Detalhar a '''architecture''' do componente '''div_clk''' e fazer sua simulação. | ||

| + | ::-Verificar se o '''clk_out''' está alto durante apenas um período do '''clk_in'''. Esse período deve ser entre duas bordas de descida do '''clk_in'''. | ||

| + | :*Equipe 1: Detalhar a '''architecture''' do componente '''parallel_reg''' e fazer sua simulação. | ||

| + | :*Equipe 2: Detalhar a '''architecture''' do componente '''shift_reg''', e fazer a simulação. | ||

| + | ::-Verificar a transferência dos dados da entrada serial para a saída paralela (função Desserializador). | ||

| + | ::-Verificar a transferência dos dados da entrada paralela para a saída serial (função Serializador). | ||

| + | ::-Verificar a transferência dos dados da entrada serial para a saída serial (função Delay). | ||

| + | ::-Verificar a transferência dos dados da entrada paralela para a saída paralela (função porta Paralela). | ||

| + | ::-Verificar a possibilidade de utilizar esse componente no lugar do '''parallel_reg'''. | ||

| + | * As equipes devem terminar de simular os componentes e integrá-los no projeto. | ||

| + | * Após a integração deverá ser feita a simulação do sistema completo. | ||

| + | * Mapear os pinos do FPGA para fazer o teste de funcionamento com um baud-rate de 1bit/s, entrada chaves, saídas leds. | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 7 - Maquinas de Estado Finitas=== | ||

| + | {{collapse top| expand=true | Unidade 7 - Maquinas de Estado Finitas}} | ||

| + | * 6 AULAS | ||

| + | |||

| + | ; Aula XX (7 ago): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O que é uma FSM - Finite State Machine | ||

| + | :* Modelo de FSM | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | -- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | -- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | -- ATTRIBUTE SYN_ENCODING OF state : TYPE IS "safe"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | pr_state <= nx_state; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value > ; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

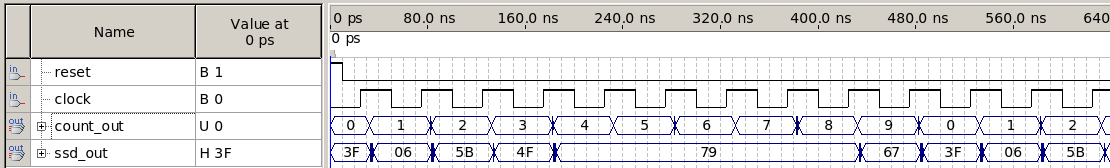

| + | :* Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1. | ||

| + | {{fig|7.1|Exemplo de diagrama de estados de uma FSM Fig11.1(a) e implementação em hardware da FSM Fig11.2(a)|Fig11_1_FSM.png|800 px|Figura 11.1 e 11.2 de <ref name="PEDRONI2010b"/>}} | ||

| + | :* Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados | ||

| + | :rst -> A -(x=0)-> A -(x=1)-> A -(x=2)-> B -(x=2)-> B -(x=0)-> C -(x=0)-> C -(x=2)-> C -(x=1)-> A -(x=2)-> B -(x=1)-> A. | ||

| + | :: Ver pag. 277 a 280 de <ref name="PEDRONI2010b"/> | ||

| + | :: Ver [https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/archives/quartusii_handbook_archive_131.pdf Quartus II Handbook Version 13.1: Manually Specifying Enumerated Types Using the enum_encoding Attribute, pag 16-37] sobre a atribuição manual do enum_encoding. | ||

| + | :: Note que o uso desse atributo faz com que o compilar do Quartus não reconheça a FSM, mas use logica regular para representar o sistema. | ||

| + | :: Ver [https://www.intel.com/content/dam/www/programmable/us/en/pdfs/literature/hb/qts/archives/quartusii_handbook_archive_131.pdf Quartus II Handbook Version 13.1: Safe State Machines, pag 16-38]. | ||

| + | |||

| + | ; Aula XX (11 ago): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* Máquina de vender doces | ||

| + | ::*Use o template da FSM para modelar o sistema mostrado na figurar a seguir. | ||

| + | |||

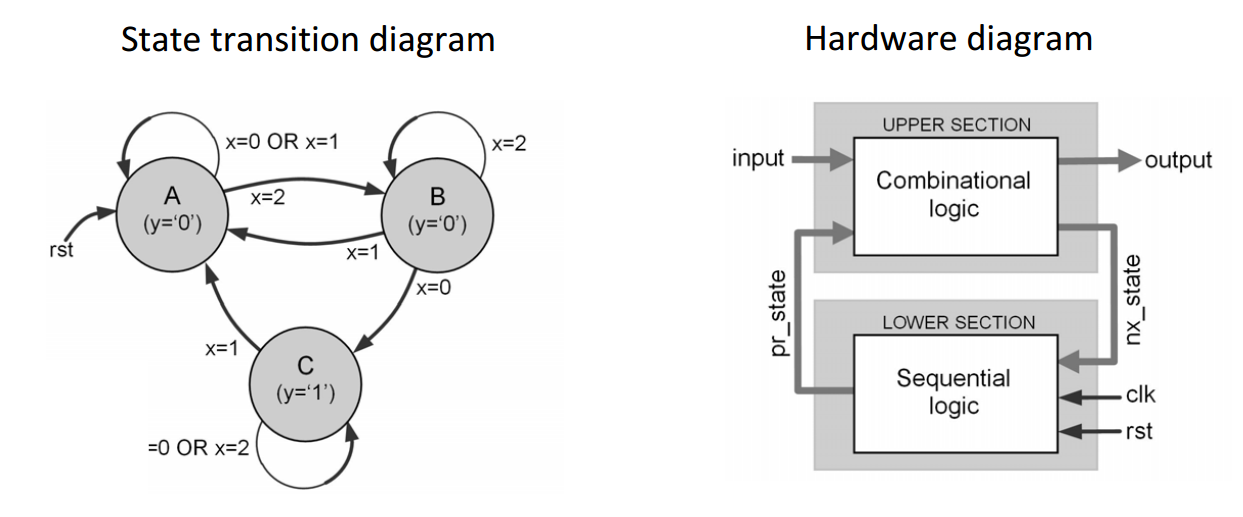

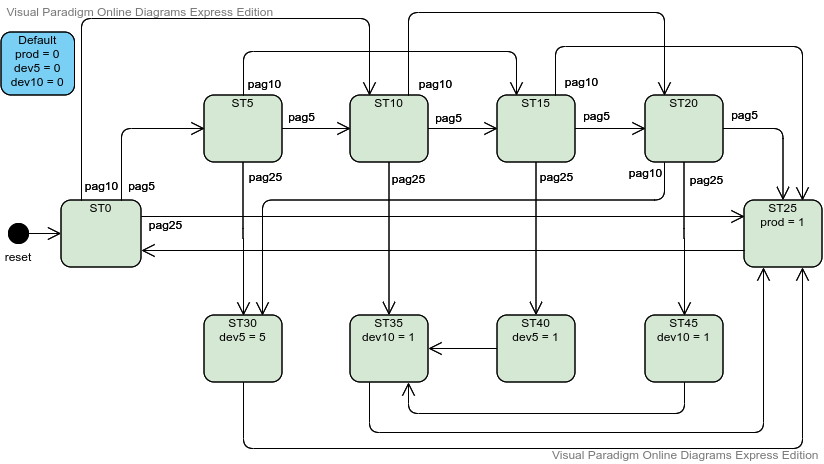

| + | {{fig|7.2|FSM - Máquina de vender doces (diagrama de estados)|FSM_MVD.png|800 px|Adaptado da Figura 11.3 de <ref name="PEDRONI2010b"/> }} | ||

| + | |||

| + | {{fig|7.3|FSM - Máquina de vender doces (diagrama de estados com default |FSM_MVD_default.png|800 px|}} | ||

| + | |||

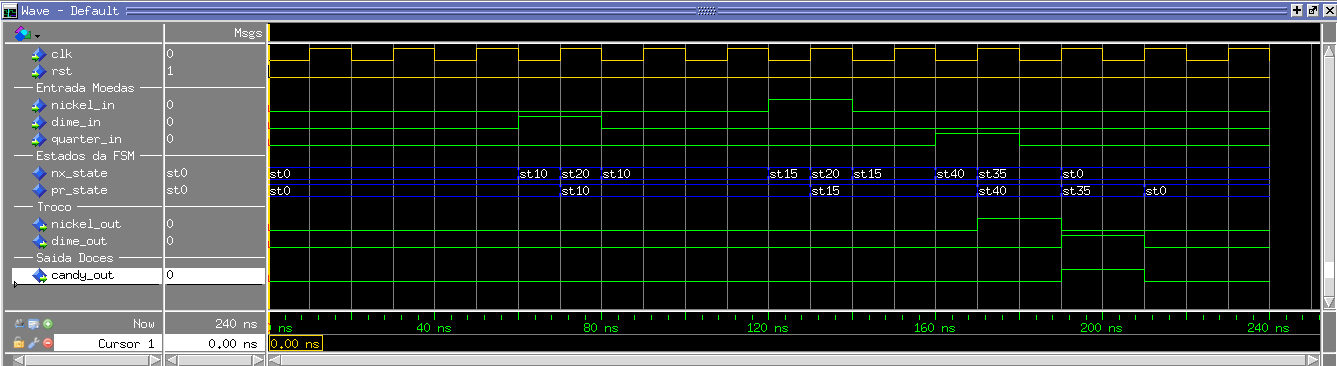

| + | ::*Simule a FSM com Modelsim utilizando um testbench em VHDL para gerar o teste mostrado na figura abaixo. | ||

| + | {{fig|7.4|FSM - Máquina de vender doces (simulação)|FSM_tb40.png|800 px|}} | ||

| + | |||

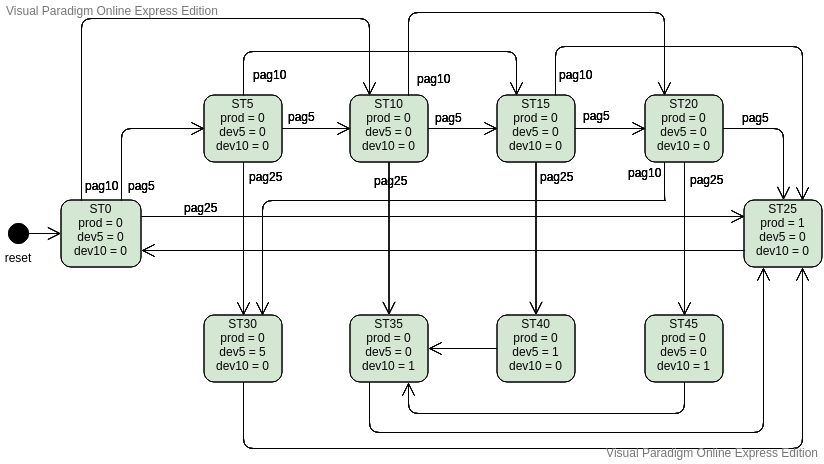

| + | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| + | :: Ver pag. 281 a 282 de <ref name="PEDRONI2010b"/> | ||

| + | :: '''Dica''': para desenhar a FSM recomendo utilizar um software on-line para tal finalidade. Por Ex. [https://online.visual-paradigm.com/pt/ Visual Paradigm]. | ||

| + | |||

| + | ; Aula XX (12 ago): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O problema de oscilando entre os estados em FSM. | ||

| + | |||

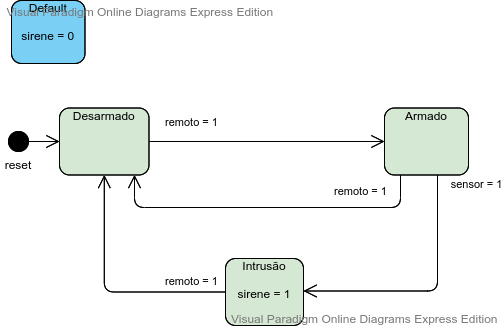

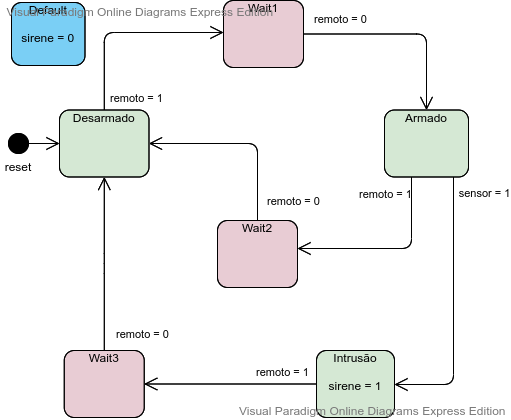

| + | {{fig|7.5| FSM - alarme (oscilando entre os estados quando remoto é 1) |alarme_erro.png|500 px|Adaptado de Figura 11.9(a) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

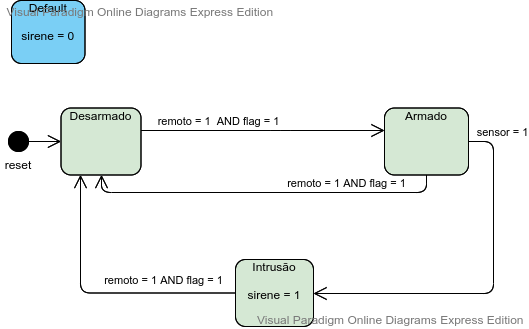

| + | ::* Solução através do uso de FLAG | ||

| + | |||

| + | {{fig|7.6| FSM - alarme (solução com flag) |alarme_flag.png|500 px|Adaptado de Figura 11.9(b) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | ::* Solução através do uso de estados de WAIT adicionais. | ||

| + | |||

| + | {{fig|7.7| FSM - alarme (solução com estados de WAIT) |alarme_wait.png|500 px|Adaptado de Figura 11.9(c) de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | :: Ver pag. 292 a 297 de <ref name="PEDRONI2010b"/> | ||

| + | *Exercício: Faça o download do arquivo simple_car_alarm.qar, disponível no Moodle da disciplina e realize as seguintes avaliações: | ||

| + | :#Perceba que existem 4 versões para o mesmo Alarme de Carro. Realize a simulação no ModelSim das 4 versões e perceba qual é a diferença de funcionamento desses circuitos. | ||

| + | :#Anote o número de elementos em cada versão. | ||

| + | :#Qual versão é a mais adequada na sua opinião? | ||

| + | :#Modifique a sua escolha para que o alarme não possa ser ativado se o "sensor" estiver em "1". | ||

| + | :#Analise o arquivo tb_vX.do e modifique-o para testar também essa nova condição. A simulação deve obrigatoriamente fazer o sistema passar por todos os estados e todas as transições. | ||

| + | :#Implemente a nova versão como uma nova arquitetura "fsm_v5", e escrever o arquivo de simulação "tbv5.do". | ||

| + | :#Salve as telas da simulação ("v5_sim.png"), tela da fsm ("v5_fsm.png"), tela do RTL ("v5_rtl.png"). | ||

| + | :#Acrescente os novos arquivos no projeto e salve o novo .qar | ||

| + | |||

| + | ;Aula XX (14 ago): | ||

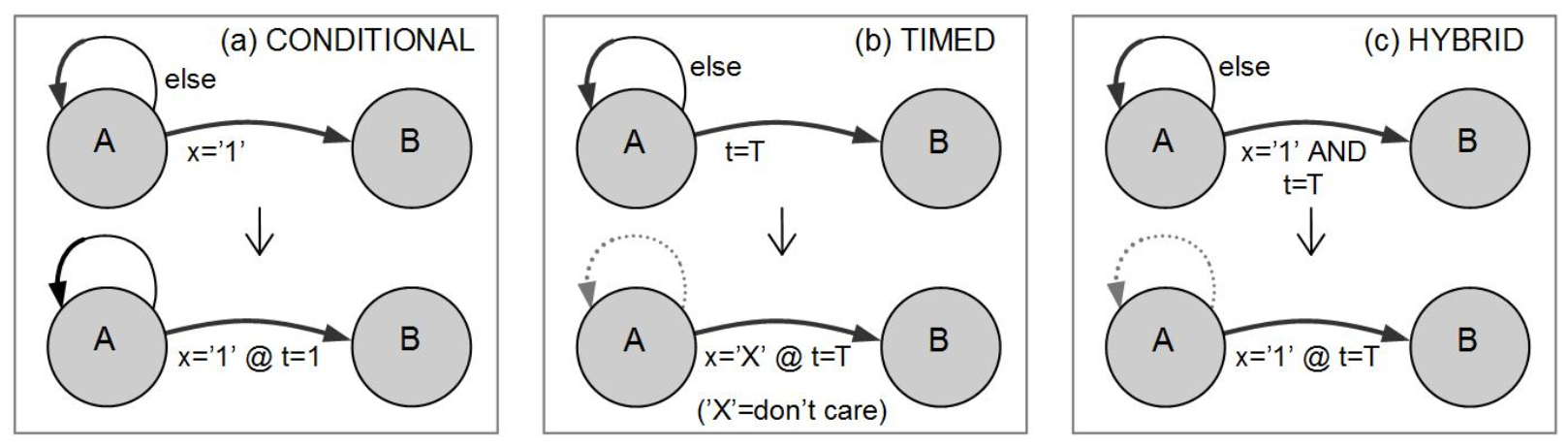

| + | * Projeto de FSM temporizadas (nas quais as transições são ativadas também pelo tempo). | ||

| + | {{fig|7.7| Tipos de FSM (Condicional, Temporizada e Hibrida) |FSM_type.png|800 px|Figura 11.12 de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | * Modelo de FSM temporizada | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | signal timer: integer range 0 to MAX; | ||

| + | -- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | -- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | variable count: integer range o to MAX; | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | count := 0; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | count := count + 1; | ||

| + | if (count >= timer) then | ||

| + | pr_state <= nx_state; | ||

| + | count := 0; | ||

| + | end if; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value >; | ||

| + | ------Valores default do timer------------ | ||

| + | timer <= <value>; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

| + | :Ver pag. 298 a 301 de <ref name="PEDRONI2010b"/> | ||

| + | ;Exercício: | ||

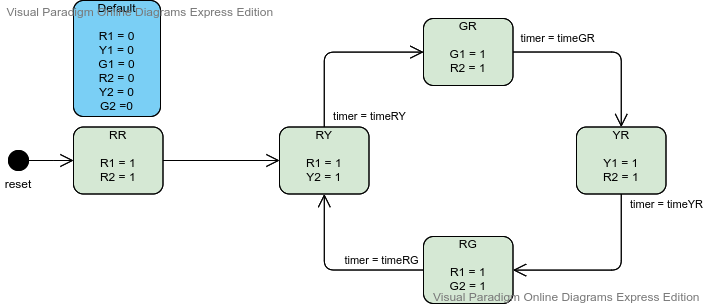

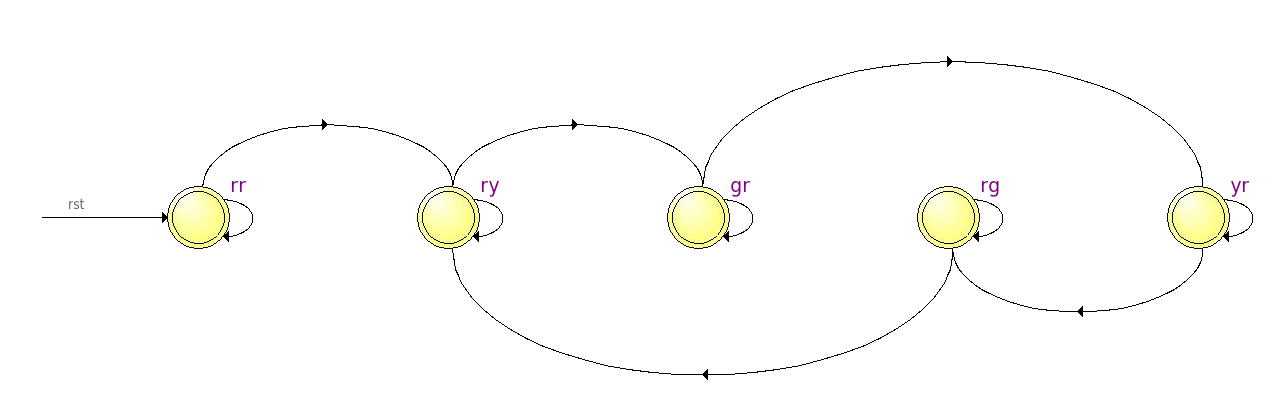

| + | * Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular da Figura 11.15 (pag. 304 de <ref name="PEDRONI2010b"/>). | ||

| + | {{fig|7.8| Diagrama de estados do controlador de semáforo |Semaforo_FSM_VD.png|800 px| Adaptado de Figura 11.15 de <ref name="PEDRONI2010b"/>}} | ||

| + | |||

| + | {{fig|7.9| Diagrama de estados do Quartus do controlador de semáforo |Semaforo_FSM.png|800 px|}} | ||

| + | |||

| + | * Para definir as temporizações utilize GENERICs que permitam instanciar diferentes semáforos em um projeto de controle de tráfego de uma avenida. | ||

| + | : Para uma instância do semáforo S1 use (timeRY = 2 segundos; timeGR = 40 segundos; timeYR = 2 segundos; timeRG = 15 segundos. | ||

| + | : Para uma instância do semáforo S2 use (timeRY = 5 segundos; timeGR = 90 segundos; timeYR = 5 segundos; timeRG = 30 segundos. | ||

| + | * Considere que o sinal de clock tem período de 1 segundo. | ||

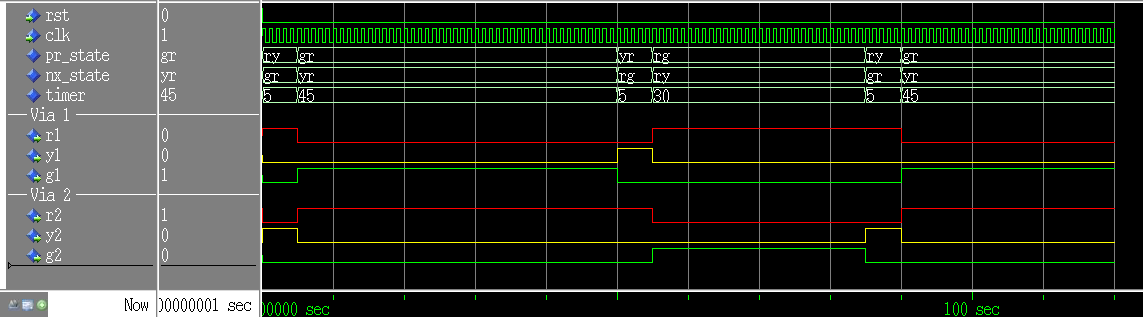

| + | * Realize a simulação dos semáforos S1 e S2, destacando as saídas com as cores correspondentes, conforme mostrado abaixo: | ||

| + | {{fig|7.10| Simulação do controlador de semáforo no Modelsim |Semaforo_ModelSim.png|800 px|}} | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top| expand=true | Unidade 8 - Testbench}} | ||

| + | |||

| + | ===Unidade 8 - Testbench=== | ||

| + | * 2 AULAS | ||

| + | ; Aula XX (18 ago): | ||

| + | |||

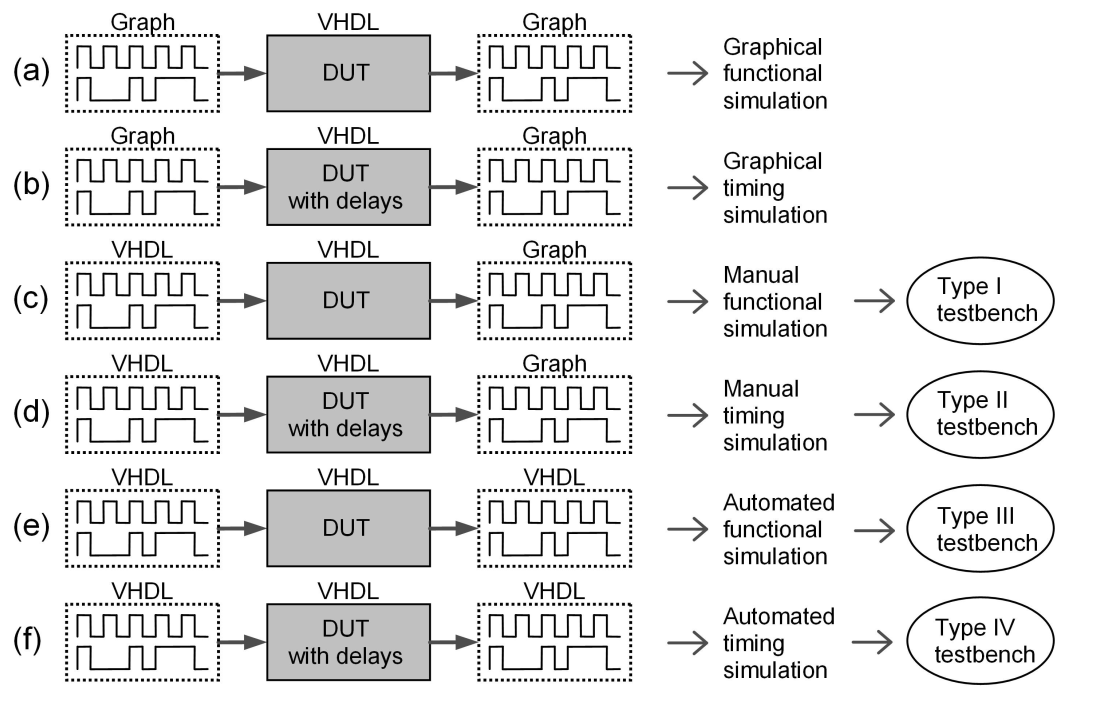

| + | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| + | :*Tipos de simulação: | ||

| + | ::1) simulação funcional (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003 | ||

| + | ::2) simulação temporal (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003 | ||

| + | ::3) simulação funcional (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - OK já visto | ||

| + | ::4) simulação temporal (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - Não será visto | ||

| + | ::5) simulação funcional (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade | ||

| + | ::6) simulação temporal (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade | ||

| + | ::7) simulação funcional (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ||

| + | ::8) simulação temporal (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ||

| + | |||

| + | {{fig|8.1| Tipos de Simulação |tipos_Simulacao.png|600 px|Figura 10.2 de <ref name="PEDRONI2010b"/> }} | ||

| + | |||

| + | :*Para usar o ModelSim 10.1d na CLOUD-IFSC(191.36.8.33) abra um terminal e digite: | ||

| + | /opt/altera/13.0sp1/modelsim_ae/bin/vsim | ||

| + | :* ou | ||

| + | vsim | ||

| + | :*Para usar o ModelSim 10.1d nos Laboratórios do IFSC campus São José abra um terminal e digite: | ||

| + | /opt/altera/13.0/quartus/modelsim_ae/linux/vsim | ||

| + | |||

| + | :*Ver também [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_func_sim.htm Performing a Functional Simulation with the ModelSim-Altera Software], e [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_timing_sim.htm Performing a Timing Simulation with the ModelSim-Altera Software]. | ||

| + | |||

| + | * Para analisar a diferença das simulações iremos utilizar como base a simulação da maquina de venda de doces Ex 11.1 | ||

| + | |||

| + | * Simulação de sistemas digitais com Modelsim e testbench em script .do. | ||

| + | |||

| + | * Script tb.do para um testbench para Modelsim. | ||

| + | <pre> | ||

| + | ################################# | ||

| + | ## FILE: tb.do | ||

| + | ################################# | ||

| + | vcom -93 -work work {../../vende_balas_FSM.vhd} | ||

| + | vsim work.vende_balas_FSM | ||

| + | |||

| + | add wave -position end -color gold sim:/vende_balas_FSM/rst | ||

| + | add wave -position end -color gold sim:/vende_balas_FSM/clk | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e5c | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e10c | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e25c | ||

| + | add wave -position end sim:/vende_balas_FSM/nx_state | ||

| + | add wave -position end sim:/vende_balas_FSM/pr_state | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/bala | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/d5c | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/d10c | ||

| + | configure wave -timelineunits sec | ||

| + | WaveRestoreZoom {0 ps} {25sec} | ||

| + | |||

| + | force -freeze sim:/vende_balas_FSM/rst 1 0, 0 0.1 sec | ||

| + | force -freeze sim:/vende_balas_FSM/clk 0 0, 1 {0.5 sec} -r 1sec | ||

| + | force -freeze sim:/vende_balas_FSM/e5c 0 0, 1 13sec, 0 14sec | ||

| + | force -freeze sim:/vende_balas_FSM/e10c 0 0, 1 16sec, 0 17sec, 1 23sec, 0 24sec | ||

| + | force -freeze sim:/vende_balas_FSM/e25c 0 0, 1 4sec, 0 5sec, 1 9sec, 0 10sec, 1 20sec, 0 21sec | ||

| + | run 25 sec | ||

| + | </pre> | ||

| + | |||

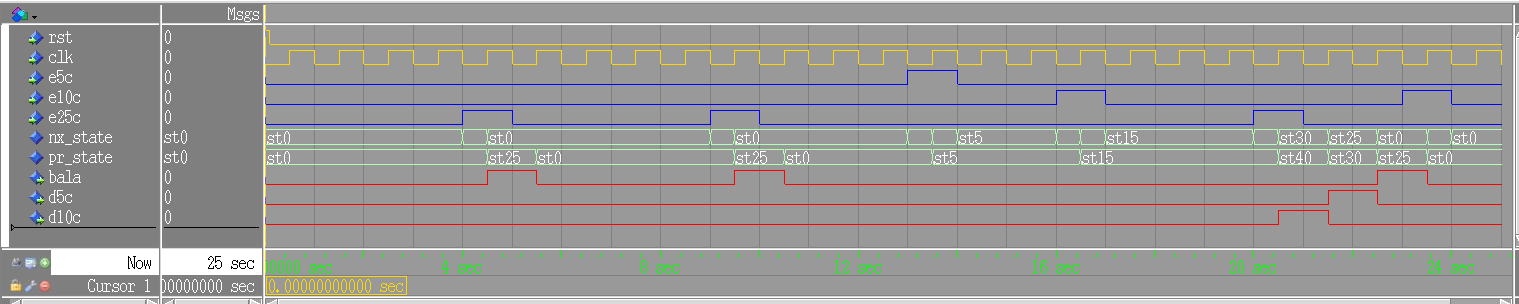

| + | *Resultado da simulação no Modelsim. Execute do tb.do | ||

| + | {{fig|8.2| Simulação com arquivo .do da FSM - maquina de vender doces |vende_balas_FSM_sim.png|800 px| }} | ||

| + | |||

| + | |||

| + | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| + | |||

| + | ::'''DICA''': Use o comando do Quartus II para gerar um template para o testbench. Selecione cada componente como TOP LEVEL e faça a ANÁLISE E SÍNTESE em seguida ('''Processing > Start > Start Test Bench Template Writer'''). | ||

| + | :* Criação de sinais para Test Bench em VHDL | ||

| + | |||

| + | {{collapse top | Geração de sinal de clock}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant tclk: time := 1 ns; | ||

| + | signal clk : std_logic := '0'; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO CONCORRENTE) | ||

| + | clk <= not clk after tclk; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | clk <= '1'; | ||

| + | wait for tclk; | ||

| + | clk <= '0'; | ||

| + | wait for tclk; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de sinal de reset}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant treset: time := 100 ps; | ||

| + | signal reset : std_logic; | ||

| + | |||

| + | -- RESET COM DURAÇÃO DE treset (COM CÓDIGO CONCORRENTE) | ||

| + | reset <= '1', '0' after treset; | ||

| + | |||

| + | -- RESET COM DURAÇÃO DE treset (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | reset <= '1'; | ||

| + | wait for treset; | ||

| + | reset <= '0'; | ||

| + | wait; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de uma sequencia binária}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant t_a: time := 100 ps; | ||

| + | constant Nbits: natural := 8; | ||

| + | signal a : std_logic_vector(Nbits-1 downto 0); | ||

| + | |||

| + | -- GERAÇÂO DO SINAL a = [0 1 2 3 4 ...] COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | for i in 0 to 2**Nbits-1 loop | ||

| + | a <= std_logic_vector(to_unsigned(i,Nbits)); | ||

| + | wait for t_a; | ||

| + | end loop; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de uma sequencia pseudoaleatória}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant t_a: time := 100 ps; | ||

| + | constant Nbits: natural := 8; | ||

| + | signal a : std_logic_vector(Nbits-1 downto 0) := (0 => '1', 3 => '1', others => '0'); | ||

| + | |||

| + | -- GERAÇÂO DO SINAL a COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL) | ||

| + | -- USANDO UM CONTADOR LFSR | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | for i in 0 to 2**Nbits-1 loop | ||

| + | a <= (a(0) xor a(2) xor a(3) xor a(4)) & a(Nbits-1 downto 1); -- para 8 bits | ||

| + | wait for t_a; | ||

| + | end loop; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | *Use o template gerado pelo Quartus e acrescente os estímulos indicados abaixo e realize a simulação usando agora o testbench em VHDL. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | |||

| + | -- constants | ||

| + | constant tclk: time := 0.5 sec; | ||

| + | constant treset: time := 100 ps; | ||

| + | constant talto: time := 1 sec; | ||

| + | |||

| + | -- RESET COM DURAO DE treset (COM CDIGO CONCORRENTE) | ||

| + | sim_rst: rst <= '1', '0' after treset; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CDIGO SEQUENCIAL) | ||

| + | sim_clk: PROCESS | ||

| + | BEGIN | ||

| + | clk <= '0'; | ||

| + | wait for tclk; | ||

| + | clk <= '1'; | ||

| + | wait for tclk; | ||

| + | END PROCESS; | ||

| + | -- GERAAO DO ESTIMULO "e5c"(COM CDIGO SEQUENCIAL) | ||

| + | sim_e5c: e5c <= '0', '1' after 13 sec, '0' after 14 sec; | ||

| + | |||

| + | -- GERAAO DO ESTIMULO "e5c"(COM CDIGO SEQUENCIAL) | ||

| + | sim_e10c: e10c <= '0', '1' after 16 sec, '0' after 17 sec, '1' after 23 sec, '0' after 24 sec; | ||

| + | |||

| + | -- GERAAO DO ESTIMULO "e25c"(COM CDIGO SEQUENCIAL) | ||

| + | |||

| + | -- sim_e25c: PROCESS | ||

| + | -- BEGIN | ||

| + | -- e25c <= '0'; | ||

| + | -- wait for 4 sec; | ||

| + | -- e25c <= '1'; | ||

| + | -- wait for 1 sec; | ||

| + | -- e25c <= '0'; | ||

| + | -- END PROCESS; | ||

| + | |||

| + | -- Os tempos neste caso sao os intervalos entre os eventos | ||

| + | -- No exemplo acima o SIGNAL e25c inicia com '0', muda para '1' apos 4 segundos, | ||

| + | -- e depois muda para '0' depois de mais 1 segundo | ||

| + | -- em CDIGO SEQUENCIALo mesmo estimulo seria gerado com: | ||

| + | -- sim_e25c: e25c <= '0', '1' after 4 sec, '0' after 5 sec; | ||

| + | |||

| + | sim_e25c: PROCESS | ||

| + | BEGIN | ||

| + | e25c <= '0'; | ||

| + | wait for 4 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 3 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 10 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 5 sec; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | ; Aula XX (19 ago): | ||

| + | * Testbench do tipo IV. | ||

| + | *Para exemplificar o uso de testbench que faz a verificação completa do resultado da simulação observe este exemplo gerado pelo Matlab/Simulink. [https://files.slack.com/files-pri/T014A4SEX7A-F019B7MS5J8/download/hdlcoder_sfir_fixed_stream.zip hdlcoder_sfir_fixed_stream.zip] | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Projeto Final (PF)=== | ||

| + | * O projeto final é uma atividade de avaliação desenvolvida em equipe, e consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a 40%do peso no conceito final. São avaliados no projeto final os quesitos: | ||

| + | :1) Sistema desenvolvido (projeto, simulação e realização, demonstração do hardware); | ||

| + | :2) Relatório com a documentação completa do projeto; | ||

| + | |||

| + | {{collapse top | expand = true | APF - Projeto Final - Sistema de controle de veículos e passagem de pedestre (Entrega e prazos ver Moodle)}} | ||

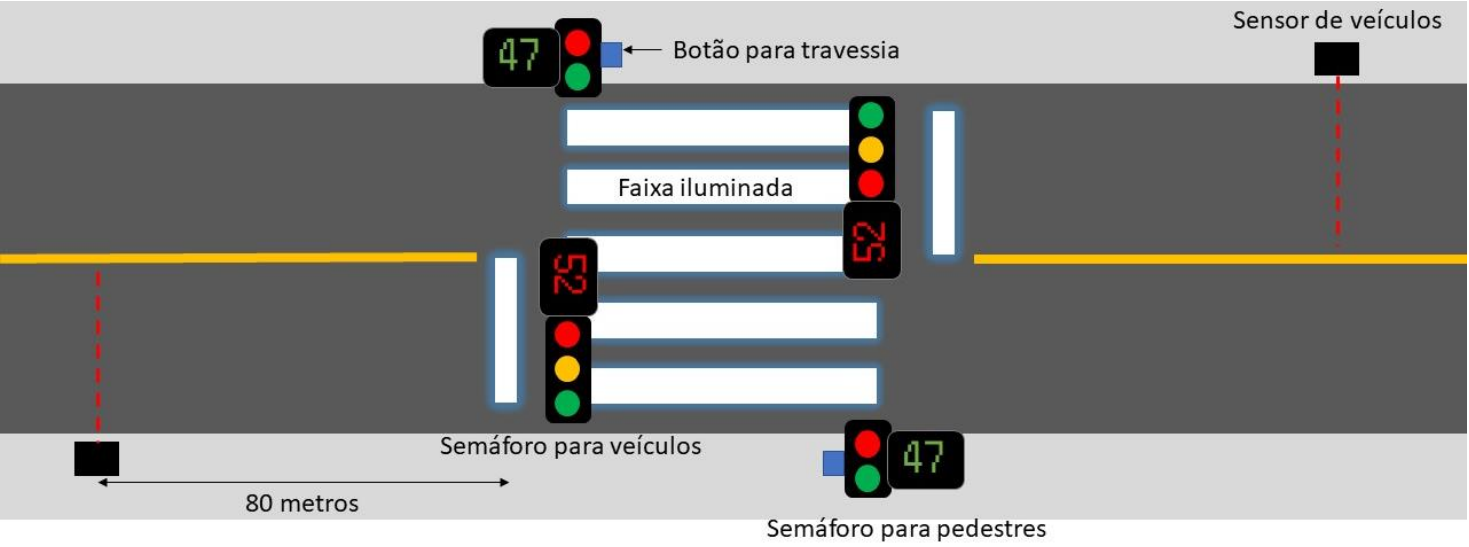

| + | * Cada equipe deverá desenvolver um sistema de controle de veículos e passagem de pedestre. | ||

| + | {{fig|PF.1| Sistema de controle de veículos e passagem de pedestre |SemaforoPedestre2018-2.png|1000 px| Imagem cedida por Yan Lucas Martins e Guilherme José Salles Vieira}} | ||

| + | |||

| + | * A descrição exata do funcionamento deve ser obtida com o cliente (professor) durante a entrevista de requisitos. | ||

| + | ;Alguns detalhes gerais que todos os projetos devem ter: | ||

| + | |||

| + | * O semáforo de passagem de pedestres é controlado por botões que os pedestres acionam do lado 1 ou 2 da passagem de pedestres para solicitar a travessia. Ao ser acionado o semáforo pode: | ||

| + | :1) liberar a passagem do pedestre após um tempo mínimo (T_min_libera) se não houver veículos circulando nas vias. | ||

| + | :2) ou aguardar até (T_espera), que deve ser configurável, caso haja veículos circulando em qualquer uma das vias. | ||

| + | :3) As vias são de mão unica podendo ser de 1 até 3 vias paralelas. | ||

| + | * Os grupos focais das vias de veículos devem ser do tipo simples ('''GFSv'''), com lâmpadas verde amarelo e vermelho. | ||

| + | * A passagem de pedestre tem além dos botões em cada lado da passagem; | ||

| + | :1) um sistema para iluminação noturna da passagem de pedestre, que liga apenas quando uma entrada de um foto sensor indica que já está escuro. | ||

| + | :2) dois grupos focais progressivos ('''GFPp''') com lâmpadas verdes e vermelhas e um display com dois dígitos para indicar o tempo restante no estado verde (contagem regressiva); | ||

| + | :3) um sistema que emite sons indicativos para auxilio aos deficientes visuais. Deverá haver uma cadencia de som para indicar a espera, e outra para indicar que a travessia está liberada. Por sugestão dos engenheiros executores, pode ser implementado uma 3ª cadência para informar que o tempo de travessia está se esgotando. | ||

| + | |||

| + | * A iluminação da passagem de pedestre deve acender assim que um botão for acionado e apagar somente (T_pos_lux) depois de o '''GFPp''' passar de verde para vermelho. | ||

| + | |||

| + | * O tempo de passagem do pedestre (T_travessia) é configurável (default = 5s x Nvias). | ||

| + | * Se não houver acionamento do botão de solicitação de passagem do pedestre, as vias 1 e 2 devem permanecer sempre em verde. | ||

| + | * O sistema de controle do semáforo deverá ser descrito através de máquinas de estado finita (FSM). | ||

| + | :*Para a FSM sugere-se utilizar GENERIC para definir os tempos tempos. | ||

| + | :* O sistema de controle das FSM será baseado no valor de um timer de segundos externo a FSM (conforme mostrado em aula). | ||

| + | * O sistema será implementado no kit FPGA DE2-115 ou Mercúrio IV. | ||

| + | * Provavelmente irei disponibilizar mini semáforos para acionamento via GPIO. | ||

| + | * As chaves serão usadas as do kit ou chaves externas conectadas via GPIO. Use no mínimo uma para cada uma das seguintes funções. | ||

| + | :*Sensor de Escuro|Claro. | ||

| + | :*Botão do lado direito para Pedestre. | ||

| + | :*Botão do lado esquerdo para Pedestre. | ||

| + | :*1 Sensor de veículo para cada via monitorada. | ||

| + | |||

| + | *Para sinalizar as saídas do sistema podem ser usados os leds disponíveis ou pinos da GPIO para acionar leds externos. | ||

| + | * Os sinais de relógio necessários deverão ser obtidos a partir do sinal de clock da placa de 50MHz. Durante as simulações esse circuito deverá ter seu valor alterado de modo a viabilizar a simulação. | ||

| + | * O arquivo QAR do projeto, e os arquivos .do e o testbench .vht para o MODELSIM devem ser enviados antecipadamente; | ||

| + | * Escreva um relatório técnico contendo os resultados em no máximo 20 paginas A4. O relatório além das tabelas com os dados de frequência máxima, número de componente, número de pinos, deverá conter a figura dos circuitos RTL da ENTITY top level com uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. A descrição da função dos pinos no Kit utilizado também deve ser feita. | ||

| + | |||