Mudanças entre as edições de "DLP29006-Engtelecom(2019-2) - Prof. Marcos Moecke"

| (71 revisões intermediárias por 3 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

{{DivulgueEngtelecom}} | {{DivulgueEngtelecom}} | ||

==Registro on-line das aulas== | ==Registro on-line das aulas== | ||

| − | |||

===Unidade 1 - Introdução a disciplina=== | ===Unidade 1 - Introdução a disciplina=== | ||

* 3 AULAS | * 3 AULAS | ||

| + | |||

| + | {{collapse top|Unidade 1 - Introdução a disciplina}} | ||

;Aula 1 (29 jul): | ;Aula 1 (29 jul): | ||

| Linha 76: | Linha 77: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

| − | |||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

* 3 AULAS | * 3 AULAS | ||

| + | {{collapse top| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} | ||

;Aula 4 (5 ago): | ;Aula 4 (5 ago): | ||

| Linha 86: | Linha 86: | ||

* Estrutura do código VHDL | * Estrutura do código VHDL | ||

:* Declaração das bibliotecas e pacotes '''LIBRARY''' / '''PACKAGE''' | :* Declaração das bibliotecas e pacotes '''LIBRARY''' / '''PACKAGE''' | ||

| − | < | + | <syntaxhighlight lang=vhdl> |

library library_name; | library library_name; | ||

use library_name.package)name.all; | use library_name.package)name.all; | ||

| − | </ | + | </syntaxhighlight> |

:* '''ENTITY''' | :* '''ENTITY''' | ||

| − | < | + | <syntaxhighlight lang=vhdl> |

entity entity_name is | entity entity_name is | ||

[generic ( | [generic ( | ||

| Linha 108: | Linha 108: | ||

statement_part] | statement_part] | ||

end [entity] [entity_name]; | end [entity] [entity_name]; | ||

| − | </ | + | </syntaxhighlight> |

:* '''ARCHITECTURE''' | :* '''ARCHITECTURE''' | ||

| − | < | + | <syntaxhighlight lang=vhdl> |

architecture arch_name of entity_name is | architecture arch_name of entity_name is | ||

[declarative_part] | [declarative_part] | ||

| Linha 117: | Linha 117: | ||

statement_part | statement_part | ||

end [architecture] [arch_name]; | end [architecture] [arch_name]; | ||

| − | </ | + | </syntaxhighlight> |

| + | |||

* Exemplo - Declaração de uma porta NAND em VHDL | * Exemplo - Declaração de uma porta NAND em VHDL | ||

| + | |||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

library std; | library std; | ||

| Linha 428: | Linha 430: | ||

--> | --> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

| − | |||

===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ||

* 7 AULAS | * 7 AULAS | ||

| + | |||

| + | {{collapse top | Unidade 3 - Tipos de Dados e Operadores em VHDL}} | ||

| + | |||

;Aula 7 (19 ago): | ;Aula 7 (19 ago): | ||

*Comentários no código (duplo traço --) | *Comentários no código (duplo traço --) | ||

| Linha 472: | Linha 475: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | constant <constant_name> : <type> := <constant_value>; | |

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ||

| + | A '''constant''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, PACKAGE_BODY, BLOCK, GENERATE, PROCESS, FUNCTION e PROCEDURE. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | -- Signal sem valor default | |

| + | -- Para atribuir um valor a um signal use "<=" como operador. | ||

| + | |||

| + | signal <name> : <type>; | ||

| + | |||

| + | -- Signal com valor default | ||

| + | signal <name> : <type> := <default_value>; | ||

| + | |||

| + | -- Declarações comuns de signals | ||

| + | |||

| + | signal <name> : std_logic; | ||

| + | signal <name> : std_logic_vector(<msb_index> downto <lsb_index>); | ||

| + | signal <name> : integer; | ||

| + | signal <name> : integer range <low> to <high>; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ||

| + | O '''signal''' pode ser declarado na parte declarativa da ENTITY, ARCHITECTURE, PACKAGE, BLOCK, GENERATE. Os sinais não podem ser declarados no código sequencial (PROCESS, FUNCTION e PROCEDURE), mas podem ser usados. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| − | + | -- Variables devem ser declarada em process ou subprogramas. | |

| + | -- Para atribuir um valor a um variable use "<=" como operador. | ||

| + | |||

| + | -- Variable sem valor default. | ||

| + | variable <name> : <type>; | ||

| + | |||

| + | -- Variable com valor default. | ||

| + | variable <name> : <type> := <default_value>; | ||

| + | |||

| + | -- Declarações comuns de variables | ||

| + | variable <name> : std_logic; | ||

| + | variable <name> : std_logic_vector(<msb_index> downto <lsb_index>); | ||

| + | variable <name> : integer; | ||

| + | variable <name> : integer range <low> to <high>; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | ||

| + | O '''variable''' (variável) só pode ser declarada e usada dentro do escopo no código sequencial (PROCESS, FUNCTION e PROCEDURE). | ||

:*Palavra chave '''OTHERS''' para formação de agregados | :*Palavra chave '''OTHERS''' para formação de agregados | ||

| Linha 1 014: | Linha 1 046: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 4 - Código Concorrente=== | ||

| + | * 4 AULAS | ||

| + | |||

| + | {{collapse top| Unidade 4 - Código Concorrente}} | ||

| + | |||

| + | ;Aula 17 (11 set): | ||

| + | *Código Concorrente. | ||

| + | :* Uso de Operadores | ||

| + | :* instrução WHEN-ELSE (WHEN) | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | <optional_label>: <target> <= | ||

| + | <value> when <condition> else | ||

| + | <value> when <condition> else | ||

| + | <value> when <condition> else | ||

| + | ... | ||

| + | <value>; | ||

| + | </syntaxhighlight> | ||

| + | ::*Importante: O último ELSE deve cobrir todos os demais valores para evitar a criação de LATCHES. | ||

| + | ::* No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Conditional Signal Assignment]''' | ||

| + | |||

| + | :* instrução WITH-SELECT-WHEN (SELECT) | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | <optional_label>: with <expression> select | ||

| + | <target> <= | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | ... | ||

| + | <value> when others; | ||

| + | </syntaxhighlight> | ||

| + | ::*Importante: O valor deve cobrir todas as demais possibilidades usando WHEN OTHERS para evitar a criação de LATCHES. | ||

| + | ::* No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Selected Signal Assignment]'''. '''Mas ATENÇÃO, faltam as virgulas após cada escolha'''. | ||

| + | |||

| + | :* Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com portas, com WHEN-ELSE, com WITH-SELECT) | ||

| + | ::Verifique os três circuitos considerando as entradas x0 a x3 e a saída y com apenas um elemento. | ||

| + | ::Modifique os circuitos para que tenham as entradas x0 a x3 e a saída y com 4 elementos. | ||

| + | :::No caso do uso de WHEN-ELSE e WITH-SELECT é só alterar o tamanho dos vetores STD_LOGIC_VECTOR. | ||

| + | :::Qual é a solução para a descrição com portas? | ||

| + | :* Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | CONFIGURATION which_mux OF mux IS | ||

| + | FOR Operator_only END FOR; | ||

| + | -- FOR with_WHEN END FOR; | ||

| + | -- FOR with_SELECT END FOR; | ||

| + | END CONFIGURATION; | ||

| + | </syntaxhighlight> | ||

| + | ::Ver pag. 121 a 127 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | |||

| + | ;Aula 18 (13 set): | ||

| + | |||

| + | :* Uso da instrução FOR-GENERATE | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | label: FOR identificador IN faixa GENERATE | ||

| + | [Parte_Declarativa | ||

| + | BEGIN] | ||

| + | Instruções_concorrentes | ||

| + | ... | ||

| + | END GENERATE [label]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :*Exercício - Dado o somador para 4 entradas a(0) até a(3), use o FOR-GENERATE para torná-lo um somador para N entradas. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --------------------- | ||

| + | -- FILE my_pkg.vhd -- | ||

| + | --------------------- | ||

| + | library ieee; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | |||

| + | package my_pkg is | ||

| + | type a_slv is array(natural range <>) of std_logic_vector (3 downto 0); | ||

| + | end package; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --------------------------- | ||

| + | -- FILE vector_adder.vhd -- | ||

| + | --------------------------- | ||

| + | library ieee work; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | use ieee.numeric_std.all; | ||

| + | use work.my_pkg.all; | ||

| + | |||

| + | entity vector_adder is | ||

| + | generic (N : natural := 4); | ||

| + | port ( | ||

| + | a : in a_slv (0 to N-1); | ||

| + | soma : out std_logic_vector (3 downto 0)); | ||

| + | end entity; | ||

| + | |||

| + | -- Versão que realiza a soma diretamente, mas que precisa modificar o código de acordo com o número de entradas. | ||

| + | |||

| + | architecture ifsc_v1 of vector_adder is | ||

| + | signal soma_sig : signed(3 downto 0); | ||

| + | begin | ||

| + | soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2)) + signed(a(3)); | ||

| + | soma <= std_logic_vector(soma_sig); | ||

| + | end architecture; | ||

| + | |||

| + | -- Versão que realiza a soma usando um FOR GENERATE | ||

| + | architecture ifsc_v2 of vector_adder is | ||

| + | |||

| + | begin | ||

| + | |||

| + | |||

| + | end architecture; | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --------------------------- | ||

| + | -- FILE vector_adder.vhd -- | ||

| + | --------------------------- | ||

| + | configuration ifsc_cfg of vector_adder is | ||

| + | -- for ifsc_v1 end for; | ||

| + | for ifsc_v2 end for; | ||

| + | end configuration; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :*Ver pag. 127 a 134 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ;Aula 19 (16 set): | ||

| + | *Código Concorrente. | ||

| + | :*Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU). (Ver [https://moodle.sj.ifsc.edu.br/pluginfile.php/13347/mod_forum/attachment/3222/Captura%20de%20tela%20em%202019-09-16%2007-59-43.png?forcedownload=1 diagrama e tabela funcional no Moodle]), [https://moodle.sj.ifsc.edu.br/mod/forum/discuss.php?d=1368]. | ||

| + | |||

| + | |||

| + | ::*Fazer as seguintes alterações do código da ALU: | ||

| + | :::* Inclusão de um sinal que indica "erro" quando ocorre ''overflow''/''underflow'' nas operações de soma, incremento ou decremento. | ||

| + | :::* Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro. | ||

| + | :::* Teste da ALU usando simulação funcional. | ||

| + | |||

| + | ;Aula 20 (18 set): | ||

| + | :*Exemplo 5.4 - Decodificador genérico de endereços. | ||

| + | |||

| + | * Implementação de conversor Binário para Gray | ||

| + | :*ver detalhes [[Código Gray]] | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity bin2gray is | ||

| + | |||

| + | generic (N : natural := 4 ) | ||

| + | |||

| + | port | ||

| + | ( | ||

| + | b : in std_logic_vector(____) | ||

| + | g : out std_logic_vector(____) | ||

| + | ) | ||

| + | |||

| + | end entity | ||

| + | |||

| + | architecture ifsc of ____ is | ||

| + | begin | ||

| + | |||

| + | |||

| + | end architecture | ||

| + | </syntaxhighlight> | ||

| + | * Implementação de conversor Gray para Binário | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity gray2bin is | ||

| + | generic (N : natural := 4 ) | ||

| + | port | ||

| + | ( | ||

| + | g : in std_logic_vector(____) | ||

| + | b : out std_logic_vector(____) | ||

| + | ) | ||

| + | end entity | ||

| + | |||

| + | architecture ifsc of ____ is | ||

| + | begin | ||

| + | |||

| + | end architecture | ||

| + | </syntaxhighlight> | ||

| + | * AE2 - Atividade Extra Classe: Implemente um circuito de incrementador Gray | ||

| + | :*Implemente um incrementador Gray, o qual dada uma entrada de N bits em código Gray fornece na saída o valor seguinte em [[Código Gray]]. | ||

| + | ::Use como base o modelo de entidade abaixo: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity inc_gray is | ||

| + | port | ||

| + | ( | ||

| + | gray_in : in std_logic_vector(____) | ||

| + | bray_out : out std_logic_vector(____) | ||

| + | ) | ||

| + | end entity | ||

| + | |||

| + | architecture ____ of inc_gray is | ||

| + | begin | ||

| + | |||

| + | end architecture | ||

| + | </syntaxhighlight> | ||

| + | ::Por exemplo: se a entrada de 4 bits for 2 = "0011" a saída será o 3 = "0010". | ||

| + | :* Mostre que o circuito funciona, fazendo a sua simulação funcional (use o QSIM ou Modelsim). | ||

| + | :* Prazo de execução e detalhes podem ser visto na [https://moodle.sj.ifsc.edu.br/course/index.php?categoryid=177 plataforma Moodle da disciplina]. | ||

| + | |||

| + | |||

| + | ;Aula 21 (23 set): | ||

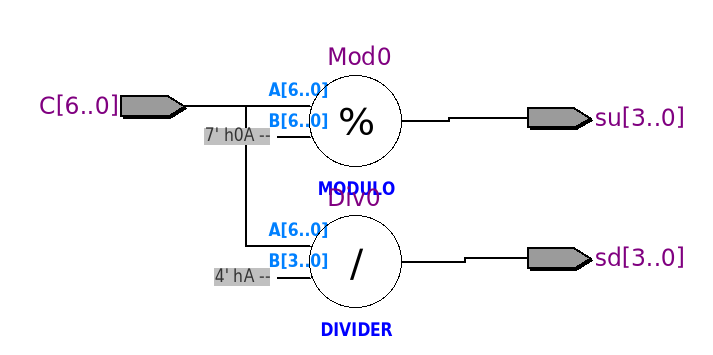

| + | * Implementação de circuitos aritméticos com operadores. | ||

| + | :* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar a biblioteca ''numeric_std''. | ||

| + | :* Também é fundamental considerar a faixa de valores coberta por <math> N </math> bits. Para tipos '''UNSIGNED''' a faixa é de <math> 0 </math> até <math> 2^{N}-1 </math>, enquanto que para '''SIGNED''' a faixa é de <math> -2^{N-1} </math> até <math> 2^{N-1}-1 </math>. Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED. | ||

| + | :* Para uso adequado dos operadores também é necessário considerar o tamanho (número de bits) requerido para o resultado em função do tamanho dos operandos. | ||

| + | ::*Ver a declaração das funções "+", "-", "*" e "/" no PACKAGE [[Numeric std.vhd]] | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function "+" (L, R: UNSIGNED) return UNSIGNED; | ||

| + | -- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0). | ||

| + | -- Result: Adds two UNSIGNED vectors that may be of different lengths. | ||

| + | function "-" (L, R: UNSIGNED) return UNSIGNED; | ||

| + | -- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0). | ||

| + | -- Result: Subtracts two UNSIGNED vectors that may be of different lengths. | ||

| + | function "*" (L, R: UNSIGNED) return UNSIGNED; | ||

| + | -- Result subtype: UNSIGNED((L'LENGTH+R'LENGTH-1) downto 0). | ||

| + | -- Result: Performs the multiplication operation on two UNSIGNED vectors | ||

| + | -- that may possibly be of different lengths. | ||

| + | function "/" (L, R: UNSIGNED) return UNSIGNED; | ||

| + | -- Result subtype: UNSIGNED(L'LENGTH-1 downto 0) | ||

| + | -- Result: Divides an UNSIGNED vector, L, by another UNSIGNED vector, R. | ||

| + | -- NOTE: If second argument is zero for "/" operator, a severity level of ERROR is issued. | ||

| + | </syntaxhighlight> | ||

| + | ::* Para operações de "+" ou "-": O tamanho do resultado é igual ao tamanho do maior operando. | ||

| + | :::Exemplo: r[7..0] = a[7..0] + b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8 bits. | ||

| + | ::* Para a operações "*": O tamanho do resultado é igual a soma do tamanho dos dois operandos. | ||

| + | :::Exemplo: r[12..0] = a[7..0] * b[4..0]; a -> 8 bits; b -> 5 bits então r -> 8+5 = 13 bits. | ||

| + | ::* Para "/": O tamanho do resultado é igual ao tamanho do numerador. | ||

| + | :::Exemplo: r[5..0] = a[5..0] / b[8..0]; a -> 6 bits; b -> 9 bits então r -> 6 bits. | ||

| + | :* No caso da operações de "*" e "/" não ocorre ''overflow'', no entanto no caso da "+" e "-", o ''overflow/underflow'' pode ocorrer e precisa ser tratado. Isso pode ser feito acrescentando um bit adicional a saída para conter o ''overflow'' ou então sinalizar a sua ocorrência com um bit na saída do circuito. Note que no caso em que ocorrem sucessivas somas, é impraticável ficar aumentando o número de bits para evitar o ''overflow'', de modo que a sinalização do ''overflow'' ou uso de escalas, ou representação em ponto fixo ou ponto flutuante podem ser as soluções a serem adotadas. | ||

| + | :* No caso das operações de "+" e "-" também pode ser necessário tratar os sinais de ''carry in'' e ''carry out'', que permitem ampliar o tamanho de um somador realizando a sua conexão em cascata, ao mesmo tempo que tratam o ''overflow''. | ||

| + | |||

| + | *Exemplo 5.7 - Somador/Subtrator Recomendado. | ||

| + | :* Implementar o circuito com 4 bits na entrada e 5 bits na saída (com signed e unsigned) | ||

| + | :* Implementar o circuito com 4 bits na entrada e 4 bits na saída, e uma saída de cout para soma e para subtração | ||

| + | :* Implementar um circuito multiplicador com 4 bits na entrada e 7 bits na saída. | ||

| + | :* em todos os circuitos acima onde possa ocorrer overflow(underflow), acrescentar um circuito para saturar a saída no máximo(mínimo). | ||

| + | :* em todos os circuitos acima onde possa ocorrer overflow(underflow), acrescentar um bit de saída que indique quando o resultado está com erro. | ||

| + | |||

| + | :*Ver pag. 139 a 140 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 5 - Código Sequencial=== | ||

| + | * 7 AULAS | ||

| + | {{collapse top| Unidade 5 - Código Sequencial}} | ||

| + | |||

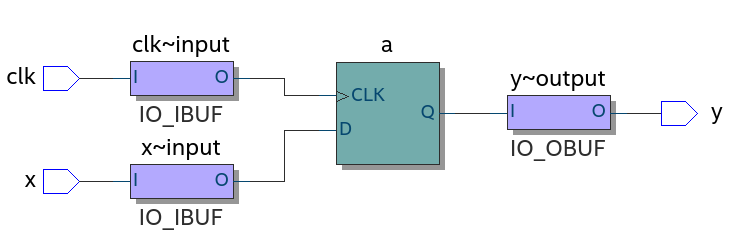

| + | ;Aula 23 (30 set): | ||

| + | *Código Sequencial. | ||

| + | :*Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial | ||

| + | :*Diferenças entre os objetos SIGNAL e VARIABLE | ||

| + | :*Tipos de elementos de memória: Latch x Flip-flop | ||

| + | ::* Latch D | ||

| + | ::* Flip-flop tipo D com reset assíncrono e com reset (clear) síncrono | ||

| + | :*Seção de código sequencial '''PROCESS''': lista de sensibilidade | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] PROCESS [(lista_de_sensibilidade)] [IS] | ||

| + | [parte_declarativa] | ||

| + | BEGIN | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END PROCESS [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | :*Instrução '''IF''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] IF condição THEN | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | ELSIF condição THEN | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | ELSE | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END IF [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | :*Exemplos: | ||

| + | ::* DFFs com Reset Assincrono e Reset Sincrono, com Enable, com Preset (Variação Ex 6.1). | ||

| + | ::* Comparar com Latch (sem clk'event). | ||

| + | ::* Simulação funcional do DFFs e do Latch | ||

| + | :*Ver pag. 161 a 160 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | |||

| + | ;Aula 24 (02 out): | ||

| + | *Código Sequencial. | ||

| + | :* Contador Básico 0-N (baseado no Ex.6.2) | ||

| + | |||

| + | |||

| + | ;Aula 25 (04 out - reposição do dia 27 set): | ||

| + | * Avaliação A1 - UN2, UN3, UN4 | ||

| + | |||

| + | ;Aula 26 (07 out): | ||

| + | *Código Sequencial. | ||

| + | :* Registrador de deslocamento (Ex.6.3) | ||

| + | ::Versão 1 - Implementação com for generate da conexão de FF D. | ||

| + | ::Versão 2 - Implementação com formação de agregado via concatenação. | ||

| + | |||

| + | ;Aula 27 (09 out) | ||

| + | |||

| + | *Código Sequencial | ||

| + | :*Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | ||

| + | ::*LOOP incondicional: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] LOOP | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*FOR-LOOP: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] FOR identificador IN faixa LOOP | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*WHILE-LOOP: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira | ||

| + | afirmação_sequencial; | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*LOOP com EXIT: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] [FOR identificador IN faixa] LOOP | ||

| + | afirmação_sequencial; | ||

| + | EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP" | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*LOOP com NEXT: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] [FOR identificador IN faixa] LOOP | ||

| + | afirmação_sequencial; | ||

| + | NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP" | ||

| + | -- e incrementa o "identificador". | ||

| + | afirmação_sequencial; | ||

| + | ... | ||

| + | END LOOP [rótulo]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Exemplos: | ||

| + | ::* Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) - apenas analisar | ||

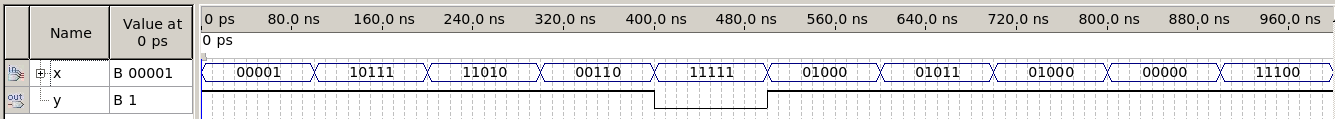

| + | ::* Leading Zeros (LOOP com EXIT) (Ex 6.5) - obter ocódigo no Moodle; fazer a síntese do circuito; fazer simulação no Modelsim; analisar a forma como o compilador implementou o incrementador. | ||

| + | :*Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ;Aula 28 (11 out): | ||

| + | :*Instrução '''CASE''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] CASE expressão IS | ||

| + | WHEN valor => atribuições; -- valor único | ||

| + | ... | ||

| + | WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores | ||

| + | ... | ||

| + | WHEN valor1 TO valor2 => atribuições; -- faixa de valores | ||

| + | ... | ||

| + | |||

| + | END CASE; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :*Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | ||

| + | ::Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT. | ||

| + | ::Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ||

| + | |||

| + | :* Timer de 0 a 9 segundos com saída SSD (Ex 6.6). | ||

| + | ::* Unir o código de um contador de 0 a 9 (código sequencial), e um conversor de binário para sete segmentos em código sequencial (usando CASE). | ||

| + | ::* Depois acrescentar um circuito que permita obter um clock com período de 1 segundo, a partir de um sinal de clock com frequência de fclk = 50MHz. | ||

| + | ::* Implementar no FPGA o circuito com contador de 0 a 9 segundos com saída SSD e clk de entrada de 50MHz. | ||

| + | :::*PROBLEMA: Uso de um período de clock de 20 ns => 50 MHz, verificar a impossibilidade prática de uma simulação deste circuito (1 segundo => 5 minutos de simulação), devido ao tamanho do contador (count1) que conta de 0 a 50M-1. | ||

| + | :::*SOLUÇÃO: modificar o contador para um valor máximo menor (0 a 50-1). Notar que a simulação é extremamente rápida neste caso. | ||

| + | :::*Após verificar que o circuito funciona "simulado", configurar o FPGA do kit Mercúrio IV para implementar este circuito. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. Utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | :::* Como o conversor de binário para ssd realizado anteriormente tinha lógica negativa ('0' acende, '1' apaga), será necessário inverter todas as saídas | ||

| + | ssd_out <= not ssd; | ||

| + | :::*Se quiser usar um led na matriz de led é necessário colocar '0' da coluna do Led e '1' na linha correspondente, ou seja utilizar um segundo pino para acender o led. | ||

| + | |||

| + | ;Aula 29 (14 out): | ||

| + | *Uso do Modelsim para simulação funcional. | ||

| + | :*Use o Modelsim para fazer a simulação do circuito do timer de 0 a 9 segundos. | ||

| + | :*Ver [[Seguindo o tutorial da ALTERA para o MODELSIM]], para utilizar o básico do MODELSIM. | ||

| + | :* [http://www.vhdl.us/Book_VHDL_2ed_unrestricted/Pedroni_VHDL_2ed_tutorial_ModelSim_10.1d_v2.pdf Pedroni VHDL 2ed Tutorial of ModelSim 10.1d] | ||

| + | :* [https://www.youtube.com/watch?v=Z8whdGa7RtY ModelSim Video Tutorial] - Kirk Weedman | ||

| + | :*[[Media:modelsim_tut.pdf |ModelSim® Tutorial]] -v10.0d | ||

| + | :* [[Documentação do ModelSim]], para conhecer mais a fundo o MODELSIM. | ||

| + | |||

| + | <!-- | ||

| + | *Projete um contador BCD de 00 a 99 configurável. | ||

| + | ::Efetue a simulação funcional (Usando o QSIM e o Modelsim) fazendo a contagem de 00 a 11 e 00 a 23 (para hora) , de 00 a 59 (para minutos e segundos), e de 00 a 99. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity Count00_99 is | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Implementação de um relógio contador BCD de segundos. | ||

| + | :*Utilizando o sistema anterior, inclua um contador em BCD de dois dígitos que permita fazer a contagem de 00 a 99, onde o valor final é configurável. | ||

| + | ::Efetue a simulação funcional (Usando o QSIM e o Modelsim) fazendo a contagem de 00 a 11 e 00 a 23 (para hora) , de 00 a 59 (para minutos e segundos), e de 00 a 99. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity Timer00_99seg is | ||

| + | port ( | ||

| + | clk50MHz : in std_logic; | ||

| + | clk1seg : out std_logic; | ||

| + | SSD_Useg : out std_logic_vector(0 to 6); | ||

| + | SSD_Dseg : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | ::configure o FPGA do kit Mercúrio IV para implementar este circuito. Utilize os mostradores ssd DISP0_D e DISP1_D. | ||

| + | *Projeto e simulação com Modelsim do sistema Timer00-99 com display de 7 segmentos e divisor de clock. | ||

| + | *Na simulação definir o clk50MHz como 100ms para produzir um clk1sec com duração de 1 segundo. | ||

| + | *Corrigir o primeiro período de clock de clk1sec. É necessário fazer com que o sinal seja alto primeiro e depois vá para baixo de modo a garantir que a transição positiva ocorra depois de 1 segundo. | ||

| + | *'''IMPORTANTE''': Também é necessário incluir um RESET em cada circuito que seja sequencial. Também é necessário iniciar o circuito com um reset de 10 ps na simulação. | ||

| + | *Perceber a necessidade de parametrizar o conversor de bcd2ssd para permitir displays do tipo CA e AA. (ler [[Display de 7 segmentos]]) | ||

| + | *Perceber a necessidade de incluir um sinal que indique o final da contagem no counter00_99. Esse sinal poderá ser usado como clock no relógio a ser projetado. | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 6 - Projeto a nível de Sistema=== | ||

| + | * 8 AULAS | ||

| + | {{collapse top| Unidade 6 - Projeto a nível de Sistema}} | ||

| + | |||

| + | ; Aula 30 e 31 (16 e 21 out): | ||

| + | *Projeto a nível de Sistema. | ||

| + | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| + | :* O '''COMPONENT''': declaração (cópia da '''ENTITY''') e instanciação. | ||

| + | Assim a entity Timer00_99 | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | ENTITY timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END ENTITY; | ||

| + | </syntaxhighlight> | ||

| + | Será declarada como um COMPONENT | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | COMPONENT timer00_99seg | ||

| + | GENERIC (D : INTEGER; | ||

| + | fclock : INTEGER; | ||

| + | U : INTEGER); | ||

| + | PORT (clk50MHz : IN STD_LOGIC; | ||

| + | RST : IN STD_LOGIC; | ||

| + | clk1seg : OUT STD_LOGIC; | ||

| + | SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6); | ||

| + | SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6)); | ||

| + | END COMPONENT; | ||

| + | </syntaxhighlight> | ||

| + | ::* Associação dos nomes das portas aos sinais. PORT -> '''PORT MAP''': | ||

| + | ::* Mapeamento por posição e nominal. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP (2, 10, 3) | ||

| + | PORT MAP (clk50MHz,RST, clk1seg, SSD_Dseg, SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | comp1 : timer00_99seg | ||

| + | GENERIC MAP ( D => 2, U => 3, | ||

| + | fclock => 10, | ||

| + | PORT MAP ( clk50MHz => clk50MHz, | ||

| + | RST => RST, | ||

| + | clk1seg => clk1seg, | ||

| + | SSD_Dseg => SSD_Dseg, | ||

| + | SSD_Useg => SSD_Useg); | ||

| + | </syntaxhighlight> | ||

| + | ::* Métodos de declaração de '''COMPONENT'''. | ||

| + | :::*Exemplo: Registrador Circular Ex. 8.2 | ||

| + | :* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | ||

| + | ::*Exemplo: Porta E com N entradas. | ||

| + | ::*Exemplo: Detector de Paridade Ex. 8.3 | ||

| + | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | |||

| + | ; Aula 32-33 (24-25 out): | ||

| + | :* Instanciação de '''COMPONENT''' com '''GENERATE'''. | ||

| + | |||

| + | :* Uso da instrução '''CONFIGURATION'''. | ||

| + | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

| + | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| + | |||

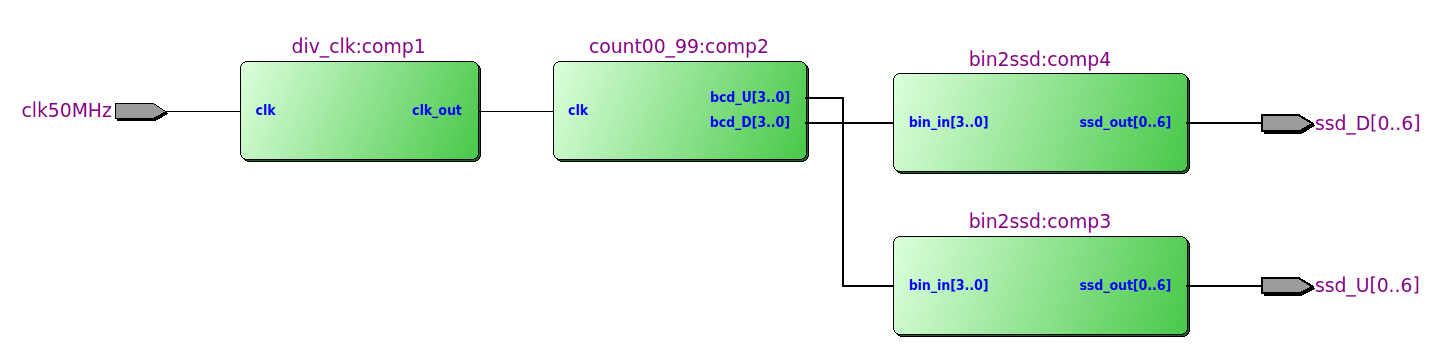

| + | * Implementação de um timer de 99 segundos usando componentes. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity timer00_99seg IS | ||

| + | generic (fclk2 : natural := 50, D : natural := 5; U : natural := 9); | ||

| + | port | ||

| + | ( | ||

| + | clk50MHz : in STD_LOGIC; | ||

| + | clk_1seg: out STD_LOGIC; | ||

| + | ssd_D : out STD_LOGIC_VECTOR(0 TO 6); | ||

| + | ssd_U : out STD_LOGIC_VECTOR(0 TO 6) | ||

| + | ); | ||

| + | end entity; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo parâmetro '''fclk2''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component div_clk is | ||

| + | generic (fclk2 : natural := 50); -- frequecia para simulacao | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic | ||

| + | ); | ||

| + | end component; | ||

| + | ;OBS: | ||

| + | *O valor do fclk2 corresponde a metade do período do clock de entrada em Hz. | ||

| + | |||

| + | </syntaxhighlight> | ||

| + | : Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos parâmetros '''D e U''' | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component count00_99 is | ||

| + | generic (D : natural := 9; U : natural := 9); | ||

| + | port ( | ||

| + | clk : in std_logic; | ||

| + | clk_out : out std_logic; | ||

| + | bcd_U : out std_logic_vector(3 downto 0); | ||

| + | bcd_D : out std_logic_vector(3 downto 0) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *Os valores D e U correspondem ao último valor do timer, depois desse valor o timer dever reiniciar a contagem. | ||

| + | |||

| + | : Componente 3 - Conversor de BIN para SSD, com um parâmetro configurável '''ac_ccn''' para selecionar Anodo ou Catodo Comum. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | component bin2ssd is | ||

| + | generic (ac_ccn : natural := 0); | ||

| + | port ( | ||

| + | bin_in : in std_logic_vector(3 downto 0); | ||

| + | ssd_out : out std_logic_vector(0 to 6) | ||

| + | ); | ||

| + | end component; | ||

| + | </syntaxhighlight> | ||

| + | ;OBS: | ||

| + | *O valor ac_ccn é utilizado para configurar o circuito entre ativo alto para display de catodo comum (ac_ccn=0), ou ativo baixo para display de anodo comum (ac_ccn=1). | ||

| + | |||

| + | |||

| + | O timer deve utilizar os componentes acima de modo a resultar em um RTL semelhante ao mostrado abaixo. | ||

| + | <center> | ||

| + | [[Arquivo:rtl_timer99sec.png | 600 px]] | ||

| + | </center> | ||

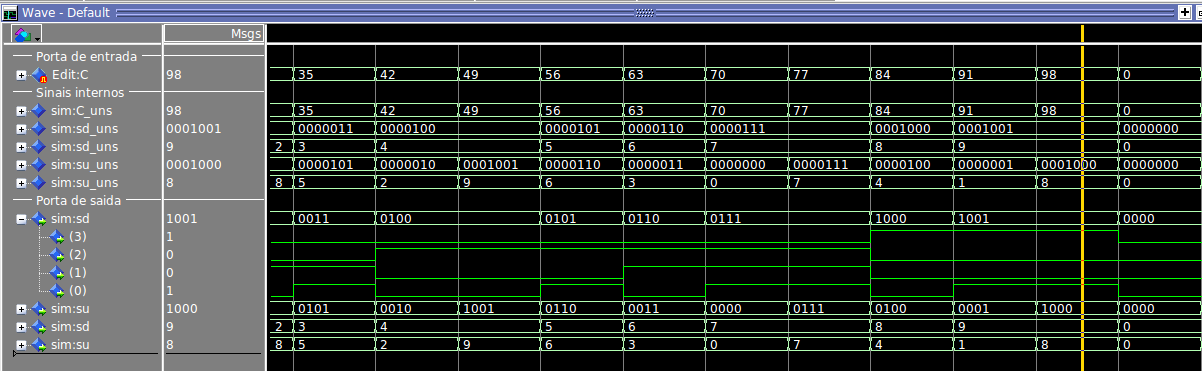

| + | * Simulação do timer com ModelSim. Na simulação definir o clk50MHz com duração de 10 ms. Faça uma simulação de pelo menos 60 segundos. | ||

| + | |||

| + | <center> | ||

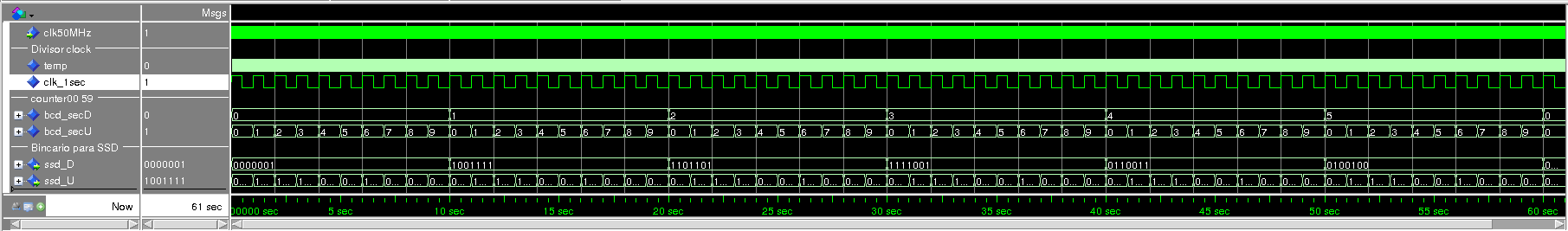

| + | [[Arquivo:sim_timer99sec.png | 800 px]] | ||

| + | </center> | ||

| + | OBS: É recomendável inserir um sinal de RESET em todos os circuitos sequenciais e ao iniciar a simulação do circuito começar com RESET ativo durante 10 ps. | ||

| + | |||

| + | *Após verificar que a simulação do circuito está funcionando, configurar um FPGA para implementar este circuito. Existem duas opções de kit disponíveis com displays de sete segmentos. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. | ||

| + | :* Ao utilizar o kit DE2-115 da TERASIC, utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0-5[0-6]: PIN_G18 - PIN_H22 ...). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <code> | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | :*Ao utilizar o kit Mercúrio IV da MACNICA, utilize os pinos (clk = CLOCK_50MHz: PIN_T1, led = DISP0_D[7] : PIN_W1, ssd = DISP0_D[0-6]: PIN_V2 - PIN_W2). | ||

| + | {{collapse top| definição dos pinos}} | ||

| + | <code> | ||

| + | set_location_assignment PIN_T1 -to clk50MHz | ||

| + | set_location_assignment PIN_V21 -to rst_in | ||

| + | set_location_assignment PIN_R5 -to ssd_D[0] | ||

| + | set_location_assignment PIN_T5 -to ssd_D[1] | ||

| + | set_location_assignment PIN_T3 -to ssd_D[2] | ||

| + | set_location_assignment PIN_T4 -to ssd_D[3] | ||

| + | set_location_assignment PIN_M6 -to ssd_D[4] | ||

| + | set_location_assignment PIN_N7 -to ssd_D[5] | ||

| + | set_location_assignment PIN_N6 -to ssd_D[6] | ||

| + | set_location_assignment PIN_V2 -to ssd_U[0] | ||

| + | set_location_assignment PIN_V1 -to ssd_U[1] | ||

| + | set_location_assignment PIN_U2 -to ssd_U[2] | ||

| + | set_location_assignment PIN_U1 -to ssd_U[3] | ||

| + | set_location_assignment PIN_Y2 -to ssd_U[4] | ||

| + | set_location_assignment PIN_Y1 -to ssd_U[5] | ||

| + | set_location_assignment PIN_W2 -to ssd_U[6] | ||

| + | set_location_assignment PIN_W1 -to clk_1seg | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | :* Análise o diagrama esquemático como funcionam as chaves e também o tipo de display. Note que no projeto o signal RST foi descrito como normalmente ALTO, podendo ser necessário acrescentar um inversor para ter o funcionamento correto. O [[Display de 7 segmentos]] da DE2-115 é do tipo cátodo comum, enquanto que na MERCURIO IV ele é do tipo ânodo comum. | ||

| + | |||

| + | <!-- | ||

| + | ; Aula 36 (31 Out): | ||

| + | *Projeto a nível de Sistema. | ||

| + | FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | ||

| + | |||

| + | A instrução '''ASSERT''' é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a sintese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] assert condição_booleana | ||

| + | [report mensagem] | ||

| + | [severity nivel_severidade]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | A mensagem pode ser criada usando STRINGs que podem ser concatenadas. | ||

| + | |||

| + | O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [https://www.ics.uci.edu/~jmoorkan/vhdlref/assert.html]. | ||

| + | |||

| + | :* A '''FUNCTION''': declaração, uso, mapeamento posicional x nominal, PURE x IMPURE. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function nome_funçao (lista_parametros_entrada) return tipo_saida is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end function; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Uso de '''FUNCTION''' e '''ASSERT'''. | ||

| + | ::* Exemplo: Declaração em ARCHITECTURE Ex.9.1 | ||

| + | ::* Exemplo: Declaração em PACKAGE Ex. 9.2 | ||

| + | ::* Exemplo: Declaração em ENTITY Ex. 9.3 | ||

| + | |||

| + | Abaixo segue um exemplo de cálculo do '''log2''' de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function log2c (n : integer) return integer is | ||

| + | variable m , p : integer; | ||

| + | begin | ||

| + | m := 0; | ||

| + | p : = 1; | ||

| + | while p < n loop | ||

| + | m : = m + 1; | ||

| + | p := p * 2; | ||

| + | end loop; | ||

| + | return m; | ||

| + | end log2c; | ||

| + | </syntaxhighlight> | ||

| + | --> | ||

| + | <!-- | ||

| + | ; Aula 37 (19 mai): | ||

| + | :*Uso de '''PROCEDURE'''. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end procedure; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::*Exemplo: min_max Ex.9.4 | ||

| + | ::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| + | :* Ver pag. 213 a 239 de <ref name="PEDRONI2010b"/>) | ||

| + | |||

| + | ; Aula 33 e 34 (23 e 26 mai): | ||

| + | :*Uso de '''FUNCTION''' e '''PROCEDURE'''. | ||

| + | ::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| + | |||

| + | ;Aula 36 a 38 (4 a 8 jun): | ||

| + | * Implementação de um serializador e um deserializador usando componentes. | ||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo '''generic N''' | ||

| + | entity div_clk is | ||

| + | entrada clk_in | ||

| + | saída clk_out | ||

| + | : Componente 2 - Registrador de deslocamento com entrada serial e paralelo e saída serial e paralelo com N FF, configurável pelo '''generic N''' | ||

| + | entity shift_reg is | ||

| + | entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in | ||

| + | saídas d_out[N-1..0], s_out | ||

| + | |||

| + | : Componente 3 - Porta paralela com N entradas, configurável pelo '''generic N'''. | ||

| + | entity port_par is | ||

| + | entradas clk_in, rst, ena, d_in[N-1..0] | ||

| + | saídas d_out[N-1..0] | ||

| + | |||

| + | * Simulação do serializador e deserializador com ModelSim. | ||

| + | * Integração dos dois componentes em um único componente. | ||

| + | |||

| + | ;Aula 27 (7 mai): | ||

| + | * Implementar um circuito de relógio que conte HH:MM:SS. | ||

| + | |||

| + | :::*PROBLEMA: Uso de um período de clock de 20 ns => 50 MHz, verificar a impossibilidade prática de uma simulação deste circuito (1 segundo => 5 minutos de simulação), devido ao tamanho do contador (count1) que conta de 0 a 50M-1. | ||

| + | :::*SOLUÇÃO: modificar o contador para um valor maximo menor (0 a 5-1), e a mesmo tempo mudar o período de clock para 200 ms => 5 Hz. Notar que a simulação é extremamente rápida neste caso. | ||

| + | :::*Após verificar que o circuito funciona "simulado", configurar o FPGA do kit DE2-115 para implementar este circuito. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. Utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0[0-6]: PIN_G18 - PIN_H22). Note que a chave usada para o rst é normalmente alta, e portanto é necessário acrescentar um inversor a esta entrada. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Renomeie a porta rst para rst_in. | ||

| + | PORT ( | ||

| + | clk, rst_in : IN BIT; | ||

| + | |||

| + | --Crie um sinal interno para inverter o clock | ||

| + | ARCHITECTURE counter OF slow_counter IS | ||

| + | signal rst : BIT; | ||

| + | BEGIN | ||

| + | rst <= not rst_in; | ||

| + | </syntaxhighlight> | ||

| + | :::*Programe o FPGA usando o programador e verifique se a contagem está correta (a cada segundo). | ||

| + | |||

| + | ;Aula 29,30 ( ): | ||

| + | *Código Sequencial. | ||

| + | * Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando um COMPONENT contador BCD de 00 a 99. Instancie 3 COMPONENTES para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ser implementados com um COMPONENT "bin2ssd" que converte o número 0 a 9 em bits do código SSD. | ||

| + | :* Simular o relógio HH:MM:SS com Modelsim, duração de 49 horas. | ||

| + | :* Implementar o relógio no kit DE2-115 (opcional) - neste caso é necessário incluir um divisor de clock antes do contador de segundo. | ||

| + | |||

| + | ::*Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity counter60seg is | ||

| + | generic (fclk: integer := 2); -- valor usado para simulação. | ||

| + | -- generic (fclk: integer := 50_000_000); -- valor usado para implementação com clk de 50 MHz. | ||

| + | port ( | ||

| + | clk, rst : in std_logic; | ||

| + | ssd_un, ssd_dz: out std_logic_vector(6 downto 0)); | ||

| + | end entity ; | ||

| + | |||

| + | architecture version1 of counter60seg is | ||

| + | -- Versão proposta por Gabriel Cantu (processo único) | ||

| + | ... | ||

| + | begin | ||

| + | ... | ||

| + | end architecture ; | ||

| + | |||

| + | architecture version2 of counter60seg is | ||

| + | -- Versão proposta por Gustavo Constante (5 processos) | ||

| + | ... | ||

| + | begin | ||

| + | ... | ||

| + | end architecture ; | ||

| + | |||

| + | configuration counter60seg_cfg of counter60seg is | ||

| + | for version1 end for; | ||

| + | -- for version2 end for; | ||

| + | end configuration; | ||

| + | </syntaxhighlight> | ||

| + | --> | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | |||

| + | ===Unidade 7 - Maquinas de Estado Finitas=== | ||

| + | {{collapse top| Unidade 7 - Maquinas de Estado Finitas}} | ||

| + | * 6 AULAS | ||

| + | |||

| + | ; Aula 34 (30 out): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O que é uma FSM - Finite State Machine | ||

| + | :* Modelo de FSM | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | pr_state <= nx_state; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value > ; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

| + | :* Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1. | ||

| + | :* Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados | ||

| + | :rst -> A -(x=0)-> A -(x=1)-> A -(x=2)-> B -(x=2)-> B -(x=0)-> C -(x=0)-> C -(x=2)-> C -(x=1)-> A -(x=2)-> B -(x=1)-> A. | ||

| + | :: Ver pag. 277 a 35 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ; Aula 35 (04 nov): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

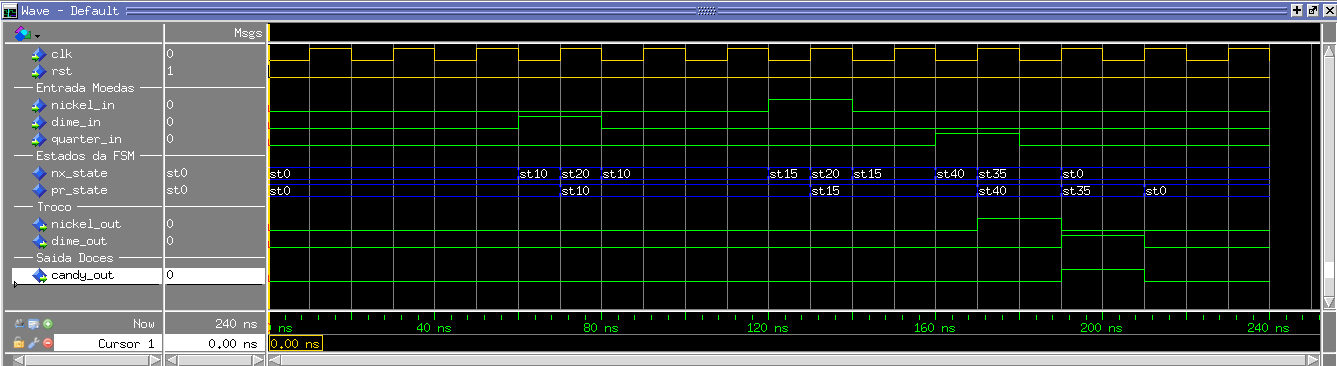

| + | :* Exemplo 11.1 Controlador de uma máquina de Venda | ||

| + | ::*Compile o código mostrado no Exemplo 11.1. | ||

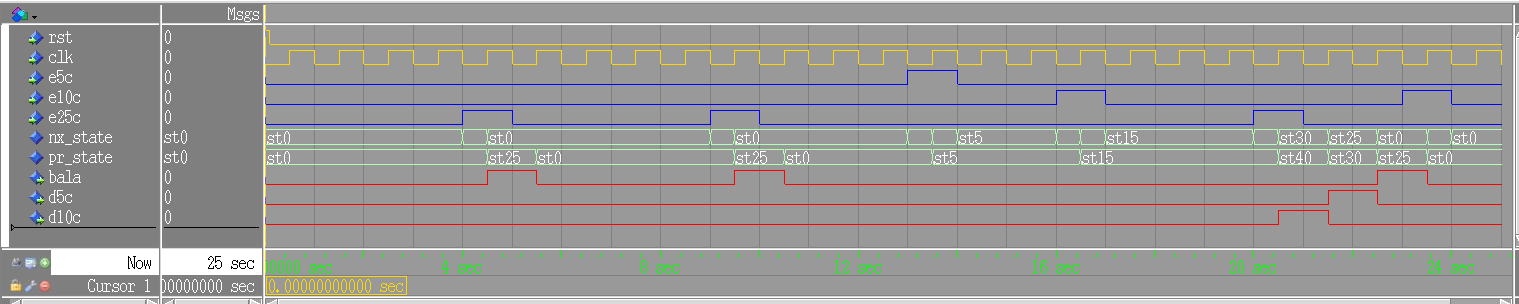

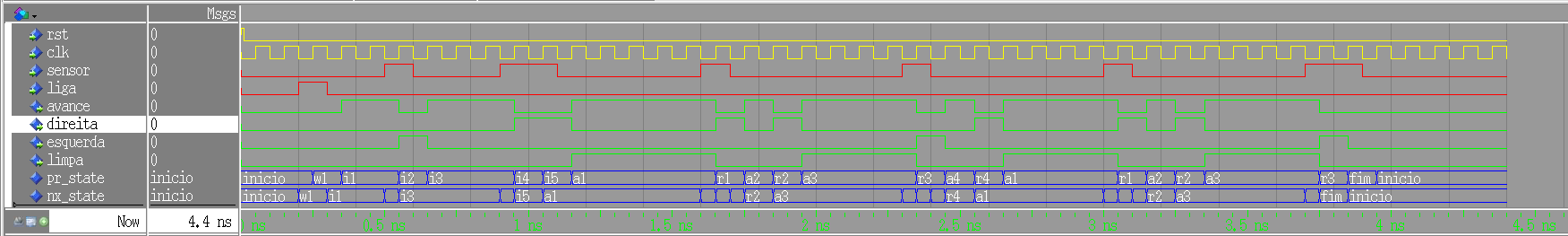

| + | ::*Simule a FSM com Modelsim utilizando um testbench em VHDL para gerar o teste mostrado na figura abaixo. | ||

| + | |||

| + | :::[[Arquivo:FSM_tb40.png | 1000 px]] | ||

| + | |||

| + | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| + | :: Ver pag. 281 a 282 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | |||

| + | ; Aula 36 (06 nov) | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* O problema de bypassar estados em FSM (explicação do funcionamento através do alarme de carro. | ||

| + | ::* Exemplo 11.4 Alarme de Carro (com FLAG) | ||

| + | ::* Exemplo 11.5 Alarme de Carro (com estados de WAIT adicionais). | ||

| + | :: Ver pag. 292 a 297 de <ref name="PEDRONI2010b"/> | ||

| + | :* Projeto de FSM temporizadas (nas quais as transições são ativadas também pelo tempo). | ||

| + | :* Modelo de FSM temporizada | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.ALL; | ||

| + | ---------------------------------------------------------- | ||

| + | ENTITY < entity_name > IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | input : IN < data_type > ; | ||

| + | output : OUT < data_type >); | ||

| + | END < entity_name > ; | ||

| + | ---------------------------------------------------------- | ||

| + | ARCHITECTURE < architecture_name > OF < entity_name > IS | ||

| + | TYPE state IS (A, B, C, ...); | ||

| + | SIGNAL pr_state, nx_state : state; | ||

| + | signal timer: integer range 0 to MAX; | ||

| + | -- ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute | ||

| + | -- ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential"; | ||

| + | BEGIN | ||

| + | ------Logica Sequencial da FSM:------------ | ||

| + | PROCESS (clk, rst) | ||

| + | variable count: integer range o to MAX; | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | pr_state <= A; | ||

| + | count := 0; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN | ||

| + | count := count + 1; | ||

| + | if (count >= timer) then | ||

| + | pr_state <= nx_state; | ||

| + | count := 0; | ||

| + | end if; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | ------Logica Combinacional da FSM:------------ | ||

| + | PROCESS (pr_state, input) | ||

| + | BEGIN | ||

| + | ------Valores default das saidas------------ | ||

| + | output <= < value >; | ||

| + | ------Valores default do timer------------ | ||

| + | timer <= <value>; | ||

| + | CASE pr_state IS | ||

| + | WHEN A => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= A; | ||

| + | END IF; | ||

| + | WHEN B => | ||

| + | output <= < value > ; -- apenas se diferente do valor default | ||

| + | IF (input =< value >) THEN | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= C; | ||

| + | ... | ||

| + | ELSE | ||

| + | timer <= <value>; -- apenas se diferente do valor default | ||

| + | nx_state <= B; | ||

| + | END IF; | ||

| + | WHEN ... | ||

| + | END CASE; | ||

| + | END PROCESS; | ||

| + | ------Seção de Saída (opcional):------- | ||

| + | PROCESS (clk, rst) | ||

| + | BEGIN | ||

| + | IF (rst = '1') THEN | ||

| + | new_output <= < value > ; | ||

| + | ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0' | ||

| + | new_output <= output; | ||

| + | END IF; | ||

| + | END PROCESS; | ||

| + | END < architecture_name > ; | ||

| + | </syntaxhighlight> | ||

| + | :: Ver pag. 298 a 301 de <ref name="PEDRONI2010b"/> | ||

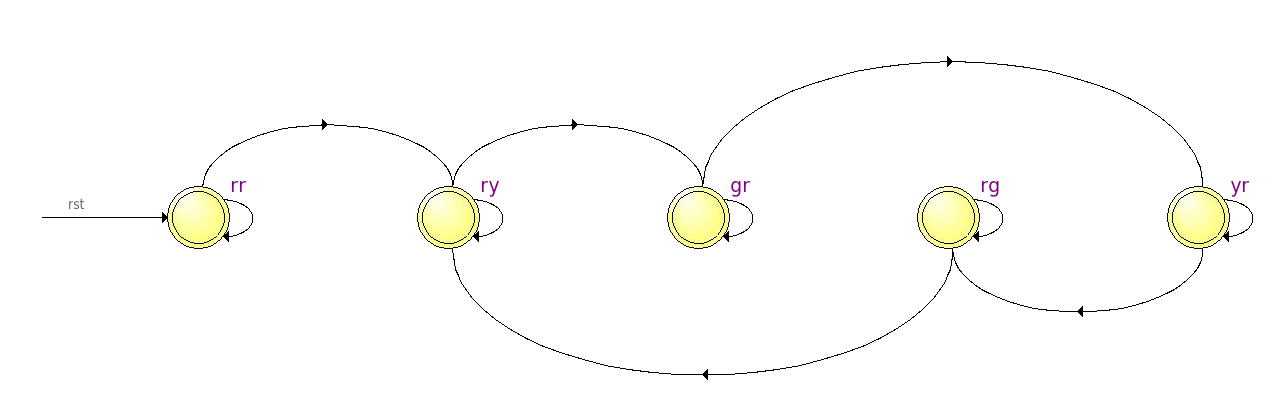

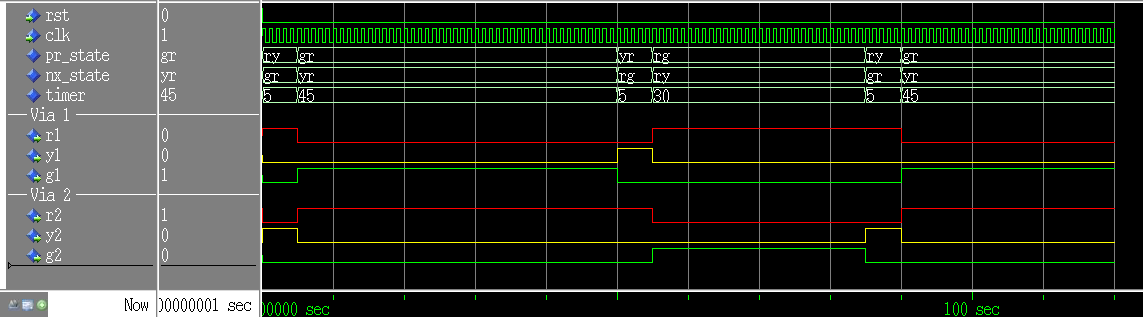

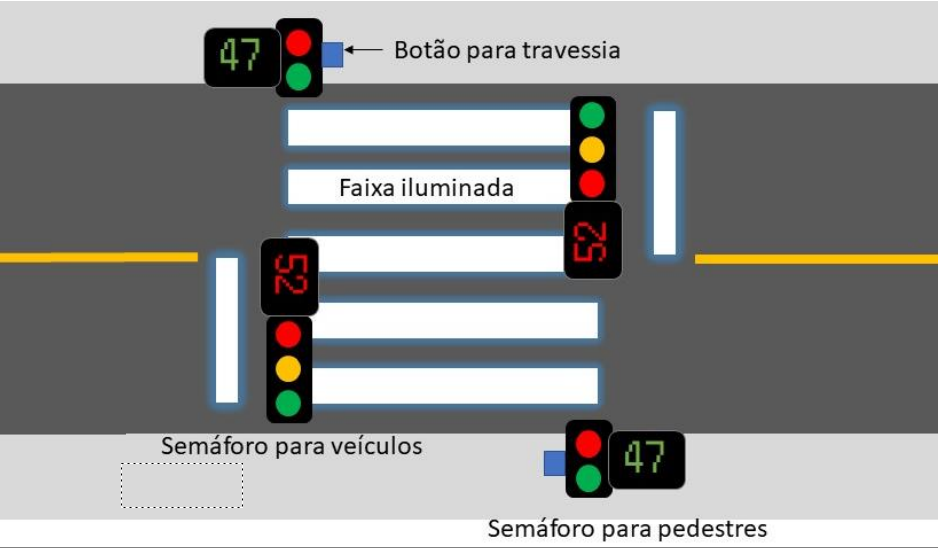

| + | :* Usando o template acima descreva em VHDL a FSM de um controlador de semáforo Regular da Figura 11.15 (pag. 304 de <ref name="PEDRONI2010b"/>). | ||

| + | <center> | ||

| + | [[Arquivo:Semaforo_FSM.png| 800px]] | ||

| + | </center> | ||

| + | ::* Para definir as temporizações utilize GENERICs que permitam instanciar diferentes semáforos em um projeto de controle de tráfego de uma avenida. | ||

| + | ::* Considere que o sinal de clock tem período de 1 segundo. | ||

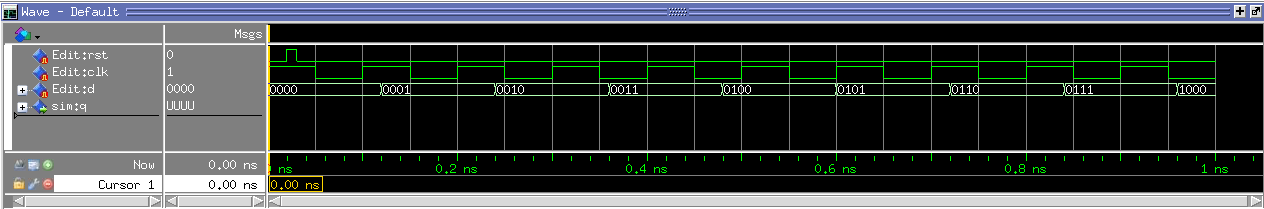

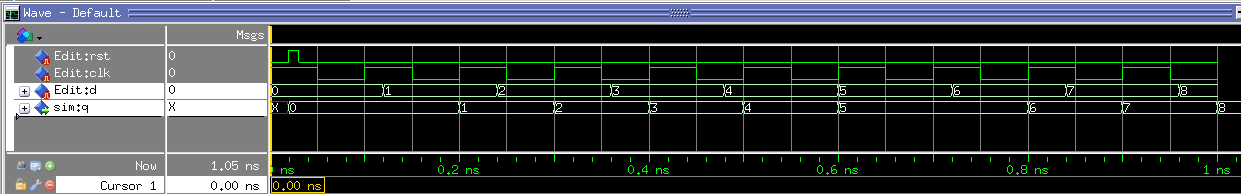

| + | ::* Realize a simulação do semáforo, destacando as saídas com as cores correspondentes, conforme mostrado abaixo: | ||

| + | <center> | ||

| + | [[Arquivo:Semaforo_ModelSim.png| 800px]] | ||

| + | </center> | ||

| + | |||

| + | |||

| + | ; Aula 37 (08 nov) | ||

| + | *Exercício: Faça o download do arquivo simple_car_alarm.qar, disponível no Moodle da disciplina e realize as seguintes avaliações: | ||

| + | :#Perceba que existem 4 versões para o mesmo Alarme de Carro. Realize a simulação no ModelSim das 4 versões e perceba qual é a diferença de funcionamento desses circuitos. | ||

| + | :#Anote o número de elementos em cada versão. | ||

| + | :#Qual versão é a mais adequada na sua opinião? | ||

| + | :#Modifique a sua escolha para que o alarme não possa ser ativado se o "sensor" estiver em "1". | ||

| + | :#Analise o arquivo tb_vX.do e modifique-o para testar também essa nova condição. A simulação deve obrigatoriamente fazer o sistema passar por todos os estados e todas as transições. | ||

| + | :#Implemente a nova versão como uma nova arquitetura "fsm_v5", e escrever o arquivo de simulação "tbv5.do". | ||

| + | :#Salve as telas da simulação ("v5_sim.png"), tela da fsm ("v5_fsm.png"), tela do RTL ("v5_rtl.png"). | ||

| + | :#Acrescente os novos arquivos no projeto e salve o novo .qar | ||

| + | |||

| + | <!-- | ||

| + | ; Aula 37 (08 nov) | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* Maquina FSM . | ||

| + | :*Implementar a FSM para uma sinaleira manual para duas vias. A mudança do sinal deve ser feito a partir do acionamento de uma chave por um guarda. | ||

| + | <code> | ||

| + | ENTITY sinal_manual IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | guarda: IN STD_LOGIC; | ||

| + | LVd1, LAm1, LVm1 : OUT std_logic; -- Lampadas da Via 1 | ||

| + | LVd2, LAm2, LVm2 : OUT std_logic -- Lampadas da Via 2 | ||

| + | ); | ||

| + | END entity ; | ||

| + | </syntaxhighlight> | ||

| + | O diagrama da FSM deve ser algo parecido com o mostrado abaixo | ||

| + | <center> | ||

| + | [[Arquivo:FSMSinaleiraManual.png|800px]] | ||

| + | </center> | ||

| + | *Note que se o sinal guarda permanece alto por mais que um clock, ocorre a mudança de mais de um estado. Para evitar esse problema pode ser utilizada a técnica de usar um FLAG, ou estados de WAIT no qual se aguarda o retorno dos sinal para baixo antes de avançar para o próximo estado. | ||

| + | |||

| + | |||

| + | ; Aula 39 (mai): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* Maquina FSM temporizada. | ||

| + | :*Implementar a maquina temporizada para uma sinaleira automática para duas vias. | ||

| + | <code> | ||

| + | ENTITY sinal_auto IS | ||

| + | GENERIC (TVd1: natural := 300; TVd2: natural := 120; TAm: natural := 10); | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | LVd1, LAm1, LVm1 : OUT std_logic; -- Lampadas da Via 1 | ||

| + | LVd2, LAm2, LVm2 : OUT std_logic -- Lampadas da Via 2 | ||

| + | ); | ||

| + | END entity ; | ||

| + | </syntaxhighlight> | ||

| + | Os tempos '''TVd1''' e '''TVd2''' são os tempos em segundos para verde das vias 1 e 2 respectivamente. '''TAm''' é o tempo em segundos que fica em amarelo em ambas vias. | ||

| + | |||

| + | A simulação no ModelSim da sinaleira deve resultar em algo conforme mostrado abaixo: | ||

| + | <center> | ||

| + | [[Arquivo:SimSinaleiraAutom.png|800px]] | ||

| + | </center> | ||

| + | |||

| + | *'''DICA:''' Use na simulação comandos que automatizam o processo através de um script '''tb_sinal_auto.do''' | ||

| + | <code> | ||

| + | vcom -93 -work work {../../sinal_auto.vhd} | ||

| + | vsim work.sinal_auto | ||

| + | do wave.do | ||

| + | force -freeze sim:/sinal_auto/clk 1 0, 0 {0.5sec} -r {1 sec} | ||

| + | force -freeze sim:/sinal_auto/rst 1 0, 0 0.01 sec | ||

| + | run 25 min | ||

| + | </syntaxhighlight> | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| + | {{collapse top| expand=true | Unidade 8 - Testbench}} | ||

| + | |||

| + | ===Unidade 8 - Testbench=== | ||

| + | * 2 AULAS | ||

| + | ; Aula 38 (11 nov): | ||

| + | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| + | :*Tipos de simulação: | ||

| + | ::1) simulação funcional (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003 | ||

| + | ::2) simulação temporal (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003 | ||

| + | ::3) simulação funcional (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - OK já visto | ||

| + | ::4) simulação temporal (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - Não será visto | ||

| + | ::5) simulação funcional (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade | ||

| + | ::6) simulação temporal (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade | ||

| + | ::7) simulação funcional (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ||

| + | ::8) simulação temporal (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ||

| + | :* Simular a maquina de venda de doces Ex 11.1 | ||

| + | |||

| + | <!-- | ||

| + | :*Exemplo de Conversor Binário para Gray (Exercício 9.7) | ||

| + | |||

| + | :*Para usar o ModelSim 10.1d na CLOUD-IFSC(191.36.8.33) abra um terminal e digite: | ||

| + | /opt/altera/13.0sp1/modelsim_ae/bin/vsim | ||

| + | :* ou | ||

| + | vsim | ||

| + | :*Para usar o ModelSim 10.1d nos Laboratórios do IFSC campus São José abra um terminal e digite: | ||

| + | /opt/altera/13.0/quartus/modelsim_ae/linux/vsim | ||

| + | |||

| + | :*Ver também [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_func_sim.htm Performing a Functional Simulation with the ModelSim-Altera Software], e [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_timing_sim.htm Performing a Timing Simulation with the ModelSim-Altera Software]. | ||

| + | |||

| + | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| + | ::*Implementar um sistema constituído de dois circuitos de SHIFT RIGHT LOGICAL - SRL_L com entradas de DADOS, LOAD e RESET, e saída paralela. Crie um componente SOMADOR constituido de um somado do tipo UNSIGNED. Conecte as saídas dos SRL_L ao SOMADOR. | ||

| + | <center> | ||

| + | [[Arquivo:slr_adder.png]] | ||

| + | </center> | ||

| + | |||

| + | ::*Criar um testbench em VHDL para testar cada componente (SOMADOR, o SRL_L) e o sistema final. (faça com o test bench teste no minimo o funcionamento da entrada LOAD para 2 entradas diferentes de DADOS, o RESET, o SOMADOR e o funcionamento do SRL_L para uma sequencia de pelo menos N clocks, onde N é o número de bits das entradas. | ||

| + | |||

| + | ::Note que no final deste projeto, deverão existir pelo menos os arquivos de projeto '''srl_l.vhd''', '''somador.vhd''', '''sistema.vhd''' e os arquivos de teste bench correspondentes '''srl_l_tb.vht''', '''somador_tb.vht''', '''sistema_tb.vht'''. Para facilitar a simulação no Modelsim recomenda-se criar também os arquivos de script '''srl_l.do''', '''somador.do''', '''sistema.do'''. | ||

| + | |||

| + | --> | ||

| + | ::'''DICA''': Use o comando do Quartus II para gerar um template para o testbench. Selecione cada componente como TOP LEVEL e faça a ANÁLISE E SÍNTESE em seguida ('''Processing > Start > Start Test Bench Template Writer'''). | ||

| + | :* Criação de sinais para Test Bench em VHDL | ||

| + | |||

| + | {{collapse top | Geração de sinal de clock}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant tclk: time := 1 ns; | ||

| + | signal clk : std_logic := '0'; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO CONCORRENTE) | ||

| + | clk <= not clk after tclk; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | clk <= '1'; | ||

| + | wait for tclk; | ||

| + | clk <= '0'; | ||

| + | wait for tclk; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de sinal de reset}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant treset: time := 100 ps; | ||

| + | signal reset : std_logic; | ||

| + | |||

| + | -- RESET COM DURAÇÃO DE treset (COM CÓDIGO CONCORRENTE) | ||

| + | reset <= '1', '0' after treset; | ||

| + | |||

| + | -- RESET COM DURAÇÃO DE treset (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | reset <= '1'; | ||

| + | wait for treset; | ||

| + | reset <= '0'; | ||

| + | wait; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de uma sequencia binária}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant t_a: time := 100 ps; | ||

| + | constant Nbits: natural := 8; | ||

| + | signal a : std_logic_vector(Nbits-1 downto 0); | ||

| + | |||

| + | -- GERAÇÂO DO SINAL a = [0 1 2 3 4 ...] COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL) | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | for i in 0 to 2**Nbits-1 loop | ||

| + | a <= std_logic_vector(to_unsigned(i,Nbits)); | ||

| + | wait for t_a; | ||

| + | end loop; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | Geração de uma sequencia pseudoaleatória}} | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- DECLARAR | ||

| + | constant t_a: time := 100 ps; | ||

| + | constant Nbits: natural := 8; | ||

| + | signal a : std_logic_vector(Nbits-1 downto 0) := (0 => '1', 3 => '1', others => '0'); | ||

| + | |||

| + | -- GERAÇÂO DO SINAL a COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL) | ||

| + | -- USANDO UM CONTADOR LFSR | ||

| + | PROCESS | ||

| + | BEGIN | ||

| + | for i in 0 to 2**Nbits-1 loop | ||

| + | a <= (a(0) xor a(2) xor a(3) xor a(4)) & a(Nbits-1 downto 1); -- para 8 bits | ||

| + | wait for t_a; | ||

| + | end loop; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | {{collapse bottom}} | ||

| + | ; Aula 39 (13 nov): | ||

| + | *Código VHDL da maquina de venda de balas | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | --------------------------------- | ||

| + | -- FILE: vende_balas_FSM.vhd | ||

| + | --------------------------------- | ||

| + | library ieee; | ||

| + | use ieee.std_logic_1164.all; | ||

| + | |||

| + | entity vende_balas_FSM is | ||

| + | port( | ||

| + | rst, clk : in std_logic; | ||

| + | e5c, e10c, e25c: in std_logic; | ||

| + | d5c, d10c: out std_logic; | ||

| + | bala: out std_logic | ||

| + | ); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of vende_balas_FSM is | ||

| + | type state is ( | ||

| + | st0, st5, st10, st15, st20, st25, st30, st35, st40, st45 | ||

| + | ); | ||

| + | signal pr_state, nx_state: state; | ||

| + | begin | ||

| + | process(clk, rst) | ||

| + | begin | ||

| + | if rst = '1' then | ||

| + | pr_state <= st0; | ||

| + | elsif rising_edge(clk) then | ||

| + | pr_state <= nx_state; | ||

| + | end if; | ||

| + | end process; | ||

| + | |||

| + | process(pr_state, e5c, e10c, e25c) | ||

| + | begin | ||

| + | bala <= '0'; | ||

| + | d5c <= '0'; | ||

| + | d10c <= '0'; | ||

| + | case pr_state is | ||

| + | when st0 => | ||

| + | if e5c = '1' then | ||

| + | nx_state <= st5; | ||

| + | elsif e10c = '1' then | ||

| + | nx_state <= st10; | ||

| + | elsif e25c = '1' then | ||

| + | nx_state <= st25; | ||

| + | else | ||

| + | nx_state <= st0; | ||

| + | end if; | ||

| + | when st5 => | ||

| + | if e5c = '1' then | ||

| + | nx_state <= st10; | ||

| + | elsif e10c = '1' then | ||

| + | nx_state <= st15; | ||

| + | elsif e25c = '1' then | ||

| + | nx_state <= st30; | ||

| + | else | ||

| + | nx_state <= st5; | ||

| + | end if; | ||

| + | when st10 => | ||

| + | if e5c = '1' then | ||

| + | nx_state <= st15; | ||

| + | elsif e10c = '1' then | ||

| + | nx_state <= st20; | ||

| + | elsif e25c = '1' then | ||

| + | nx_state <= st35; | ||

| + | else | ||

| + | nx_state <= st10; | ||

| + | end if; | ||

| + | when st15 => | ||

| + | if e5c = '1' then | ||

| + | nx_state <= st20; | ||

| + | elsif e10c = '1' then | ||

| + | nx_state <= st25; | ||

| + | elsif e25c = '1' then | ||

| + | nx_state <= st40; | ||

| + | else | ||

| + | nx_state <= st15; | ||

| + | end if; | ||

| + | when st20 => | ||

| + | if e5c = '1' then | ||

| + | nx_state <= st25; | ||

| + | elsif e10c = '1' then | ||

| + | nx_state <= st30; | ||

| + | elsif e25c = '1' then | ||

| + | nx_state <= st45; | ||

| + | else | ||

| + | nx_state <= st20; | ||

| + | end if; | ||

| + | when st25 => | ||

| + | bala <= '1'; | ||

| + | nx_state <= st0; | ||

| + | when st30 => | ||

| + | d5c <= '1'; | ||

| + | nx_state <= st25; | ||

| + | when st35 => | ||

| + | d10c <= '1'; | ||

| + | bala <= '1'; | ||

| + | nx_state <= st0; | ||

| + | when st40 => | ||

| + | d10c <= '1'; | ||

| + | nx_state <= st30; | ||

| + | when st45 => | ||

| + | d10c <= '1'; | ||

| + | nx_state <= st35; | ||

| + | end case; | ||

| + | end process; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | *Script tb.do para um testbench para Modelsim. | ||

| + | <code> | ||

| + | ################################# | ||

| + | ## FILE: tb.do | ||

| + | ################################# | ||

| + | vcom -93 -work work {../../vende_balas_FSM.vhd} | ||

| + | vsim work.vende_balas_FSM | ||

| + | |||

| + | add wave -position end -color gold sim:/vende_balas_FSM/rst | ||

| + | add wave -position end -color gold sim:/vende_balas_FSM/clk | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e5c | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e10c | ||

| + | add wave -position end -color blue sim:/vende_balas_FSM/e25c | ||

| + | add wave -position end sim:/vende_balas_FSM/nx_state | ||

| + | add wave -position end sim:/vende_balas_FSM/pr_state | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/bala | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/d5c | ||

| + | add wave -position end -color red sim:/vende_balas_FSM/d10c | ||

| + | configure wave -timelineunits sec | ||

| + | WaveRestoreZoom {0 ps} {25sec} | ||

| + | |||

| + | force -freeze sim:/vende_balas_FSM/rst 1 0, 0 0.1 sec | ||

| + | force -freeze sim:/vende_balas_FSM/clk 0 0, 1 {0.5 sec} -r 1sec | ||

| + | force -freeze sim:/vende_balas_FSM/e5c 0 0, 1 13sec, 0 14sec | ||

| + | force -freeze sim:/vende_balas_FSM/e10c 0 0, 1 16sec, 0 17sec, 1 23sec, 0 24sec | ||

| + | force -freeze sim:/vende_balas_FSM/e25c 0 0, 1 4sec, 0 5sec, 1 9sec, 0 10sec, 1 20sec, 0 21sec | ||

| + | run 25 sec | ||

| + | </syntaxhighlight> | ||

| + | *Resultado da simulação no Modelsim. Execute do tb.do | ||

| + | <center> | ||

| + | [[Arquivo:vende_balas_FSM_sim.png | 800px]] | ||

| + | </center> | ||

| + | *Use o template gerado pelo Quartus e acrescente os estimulos indicados abaixo e realize a simulação usando agora o testbench em VHDL. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | |||

| + | -- constants | ||

| + | constant tclk: time := 0.5 sec; | ||

| + | constant treset: time := 100 ps; | ||

| + | constant talto: time := 1 sec; | ||

| + | |||

| + | -- RESET COM DURAO DE treset (COM CDIGO CONCORRENTE) | ||

| + | sim_rst: rst <= '1', '0' after treset; | ||

| + | |||

| + | -- CLOCK COM PERIODO DE 2*tclk (COM CDIGO SEQUENCIAL) | ||

| + | sim_clk: PROCESS | ||

| + | BEGIN | ||

| + | clk <= '0'; | ||

| + | wait for tclk; | ||

| + | clk <= '1'; | ||

| + | wait for tclk; | ||

| + | END PROCESS; | ||

| + | -- GERAAO DO ESTIMULO "e5c"(COM CDIGO SEQUENCIAL) | ||

| + | sim_e5c: e5c <= '0', '1' after 13 sec, '0' after 14 sec; | ||

| + | |||

| + | -- GERAAO DO ESTIMULO "e5c"(COM CDIGO SEQUENCIAL) | ||

| + | sim_e10c: e10c <= '0', '1' after 16 sec, '0' after 17 sec, '1' after 23 sec, '0' after 24 sec; | ||

| + | |||

| + | -- GERAAO DO ESTIMULO "e25c"(COM CDIGO SEQUENCIAL) | ||

| + | |||

| + | -- sim_e25c: PROCESS | ||

| + | -- BEGIN | ||

| + | -- e25c <= '0'; | ||

| + | -- wait for 4 sec; | ||

| + | -- e25c <= '1'; | ||

| + | -- wait for 1 sec; | ||

| + | -- e25c <= '0'; | ||

| + | -- END PROCESS; | ||

| + | |||

| + | -- Os tempos neste caso sao os intervalos entre os eventos | ||

| + | -- No exemplo acima o SIGNAL e25c inicia com '0', muda para '1' apos 4 segundos, | ||

| + | -- e depois muda para '0' depois de mais 1 segundo | ||

| + | -- em CDIGO SEQUENCIALo mesmo estimulo seria gerado com: | ||

| + | -- sim_e25c: e25c <= '0', '1' after 4 sec, '0' after 5 sec; | ||

| + | |||

| + | sim_e25c: PROCESS | ||

| + | BEGIN | ||

| + | e25c <= '0'; | ||

| + | wait for 4 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 3 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 10 sec; | ||

| + | e25c <= '1'; | ||

| + | wait for talto; | ||

| + | e25c <= '0'; | ||

| + | wait for 5 sec; | ||

| + | END PROCESS; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ===ATUAL=== | ||

| + | ;Aula 40 (18 Nov): | ||

| + | |||

| + | * Especificação do projeto final. Ver detalhes abaixo no tópico Projeto Final. | ||

| + | |||

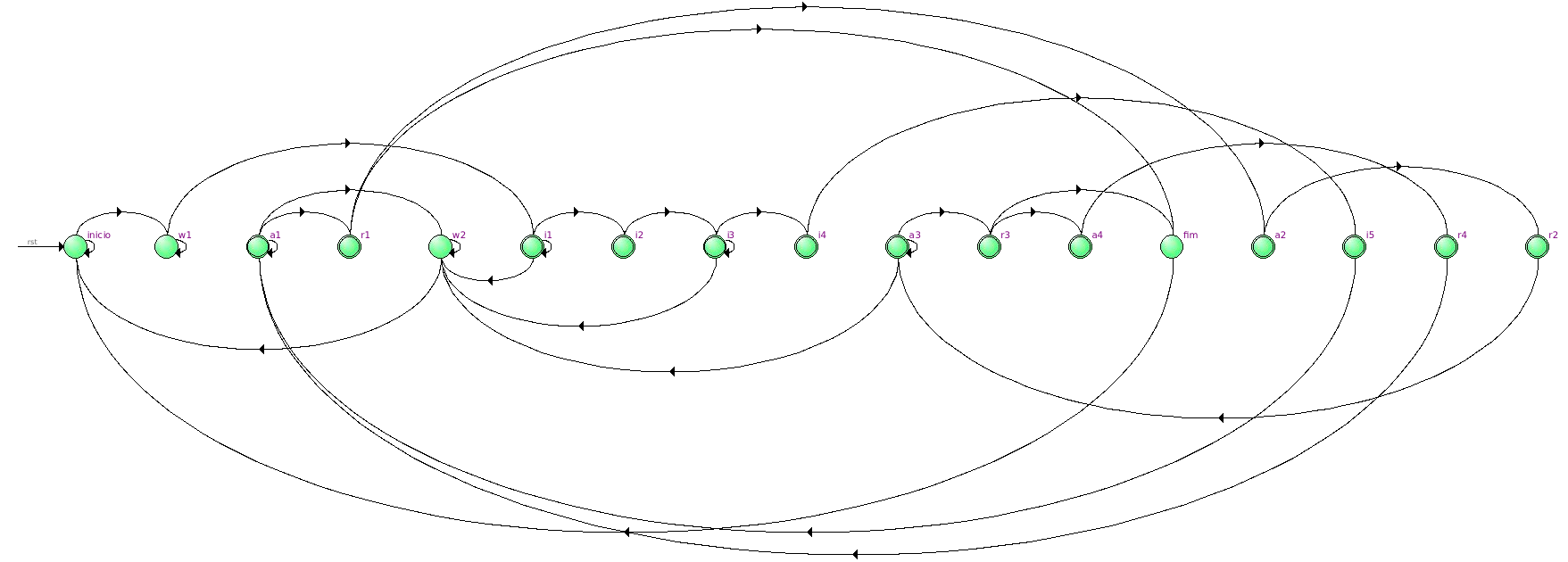

| + | * Definição de uma maquina de estados finita (FSM) para um robô de limpeza de áreas retangulares. (sugerido por ARY HAUFFE NETO) | ||

| + | :*O robô ao ser colocado em uma área retangular ao ser ligado deve ir até o canto superior esquerdo. | ||

| + | :*A limpeza deve ser realizada indo e voltando em linhas paralelas até atingir o canto inferior. | ||

| + | :*Ao atingir o canto inferior o robô deve percorrer todos os quatro lados e fazer a limpeza. | ||

| + | :*Existe um sensor (S) na frente que permite detectar se existe um obstaculo a frente (Sensor = '1') | ||

| + | :*Existe um comando que permite avançar (A) um passo a cada ''clock'' (Avança = '1') | ||

| + | :*Existe um comando que indica para o robô ligar os equipamentos de limpeza (Limpa = '1') | ||

| + | :*Existe um comando para girar o robô 90º no sentido anti-horário (E = '1') ou horário (D = '1'). | ||

| + | :*Implementar a lógica completa da FSM e simular o seu funcionamento para uma área correspondente a 4 passos x 5 passos. | ||

| + | |||

| + | {{collapse top | Cleanbot v1}} | ||

| + | |||

| + | <center> | ||

| + | '''Figura - Projeto da maquina de estados finita do sistema cleanbot v1. Diagrama feito em [[linguagem .dot]].''' | ||

| + | <graphviz> | ||

| + | // FILE: Exemplo_FSM.do | ||

| + | // AUTOR: prof. Marcos Moeck | ||

| + | // Curso de Engenharia de Telecomunicações | ||

| + | // IFSC - Instituto Federal de Santa Catarina | ||

| + | // DATA: 19 nov 2019 | ||

| + | digraph G { | ||

| + | size="12,10!" | ||

| + | labelloc=c fontsize=30 | ||

| + | label ="Cleanbot" | ||

| + | labelloc = t | ||

| + | rankdir = "LR" | ||

| + | //packMode = "clust" | ||

| + | clusterMode = "local" | ||

| + | fixedsize = true | ||

| + | splines = true | ||

| + | node [style=filled, shape=circle, style="rounded,filled"] | ||

| + | // node [width = 2, height = 1,labelloc=c fontsize=17, style=filled, shape=circle, style="rounded,filled"] | ||

| + | |||

| + | edge [arrowsize=0.5] | ||

| + | //Estado inicial | ||

| + | Inicio [shape=Mdiamond]; | ||

| + | Fim [shape=Msquare]; | ||

| + | |||

| + | // Inicialização - ir para o canto superior esquerdo | ||

| + | I1 [color="#7777FF", label = "I1 \nA = 1"] | ||

| + | I2 [color="#7777FF", label = "I2 \nE = 1"] | ||

| + | I3 [color="#7777FF", label = "I3 \nA = 1"] | ||

| + | I4 [color="#7777FF", label = "I4 \nD = 1"] | ||

| + | I5 [color="#7777FF", label = "I5 \nD = 1"] | ||

| + | |||

| + | A1 [color="#77FF77", label = "A1 \nA = 1"] | ||

| + | R1 [color="#77FF77", label = "R1 \nD = 1 \nA=1"] | ||

| + | R2 [color="#77FF77", label = "R2 \nD = 1"] | ||

| + | A2 [color="#77FF77", label = "A2 \nA = 1"] | ||

| + | R3 [color="#77FF77", label = "R3 \nE = 1 \nA = 1"] | ||

| + | R4 [color="#77FF77", label = "R4 \nE = 1"] | ||

| + | |||

| + | Inicio -> W1 [label = "I = 1"] | ||

| + | W1 -> I1 [label = "I = 0"] | ||