Mudanças entre as edições de "DLP29006-Engtelecom(2019-1) - Prof. Marcos Moecke"

| (32 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 1 003: | Linha 1 003: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 5 - Código Sequencial}} |

===Unidade 5 - Código Sequencial=== | ===Unidade 5 - Código Sequencial=== | ||

| Linha 1 215: | Linha 1 215: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 6 - Projeto a nível de Sistema}} |

<!-- | <!-- | ||

| Linha 1 237: | Linha 1 237: | ||

:* Remodelar o projeto do contador 0 a 9 com saída SSD para usar um componente para o contador e outro para o conversor de BCD para SSD. | :* Remodelar o projeto do contador 0 a 9 com saída SSD para usar um componente para o contador e outro para o conversor de BCD para SSD. | ||

| − | |||

:* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

Assim a entity Timer00_99 | Assim a entity Timer00_99 | ||

| Linha 1 289: | Linha 1 288: | ||

::*Exemplo: Detector de Paridade Ex. 8.3 | ::*Exemplo: Detector de Paridade Ex. 8.3 | ||

:* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 213 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ; Aula 32 e 33 (13 e 16 mai): | ||

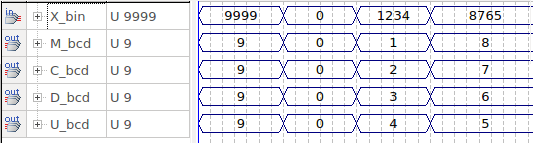

| + | *Implementar o timer00a99 em projeto hierarquico | ||

| + | <center> | ||

| + | [[Arquivo:timer00a99RTL.png]] | ||

| + | </center> | ||

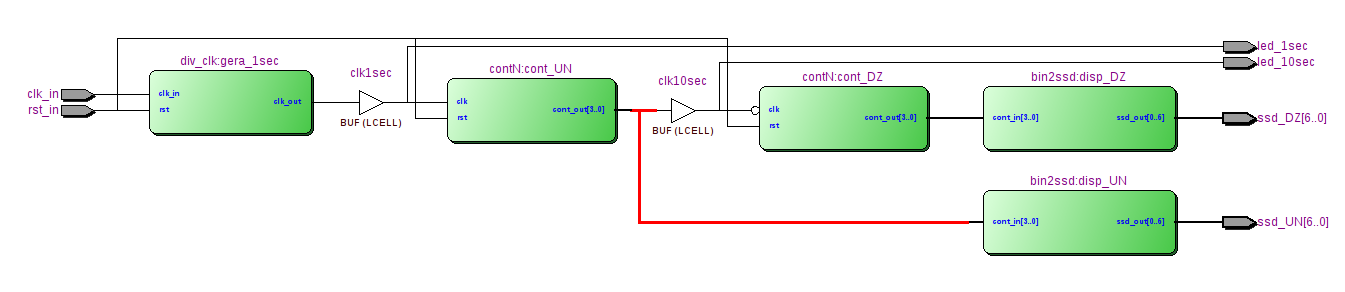

| + | *Fazer a simulação de 110 segundos usando o MODELSIM. | ||

| + | :*Use um clock compativel com o divisor utilizado no div_clock | ||

| + | <center> | ||

| + | [[Arquivo:timer00a99SIM.png]] | ||

| + | </center> | ||

| + | *Testar o timer00a99 no kit DE2-115 | ||

| + | :* Usar uma chave PUSH-BOTTON como reset. | ||

| + | :* Usar o clk de 50 MHz da placa | ||

| + | :* Usar dois displays SSD para mostrar a contagem de 00 a 99 segundos | ||

| + | :* Usar um led para mostrar o segundo e outro para mostrar a dezena de segundos. | ||

| + | *Verificar se o circuito funciona como esperado. | ||

| + | :*Anote os problemas ocorridos e as soluções adotadas. | ||

| + | |||

| + | |||

| + | |||

<!-- | <!-- | ||

| Linha 1 544: | Linha 1 564: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 7 - Maquinas de Estado Finitas}} |

===Unidade 7 - Maquinas de Estado Finitas=== | ===Unidade 7 - Maquinas de Estado Finitas=== | ||

| − | * | + | * 6 AULAS |

| − | + | ||

| − | ; Aula 37 ( | + | ; Aula 37 (mai): |

*Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

:* O que é uma FSM - Finite State Machine | :* O que é uma FSM - Finite State Machine | ||

| Linha 1 626: | Linha 1 646: | ||

:* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| − | --> | + | ; Aula 38 (mai): |

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* Maquina FSM . | ||

| + | :*Implementar a FSM para uma sinaleira manual para duas vias. A mudança do sinal deve ser feito a partir do acionamento de uma chave por um guarda. | ||

| + | <code> | ||

| + | ENTITY sinal_manual IS | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | guarda: IN STD_LOGIC; | ||

| + | LVd1, LAm1, LVm1 : OUT std_logic; -- Lampadas da Via 1 | ||

| + | LVd2, LAm2, LVm2 : OUT std_logic -- Lampadas da Via 2 | ||

| + | ); | ||

| + | END entity ; | ||

| + | </syntaxhighlight> | ||

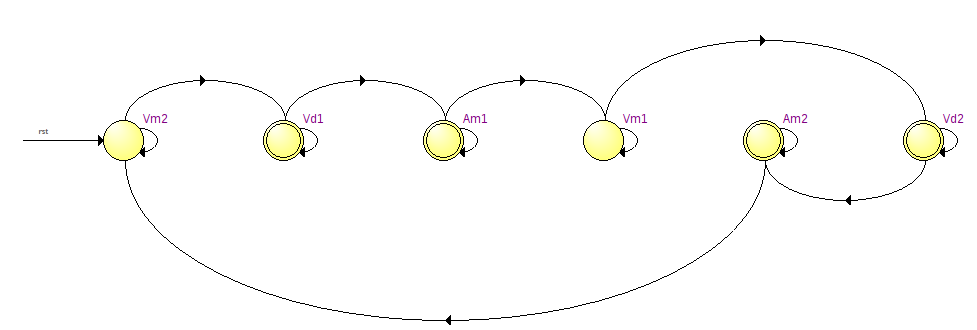

| + | O diagrama da FSM deve ser algo parecido com o mostrado abaixo | ||

| + | <center> | ||

| + | [[Arquivo:FSMSinaleiraManual.png|800px]] | ||

| + | </center> | ||

| + | *Note que se o sinal guarda permanece alto por mais que um clock, ocorre a mudança de mais de um estado. Para evitar esse problema pode ser utilizada a técnica de usar um FLAG, ou estados de WAIT no qual se aguarda o retorno dos sinal para baixo antes de avançar para o próximo estado. | ||

| + | |||

| + | |||

| + | ; Aula 39 (mai): | ||

| + | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

| + | :* Maquina FSM temporizada. | ||

| + | :*Implementar a maquina temporizada para uma sinaleira automática para duas vias. | ||

| + | <code> | ||

| + | ENTITY sinal_auto IS | ||

| + | GENERIC (TVd1: natural := 300; TVd2: natural := 120; TAm: natural := 10); | ||

| + | PORT ( | ||

| + | clk, rst : IN STD_LOGIC; | ||

| + | LVd1, LAm1, LVm1 : OUT std_logic; -- Lampadas da Via 1 | ||

| + | LVd2, LAm2, LVm2 : OUT std_logic -- Lampadas da Via 2 | ||

| + | ); | ||

| + | END entity ; | ||

| + | </syntaxhighlight> | ||

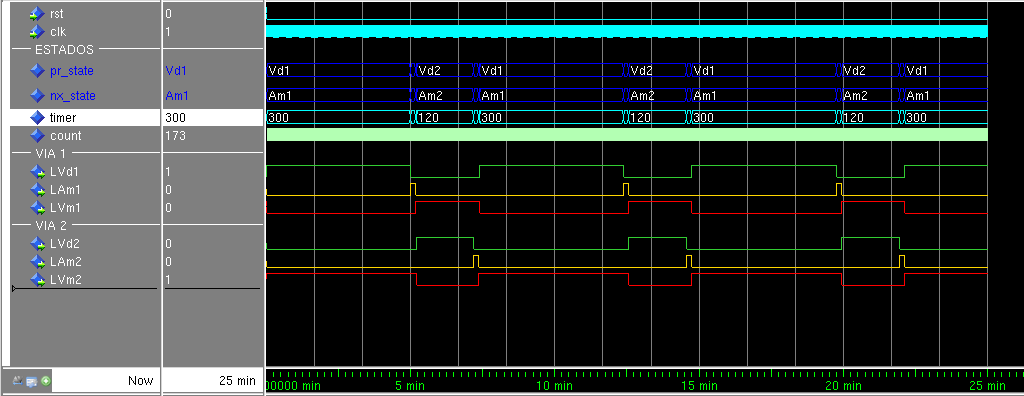

| + | Os tempos '''TVd1''' e '''TVd2''' são os tempos em segundos para verde das vias 1 e 2 respectivamente. '''TAm''' é o tempo em segundos que fica em amarelo em ambas vias. | ||

| + | |||

| + | A simulação no ModelSim da sinaleira deve resultar em algo conforme mostrado abaixo: | ||

| + | <center> | ||

| + | [[Arquivo:SimSinaleiraAutom.png|800px]] | ||

| + | </center> | ||

| + | |||

| + | *'''DICA:''' Use na simulação comandos que automatizam o processo através de um script '''tb_sinal_auto.do''' | ||

| + | <code> | ||

| + | vcom -93 -work work {../../sinal_auto.vhd} | ||

| + | vsim work.sinal_auto | ||

| + | do wave.do | ||

| + | force -freeze sim:/sinal_auto/clk 1 0, 0 {0.5sec} -r {1 sec} | ||

| + | force -freeze sim:/sinal_auto/rst 1 0, 0 0.01 sec | ||

| + | run 25 min | ||

| + | </syntaxhighlight> | ||

| + | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 8 - Testbench}} |

===Unidade 8 - Testbench=== | ===Unidade 8 - Testbench=== | ||

* 2 AULAS | * 2 AULAS | ||

| − | + | ; Aula 40 (27 mai): | |

| − | ; Aula | ||

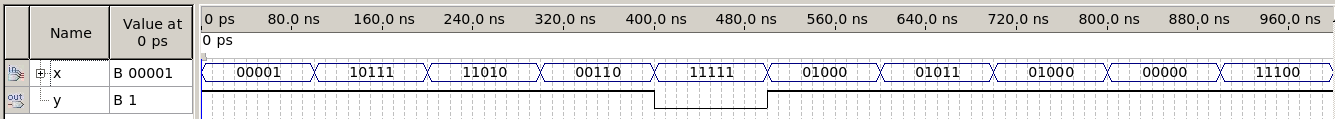

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

:*Tipos de simulação: | :*Tipos de simulação: | ||

| Linha 1 646: | Linha 1 716: | ||

::8) simulação temporal (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ::8) simulação temporal (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída. | ||

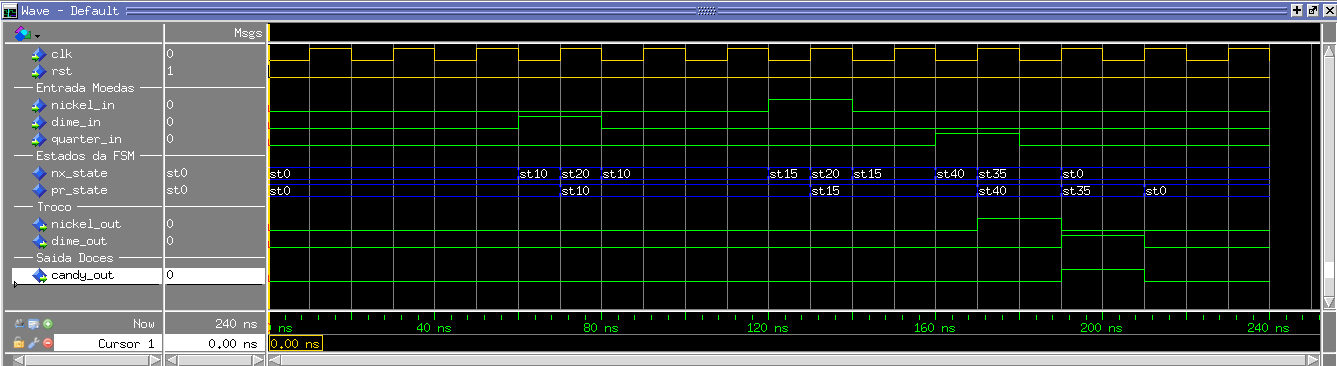

:* Simular a maquina de venda de doces Ex 11.1 | :* Simular a maquina de venda de doces Ex 11.1 | ||

| + | |||

<!-- | <!-- | ||

:*Exemplo de Conversor Binário para Gray (Exercício 9.7) | :*Exemplo de Conversor Binário para Gray (Exercício 9.7) | ||

| Linha 1 669: | Linha 1 740: | ||

--> | --> | ||

| − | |||

::'''DICA''': Use o comando do Quartus II para gerar um template para o testbench. Selecione cada componente como TOP LEVEL e faça a ANÁLISE E SÍNTESE em seguida ('''Processing > Start > Start Test Bench Template Writer'''). | ::'''DICA''': Use o comando do Quartus II para gerar um template para o testbench. Selecione cada componente como TOP LEVEL e faça a ANÁLISE E SÍNTESE em seguida ('''Processing > Start > Start Test Bench Template Writer'''). | ||

:* Criação de sinais para Test Bench em VHDL | :* Criação de sinais para Test Bench em VHDL | ||

| Linha 1 750: | Linha 1 820: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

| + | ;Aula 41 (7 jun): | ||

| + | *Revisão para avaliação A2 | ||

| + | |||

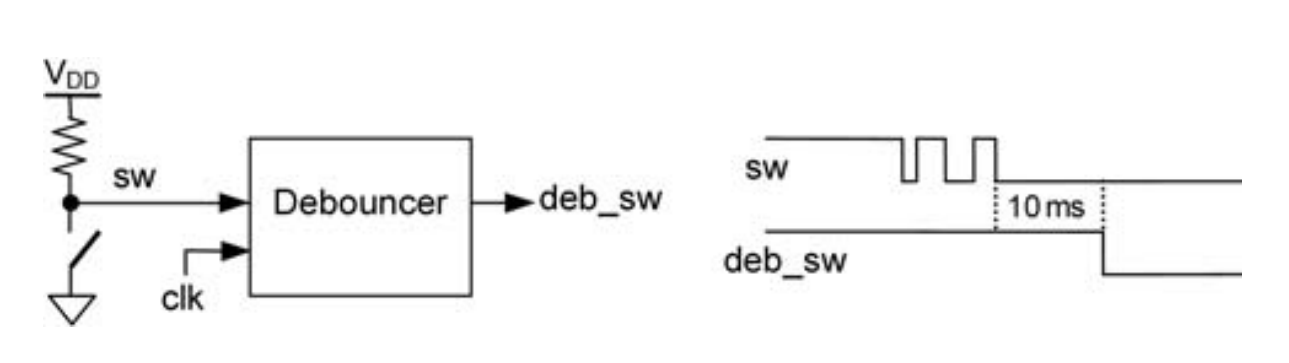

| + | *Implementar um ''debouncer'' de chave mecânica, considerando que o período de ''bouncing'' é de no máximo 10ms. | ||

| + | :*Considere que existe disponível um sinal de clock de 1ms. | ||

| + | |||

| + | <center> | ||

| + | [[Arquivo:DeboucerFig6_18.jpg | 800px]] | ||

| + | </center> | ||

| + | FONTE: Pedroni. | ||

| + | *Usando um clock de 50MHz, gere os sinais de clock com duração de 1ms e de 1 segundo. | ||

| + | :*Use duas instância de um componente '''divisor de clock''' para fazer o circuito hierárquico. | ||

| + | |||

| + | ;Aula 42 (10 jun): | ||

| + | *Avaliação A2 | ||

{{collapse top| expand=true | Unidade 9 - Projeto Final}} | {{collapse top| expand=true | Unidade 9 - Projeto Final}} | ||

| Linha 1 757: | Linha 1 842: | ||

===Unidade 9 - Projeto Final=== | ===Unidade 9 - Projeto Final=== | ||

* 8 AULAS | * 8 AULAS | ||

| − | + | ;Aula 40 (07 jun): | |

| − | ;Aula | + | *Projeto a nível de Sistema. |

| − | * Projeto Final - | + | *Especificação do projeto final: |

| + | :*Objetivo: transmitir através de um transmissor serial assíncrono uma mensagem ASCII. | ||

| + | :*Especificação: A especificação foi informada para os alunos em sala, e estes são responsáveis por criar o texto de especificação do sistema, incluindo detalhes de forma de testes. | ||

| + | |||

| + | ;Aula 43 (14 jun): | ||

| + | *Equipes trabalhando no projeto no Laboratório. | ||

| + | |||

| + | FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. | ||

| + | |||

| + | A instrução '''ASSERT''' é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a sintese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | [rótulo:] assert condição_booleana | ||

| + | [report mensagem] | ||

| + | [severity nivel_severidade]; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | A mensagem pode ser criada usando STRINGs que podem ser concatenadas. | ||

| + | |||

| + | O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [https://www.ics.uci.edu/~jmoorkan/vhdlref/assert.html]. | ||

| + | |||

| + | :* A '''FUNCTION''': declaração, uso, mapeamento posicional x nominal, PURE x IMPURE. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function nome_funçao (lista_parametros_entrada) return tipo_saida is | ||

| + | declarações | ||

| + | begin | ||

| + | afirmações sequenciais | ||

| + | end function; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | :* Uso de '''FUNCTION''' e '''ASSERT'''. | ||

| + | ::* Exemplo: Declaração em ARCHITECTURE Ex.9.1 | ||

| + | ::* Exemplo: Declaração em PACKAGE Ex. 9.2 | ||

| + | ::* Exemplo: Declaração em ENTITY Ex. 9.3 | ||

| + | |||

| + | Abaixo segue um exemplo de cálculo do '''log2''' de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | function log2c (n : integer) return integer is | ||

| + | variable m , p : integer; | ||

| + | begin | ||

| + | m := 0; | ||

| + | p : = 1; | ||

| + | while p < n loop | ||

| + | m : = m + 1; | ||

| + | p := p * 2; | ||

| + | end loop; | ||

| + | return m; | ||

| + | end log2c; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ;Aula 44 (17 jun): | ||

| + | |||

| + | * Projeto Final - Detalhamento em sala da especificação do transmissor serial assíncrono | ||

| + | :*Sugestão detalhada para o gerador de baud-rate, utilizando divisores de clock em paralelo ou em cascata. | ||

| + | :*Sugestão de uso do registrador de deslocamento para o conversor paralelo/serial. | ||

| + | :*Sugestão de uso de uma maquina de estados para o conversor paralelo/serial. | ||

| + | :*Sugestão de entrada da mensagem por chaves binárias ou através de memórias rom (String constante). | ||

| + | :*Sugestão de uso de um conversor de ASCII para sete segmentos | ||

| + | *Alguns detalhes do projeto | ||

| + | :*Definição de prazo: | ||

| + | 1) A parte inicial do projeto deve ter sua especificação concluída até o dia 14/06. | ||

| + | :* O trabalho poderá ser desenvolvido em equipes de até 2 alunos (devido ao número impar de alunos é permitida uma única equipe de 3 alunos). O trabalho também pode ser feito de forma individual, mediante justificativa. | ||

| + | :* Durante as aulas até o final do professor estará disponível para o esclarecimento de dúvidas e orientação das equipes. | ||

| + | :* A presença dos alunos é obrigatória nas aulas de projeto, pois os mesmos estarão sendo avaliados no seu trabalho em equipe e individual durante estas aulas. | ||

| + | |||

| + | ;Aula 45 (24 jun): | ||

| + | *Equipes trabalhando no projeto no Laboratório. | ||

| + | *Dica para uso do tipo STRING no VHDL. | ||

| + | :* O STRING é um tipo predefinido do [[Standard.vhdl | pacote Standard]], sendo um array de uma dimensão onde cada elemento é do tipo CHARACTER. | ||

| + | type string is array (positive range <>) of character; | ||

| + | :* Note que o range é positivo, portanto deve ser de maior que 1, podendo ser usado o range ascendente ou descendente. | ||

| + | :* Cada CHARACTER é uma letra ou simbolo representado por um código ASCII. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | type character is ( | ||

| + | nul, soh, stx, etx, eot, enq, ack, bel, | ||

| + | bs, ht, lf, vt, ff, cr, so, si, | ||

| + | dle, dc1, dc2, dc3, dc4, nak, syn, etb, | ||

| + | can, em, sub, esc, fsp, gsp, rsp, usp, | ||

| + | |||

| + | ' ', '!', '"', '#', '$', '%', '&', ''', | ||

| + | '(', ')', '*', '+', ',', '-', '.', '/', | ||

| + | '0', '1', '2', '3', '4', '5', '6', '7', | ||

| + | '8', '9', ':', ';', '<', '=', '>', '?', | ||

| + | |||

| + | '@', 'A', 'B', 'C', 'D', 'E', 'F', 'G', | ||

| + | 'H', 'I', 'J', 'K', 'L', 'M', 'N', 'O', | ||

| + | 'P', 'Q', 'R', 'S', 'T', 'U', 'V', 'W', | ||

| + | 'X', 'Y', 'Z', '[', '\', ']', '^', '_', | ||

| + | |||

| + | '`', 'a', 'b', 'c', 'd', 'e', 'f', 'g', | ||

| + | 'h', 'i', 'j', 'k', 'l', 'm', 'n', 'o', | ||

| + | 'p', 'q', 'r', 's', 't', 'u', 'v', 'w', | ||

| + | 'x', 'y', 'z', '{', '|', '}', '~', del ); | ||

| + | </syntaxhighlight> | ||

| + | :* As atribuições em um objeto do tipo STRING são realizadas do mesmo modo que em qualquer outro array. Pode ser feita a atribuição em um simples elemento, concatenação, agregação, fatiamento ou combinação dos anteriores. Também estão disponíveis operadores predefinidos como "=", "/=", "<", "<=", ">", ">=" e "&". | ||

| + | :* A concatenação pode ser feita entre 2 strings, ou entre string e caracter ou até mesmo entre dois caracteres para criar uma string. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Declaração dos objetos | ||

| + | constant mensagem1 : String(1 to 25) := "Este é um teste de string"; | ||

| + | constant N: natural := 7; | ||

| + | signal letra1 : character; | ||

| + | signal mensagem2 : string(1 to 29); | ||

| + | signal mensagem3 : string(1 to 3); | ||

| + | signal letra_nat : natural range 0 to 2**N-1; | ||

| + | signal letra_slv : std_logic_vector(N-1 downto 0); | ||

| + | |||

| + | -- Uso dos objetos na ARCHITECTURE | ||

| + | |||

| + | mensagem2 <= mensagem1(1 to 5) & "não " & mensagem1(6 to 25); | ||

| + | -- Resulta na STRING "Este não é um teste de string" | ||

| + | |||

| + | mensagem3 <= 'D' & 'L' & 'P'; | ||

| + | -- Resulta na STRING "DLP" | ||

| − | + | letra1 <= mensagem2(6) | |

| − | + | -- Resulta no CHARACTER 'u' | |

| − | |||

| − | |||

| − | + | -- posiçao da letra na tabela ascii => resulta em natural de 0 a 255 | |

| − | + | letra_nat <= character'pos(letra1); | |

| − | |||

| − | |||

| − | + | -- letra convertida para slv de N bits | |

| − | + | -- necessita de std_logic_1164 e numeric_std | |

| − | + | letra_slv <= std_logic_vector(to_unsigned(character'pos(letra1),N)); | |

| − | + | </syntaxhighlight> | |

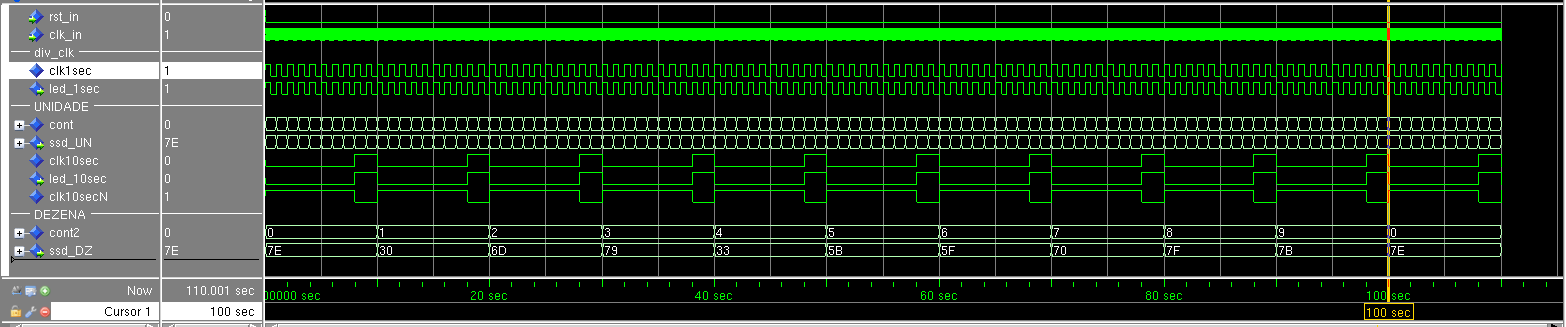

| − | + | <center> | |

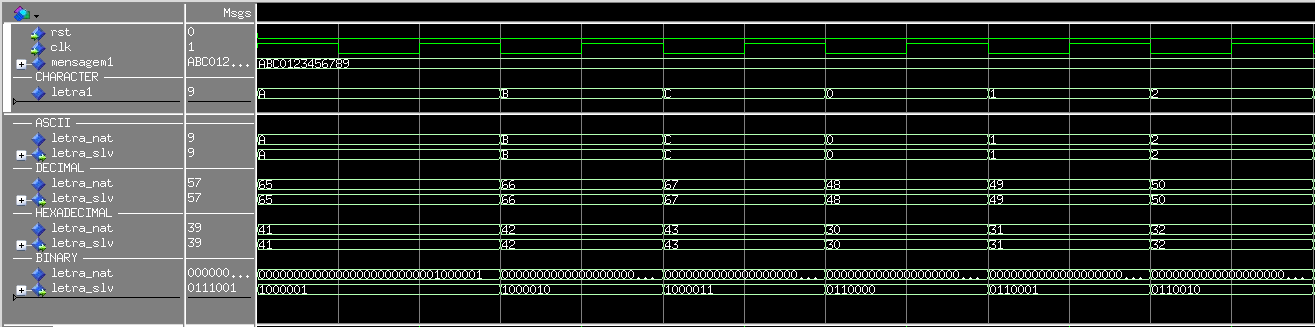

| − | + | Figura - Simulação da transmissão sequencial das letras de uma palavra | |

| − | |||

| − | |||

| − | ;Aula 49 ( | + | [[Arquivo:VHDL_Modelsim_string.png | 1000px]] |

| − | * Projeto Final | + | </center> |

| + | :* Na representação em RADIX-ASCII, tanto o SIGNAL letra_nat e letra_slv são mostrados como CHARACTER ASCII. | ||

| + | :* Na representação em RADIX-DECIMAL, tanto o SIGNAL letra_nat e letra_slv mostram a posição do CHARACTER na definição do TYPE em decimal. | ||

| + | :* Na representação em RADIX-HEXADECIMAL, tanto o SIGNAL letra_nat e letra_slv mostram a posição do CHARACTER na definição do TYPE em hexadecimal. | ||

| + | :* Na representação em RADIX-BINAY, tanto o SIGNAL letra_nat e letra_slv mostram a posição do CHARACTER na definição do TYPE em binário. (esse código corresponde a representação em bits do CHARACTER ASCII) | ||

| + | |||

| + | ====ATUAL==== | ||

| + | ;Aula 46 a 48 (28 jun a 04 jul): | ||

| + | *Trabalho das equipes no projeto | ||

| + | *Término do projeto e simulação no Modelsim | ||

| + | *Teste no kit DE2-115 | ||

| + | |||

| + | ;Aula 49 (05 jul): | ||

| + | * Projeto Final | ||

:*Apresentação do sistema no kit FPGA pelas equipes. | :*Apresentação do sistema no kit FPGA pelas equipes. | ||

| − | + | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

| + | ;Aula 50 (08 jul): | ||

| + | *Avaliação de recuperação R12. | ||

==Avaliações== | ==Avaliações== | ||

| Linha 1 819: | Linha 2 029: | ||

===Projeto Final (PF)=== | ===Projeto Final (PF)=== | ||

* O projeto final é uma atividade de avaliação desenvolvida em equipe, e consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a no mínimo 45% do peso no conceito final. São avaliados no projeto final os quesitos: 1) Sistema desenvolvido (projeto, simulação e realização, demostração do harware); 2) Relatório com a documentação completa do projeto; 3) A avaliação individual do aluno durante o desenvolvimento do projeto e/ou entrevista (avaliação oral). | * O projeto final é uma atividade de avaliação desenvolvida em equipe, e consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a no mínimo 45% do peso no conceito final. São avaliados no projeto final os quesitos: 1) Sistema desenvolvido (projeto, simulação e realização, demostração do harware); 2) Relatório com a documentação completa do projeto; 3) A avaliação individual do aluno durante o desenvolvimento do projeto e/ou entrevista (avaliação oral). | ||

| + | |||

| + | {{collapse top | expand = true | PF - Projeto Final - Sistema de transmissão serial assíncrono (Entrega e prazos ver Moodle)}} | ||

| + | * Cada aluno (ou equipe de 2 alunos) deverá desenvolver um sistema de de transmissão serial assíncrono. | ||

| + | * A descrição exata do funcionamento deve ser obtida com o cliente durante a entrevista de requisitos. | ||

| + | <!-- | ||

| + | mostrado na figura abaixo: | ||

| + | <center> | ||

| + | [[Arquivo:APF_DLP29006_2017_2_Serial_Assincrono.png | 600 px]] | ||

| + | |||

| + | '''Figura 1. Sistema de Comunicação Serial Assíncrono com Endereçamento de A para B''' | ||

| + | |||

| + | [[Arquivo:APF_DLP29006_2017_2_UART_TX.png | 600 px]] | ||

| + | |||

| + | '''Figura 2. Interface transmissora serial''' | ||

| + | |||

| + | [[Arquivo:APF_DLP29006_2017_2_UART_RX.png | 600 px]] | ||

| + | |||

| + | '''Figura 3. Interface receptora serial'''</center> | ||

| + | |||

| + | * As taxa de transmissão deverão ser geradas a partir do clock principal '''CLK50MHz''' do kit a ser utilizado. | ||

| + | * A seleção da Taxa de Transmissão será feita através das chaves '''SW_BAUD_TX'''[1..0] para o transmissor e das '''SW_BAUD_RX'''[1..0] para o receptor. | ||

| + | :Por exemplo: | ||

| + | ::00 => 0.1 bps, 01 => 10 bps, 10 => 9600 bps, 11 => 100 kbps. | ||

| + | * Na transmissão deverá ser enviado um bit paridade (par ou impar) de acordo com a chave seletora '''SW_PARITY'''. | ||

| + | :: 0 => paridade par, 1 => paridade impar. | ||

| + | *No receptor a saída '''RX_ERROR''' deve ser usada para indicar que houve erro na recepção do dado. | ||

| + | <!-- | ||

| + | <center> | ||

| + | [[Arquivo:APF_DLP29006_2017_2_times.png | 900 px]] | ||

| + | </center> | ||

| + | --> | ||

| + | * O sistema no seu '''TOP LEVEL''' deverá ser constituído de um '''Conversor Paralelo Serial''', um '''Conversor Serial Paralelo''', dois '''Geradores de Baud Rate''', um '''Gerador de Paridade''', um '''Detector de Paridade''', um '''Circuito de Entrada de Dados''', e um '''Circuito de Saída de Dados'''. | ||

| + | |||

| + | * O projeto deve ser desenvolvido integrando estes componentes no TOP LEVEL, de modo que neste nível existam apenas conexões entre estes componentes. Recomenda-se utilizar também componentes para a criação dos circuitos no segundo nível. O reuso de componentes já desenvolvidos nas aulas é fortemente encorajado. | ||

| + | |||

| + | * Durante a fase das simulações recomenda-se alterar o valor da frequência do CLK50MHz para um clock menor de modo a viabilizar uma simulação mais rápida. As simulações de cada componente do TOP LEVEL e da integração de todos componentes no TOP LEVEL devem ser feitas no MODELSIM, sendo a última obrigatoriamente feita usando testbench em VHDL. | ||

| + | |||

| + | * O sistema deverá ser implementado, testado e demonstrado no kit de hardware FPGA DE2-115 usando as chaves e leds disponíveis e os pinos da GPIO para acionar circuitos externos. | ||

| + | |||

| + | * O arquivo QAR do projeto, e os arquivos .do e o testbench .vht para o MODELSIM devem ser enviados antecipadamente para o professor para conferencia antes da implementação no kit de hardware. | ||

| + | |||

| + | * Escreva um relatório técnico contendo os resultados em no máximo 10 paginas A4. O relatório além das tabelas com os dados de frequência máxima, número de componente, número de pinos, deverá conter a figura dos circuitos RTL da ENTITY top level com uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. A descrição da função dos pinos no Kit DE2-115 também deve ser feita. | ||

| + | |||

| + | * Para entender o sistema de transmissão recomenda-se consulte materiais complementares sobre [https://en.wikipedia.org/wiki/Asynchronous_serial_communication Comunicação serial assíncrona], [https://en.wikipedia.org/wiki/Parity_bit bit de paridade], [https://en.wikipedia.org/wiki/Universal_asynchronous_receiver-transmitter UART], [https://en.wikipedia.org/wiki/Bit_rate Taxa de bits]. | ||

| + | *Para o teste da transmissão serial pode ser utilizada a interface DB9 disponível nos computadores, em conjunto com o software minicom. | ||

| + | :*[https://manpages.debian.org/testing/minicom/minicom.1.en.html minicom man] | ||

| + | :*[http://processors.wiki.ti.com/index.php/Setting_up_Minicom_in_Ubuntu Instalação e configuração do minicom no linux] | ||

| + | {{collapse bottom}} | ||

<!-- | <!-- | ||

{{collapse top | expand = true | APF - Projeto Final - Sistema de controle de passagem de pedestre (Entrega e prazos ver Moodle)}} | {{collapse top | expand = true | APF - Projeto Final - Sistema de controle de passagem de pedestre (Entrega e prazos ver Moodle)}} | ||

| Linha 1 826: | Linha 2 084: | ||

''FONTE: Imagem cedida por Yan Lucas Martins e Guilherme José Salles Vieira'' | ''FONTE: Imagem cedida por Yan Lucas Martins e Guilherme José Salles Vieira'' | ||

</center> | </center> | ||

| − | + | ||

Alguns detalhes gerais: | Alguns detalhes gerais: | ||

* O semáforo de passagem de pedestres é controlado por botões que os pedestres acionam do lado 1 ou 2 da passagem de pedestres para solicitar a travessia. Ao ser acionado o semáforo pode: 1) liberar imediatamente a passagem do pedestre se não houver veículos circulando na via 1 e via 2. 2) aguardar até T_espera segundos (configurável) se houver veículos circulando. | * O semáforo de passagem de pedestres é controlado por botões que os pedestres acionam do lado 1 ou 2 da passagem de pedestres para solicitar a travessia. Ao ser acionado o semáforo pode: 1) liberar imediatamente a passagem do pedestre se não houver veículos circulando na via 1 e via 2. 2) aguardar até T_espera segundos (configurável) se houver veículos circulando. | ||

| Linha 1 854: | Linha 2 112: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

--> | --> | ||

| + | |||

| + | ====Links uteis para entender o projeto:==== | ||

| + | *[https://www.sciencedirect.com/topics/engineering/stop-bit artigo explicando o que é a transmissão serial.] | ||

| + | *[https://ars.els-cdn.com/content/image/3-s2.0-B9780128006290000255-f25-03-9780128006290.jpg?_ Exemplo de transmissor e receptor assincrono] | ||

| + | *[https://books.google.com.br/books?id=2YgnCgAAQBAJ&pg=PA93&dq=stop+bits&hl=pt-BR&sa=X&ved=0ahUKEwj-luWexeniAhW9FLkGHUslAV8Q6AEISTAE#v=onepage&q=start%20bits&f=false Raspberry Pi Hardware Reference, Warren Gay] pag. 92-94 | ||

===Atividades Extraclasse (AE)=== | ===Atividades Extraclasse (AE)=== | ||

| Linha 2 075: | Linha 2 338: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

{{collapse top | EL6 - Resolução dos exercícios do Cap 6}} | {{collapse top | EL6 - Resolução dos exercícios do Cap 6}} | ||

| − | *Resolva os exercícios do capítulo 6 (1, '''2''', 3-4, '''5''', 6-7, '''9*''', '''10-11''', 12*, 13*, '''14''', | + | *Resolva os exercícios do capítulo 6 (1, '''2''', 3-4, '''5''', 6-7, '''9*''', '''10-11''', 12*, 13*, '''14''', 15*) pag. 172 a 176. |

| + | {{collapse bottom}} | ||

| + | |||

| + | {{collapse top | EL7 - Resolução dos exercícios do Cap 7}} | ||

| + | *Resolva os exercícios da capítulo 7 (9-10) pag. 197. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | | + | {{collapse top | EL8 - Resolução dos exercícios do Cap 8}} |

*Resolva os exercícios da capítulo 8 (1-7, 9*) pag. 219 a 220. | *Resolva os exercícios da capítulo 8 (1-7, 9*) pag. 219 a 220. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | | + | {{collapse top | EL9 - Resolução dos exercícios do Cap 9}} |

*Resolva os exercícios da capítulo 9 (1-4, 6-9) pag. 238 a 239. | *Resolva os exercícios da capítulo 9 (1-4, 6-9) pag. 238 a 239. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | | + | {{collapse top | EL10 - Resolução dos exercícios do Cap 10}} |

| − | *Resolva os exercícios da capítulo 10 (1,2,5 | + | *Resolva os exercícios da capítulo 10 (1,2,5-7, 10-15, 17**) pag. 271 a 274. |

:*Na simulação de cada exercício, faça um versão usando comandos force e run e outra com testbench em vhdl. | :*Na simulação de cada exercício, faça um versão usando comandos force e run e outra com testbench em vhdl. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | |||

==Referências Bibliográficas:== | ==Referências Bibliográficas:== | ||

Edição atual tal como às 15h16min de 28 de junho de 2019

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

-- Isso eh uma linha de comentario y <= a * b ; --o sinal y recebe o resultado da multiplicacao a x b

caracter: 'A' 'x' '#' (com aspas simples) string de caracteres: "IFSC" "teste" "teste123"

bit único: '0' '1' 'Z' (com aspas simples) vetor de bits: "0110" "101001Z" (com aspas duplas) vetor de 1 bit: "0" "1" (com aspas duplas) inteiros: 5 1101 1102 (sem aspas)

0 -> '0' 7 -> "0111" ou b"0111" ou B"0111" 1023 -> "001111111111" ou b"1111111111" ou B"1111111111"

44 -> 5*8^1 + 4*8^0 -> O"54" ou o"54" 1023 -> 1*8^3 + 7*8^2 + 7*8^1 + 7*8^0 -> o"1777" 8#1777#

1023 -> 3*16^2 + 15*16^1 + 15*16^0 = X"3FF" ou x"3FF" 16#3FF#

1023 -> 1023 ou 1_023 1000 -> 1000 ou 1_000 ou 1E3

5#320# (3*5^2 + 2*5^1 + 0*5^0) -> 85 3#201#E4 (2*3^2+0*3^1+1*3^0)*3^4 -> 1539

package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

Ver pag. 60 a 73 de [2]

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY operadores IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

div: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

);

END ENTITY;

ARCHITECTURE type_conv_arch OF operadores IS

BEGIN

-- Inserir o código e definir o tamanho das saidas.

END ARCHITECTURE;

OBS: uso da função resize(object,size) --============================================================================

-- RESIZE Functions

--============================================================================

-- Id: R.1

function RESIZE (ARG: SIGNED; NEW_SIZE: NATURAL) return SIGNED;

-- Result subtype: SIGNED(NEW_SIZE-1 downto 0)

-- Result: Resizes the SIGNED vector ARG to the specified size.

-- To create a larger vector, the new [leftmost] bit positions

-- are filled with the sign bit (ARG'LEFT). When truncating,

-- the sign bit is retained along with the rightmost part.

-- Id: R.2

function RESIZE (ARG: UNSIGNED; NEW_SIZE: NATURAL) return UNSIGNED;

-- Result subtype: UNSIGNED(NEW_SIZE-1 downto 0)

-- Result: Resizes the SIGNED vector ARG to the specified size.

-- To create a larger vector, the new [leftmost] bit positions

-- are filled with '0'. When truncating, the leftmost bits

-- are dropped.

Atributos em VHDL.

Em VHDL existem diversos atributos de sintese que controlam a forma como o processo de "Analysis & Synthesis" é realizado pelo Quartus II. Uma listagem completa pode ser encontrada em:

type fruit is (apple, orange, pear, mango);

attribute enum_encoding : string;

attribute enum_encoding of fruit : type is "11 01 10 00";

entity foo is

port (sel : in std_logic;

data : in std_logic_vector(3 downto 0);

o : out std_logic);

end foo;

architecture rtl of foo is

attribute chip_pin : string;

attribute chip_pin of sel : signal is "C4";

attribute chip_pin of data : signal is "D1, D2, D3, D4";

begin

-- Specify additional code

end architecture;

O uso desse atributo sobrepõe a atribuição dos pinos através da IDE do Quartus II, e por isso não é recomendável. O atributo de síntese chip_pin pode ser usado apenas em portas da entidade "top-level" do projeto. .

signal a,b,c : std_logic;

attribute keep: boolean;

attribute keep of a,b,c: signal is true;

signal a,b,c : std_logic;

attribute preserve: boolean;

attribute preserve of a,b,c: signal is true;

signal reg1: std_logic;

attribute noprune: boolean;

attribute noprune of reg1: signal is true;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

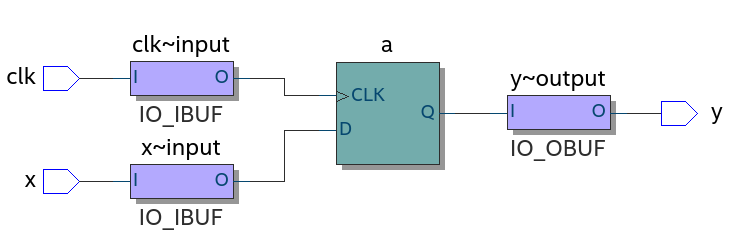

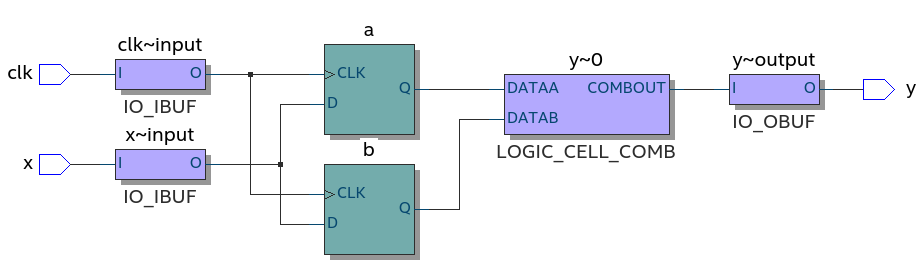

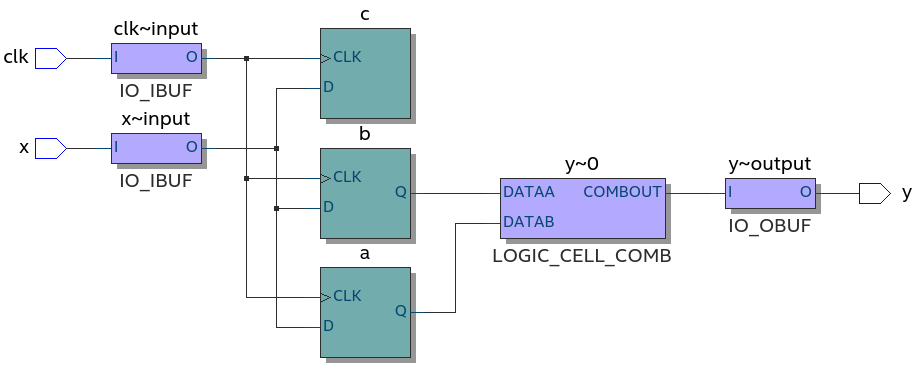

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

attribute attribute_name: attribute_type;

attribute attribute_name of entity_tag [signature]: entity_class is value;

Exemplo:

Uso da instrução ALIAS.

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

label: FOR identificador IN faixa GENERATE

[Parte_Declarativa

BEGIN]

Instruções_concorrentes

...

END GENERATE [label];

---------------------

-- FILE my_pkg.vhd --

---------------------

library ieee;

use ieee.std_logic_1164.all;

package my_pkg is

type a_slv is array(natural range <>) of std_logic_vector (3 downto 0);

end package;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

library ieee work;

use ieee.std_logic_1164.all;

use ieee.numeric_std.all;

use work.my_pkg.all;

entity vector_adder is

generic (N : natural := 4);

port (

a : in a_slv (0 to N-1);

soma : out std_logic_vector (3 downto 0));

end entity;

-- Versão que realiza a soma diretamente, mas que precisa modificar o código de acordo com o número de entradas.

architecture ifsc_v1 of vector_adder is

signal soma_sig : signed(3 downto 0);

begin

-- soma_sig <= signed(a(0)) + signed(a(1))

-- soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2))

soma_sig <= signed(a(0)) + signed(a(1)) + signed(a(2)) + signed(a(3));

soma <= std_logic_vector(soma_sig);

end architecture;

-- Versão que realiza a soma usando um FOR GENERATE

architecture ifsc_v2 of vector_adder is

begin

end architecture;

---------------------------

-- FILE vector_adder.vhd --

---------------------------

configuration ifsc_cfg of vector_adder is

-- for ifsc_v1 end for;

for ifsc_v2 end for;

end configuration;

entity bin2gray is

generic (N : natural := 4 )

port

(

b : in std_logic_vector(____)

g : out std_logic_vector(____)

)

end entity

architecture ifsc of ____ is

begin

end architecture

entity gray2bin is

generic (N : natural := 4 )

port

(

g : in std_logic_vector(____)

b : out std_logic_vector(____)

)

end entity

architecture ifsc of ____ is

begin

end architecture

function "+" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Adds two UNSIGNED vectors that may be of different lengths.

function "-" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(MAX(L'LENGTH, R'LENGTH)-1 downto 0).

-- Result: Subtracts two UNSIGNED vectors that may be of different lengths.

function "*" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED((L'LENGTH+R'LENGTH-1) downto 0).

-- Result: Performs the multiplication operation on two UNSIGNED vectors

-- that may possibly be of different lengths.

function "/" (L, R: UNSIGNED) return UNSIGNED;

-- Result subtype: UNSIGNED(L'LENGTH-1 downto 0)

-- Result: Divides an UNSIGNED vector, L, by another UNSIGNED vector, R.

-- NOTE: If second argument is zero for "/" operator, a severity level of ERROR is issued.

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

Avaliação A1 - UN2, UN3, UN4

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

|

| Unidade 6 - Projeto a nível de Sistema |

|---|

|

Unidade 6 - Projeto a nível de Sistema

Assim a entity Timer00_99 ENTITY timer00_99seg

GENERIC (D : INTEGER;

fclock : INTEGER;

U : INTEGER);

PORT (clk50MHz : IN STD_LOGIC;

RST : IN STD_LOGIC;

clk1seg : OUT STD_LOGIC;

SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6);

SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6));

END ENTITY;

Será declarada como um COMPONENT COMPONENT timer00_99seg

GENERIC (D : INTEGER;

fclock : INTEGER;

U : INTEGER);

PORT (clk50MHz : IN STD_LOGIC;

RST : IN STD_LOGIC;

clk1seg : OUT STD_LOGIC;

SSD_Dseg : OUT STD_LOGIC_VECTOR(0 TO 6);

SSD_Useg : OUT STD_LOGIC_VECTOR(0 TO 6));

END COMPONENT;

comp1 : timer00_99seg

GENERIC MAP (2, 10, 3)

PORT MAP (clk50MHz,RST, clk1seg, SSD_Dseg, SSD_Useg);

comp1 : timer00_99seg

GENERIC MAP ( D => 2, U => 3,

fclock => 10,

PORT MAP ( clk50MHz => clk50MHz,

RST => RST,

clk1seg => clk1seg,

SSD_Dseg => SSD_Dseg,

SSD_Useg => SSD_Useg);

|

| Unidade 7 - Maquinas de Estado Finitas |

|---|

Unidade 7 - Maquinas de Estado Finitas

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END < entity_name > ;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF (clk'EVENT AND clk = '1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

CASE pr_state IS

WHEN A =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= C;

...

ELSE

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END < architecture_name > ;

|

| Unidade 8 - Testbench | ||||||||

|---|---|---|---|---|---|---|---|---|

Unidade 8 - Testbench

|

- Aula 41 (7 jun)

- Revisão para avaliação A2

- Implementar um debouncer de chave mecânica, considerando que o período de bouncing é de no máximo 10ms.

- Considere que existe disponível um sinal de clock de 1ms.

FONTE: Pedroni.

- Usando um clock de 50MHz, gere os sinais de clock com duração de 1ms e de 1 segundo.

- Use duas instância de um componente divisor de clock para fazer o circuito hierárquico.

- Aula 42 (10 jun)

- Avaliação A2

| Unidade 9 - Projeto Final |

|---|

Unidade 9 - Projeto Final

FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a sintese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: [rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas. O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. ERROR é o valor "default" [9].

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

end function;

Abaixo segue um exemplo de cálculo do log2 de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

1) A parte inicial do projeto deve ter sua especificação concluída até o dia 14/06.

type string is array (positive range <>) of character;

type character is (

nul, soh, stx, etx, eot, enq, ack, bel,

bs, ht, lf, vt, ff, cr, so, si,

dle, dc1, dc2, dc3, dc4, nak, syn, etb,

can, em, sub, esc, fsp, gsp, rsp, usp,

' ', '!', '"', '#', '$', '%', '&', ''',

'(', ')', '*', '+', ',', '-', '.', '/',

'0', '1', '2', '3', '4', '5', '6', '7',

'8', '9', ':', ';', '<', '=', '>', '?',

'@', 'A', 'B', 'C', 'D', 'E', 'F', 'G',

'H', 'I', 'J', 'K', 'L', 'M', 'N', 'O',

'P', 'Q', 'R', 'S', 'T', 'U', 'V', 'W',

'X', 'Y', 'Z', '[', '\', ']', '^', '_',

'`', 'a', 'b', 'c', 'd', 'e', 'f', 'g',

'h', 'i', 'j', 'k', 'l', 'm', 'n', 'o',

'p', 'q', 'r', 's', 't', 'u', 'v', 'w',

'x', 'y', 'z', '{', '|', '}', '~', del );

-- Declaração dos objetos

constant mensagem1 : String(1 to 25) := "Este é um teste de string";

constant N: natural := 7;

signal letra1 : character;

signal mensagem2 : string(1 to 29);

signal mensagem3 : string(1 to 3);

signal letra_nat : natural range 0 to 2**N-1;

signal letra_slv : std_logic_vector(N-1 downto 0);

-- Uso dos objetos na ARCHITECTURE

mensagem2 <= mensagem1(1 to 5) & "não " & mensagem1(6 to 25);

-- Resulta na STRING "Este não é um teste de string"

mensagem3 <= 'D' & 'L' & 'P';

-- Resulta na STRING "DLP"

letra1 <= mensagem2(6)

-- Resulta no CHARACTER 'u'

-- posiçao da letra na tabela ascii => resulta em natural de 0 a 255

letra_nat <= character'pos(letra1);

-- letra convertida para slv de N bits

-- necessita de std_logic_1164 e numeric_std

letra_slv <= std_logic_vector(to_unsigned(character'pos(letra1),N));

Figura - Simulação da transmissão sequencial das letras de uma palavra

ATUAL

|

- Aula 50 (08 jul)

- Avaliação de recuperação R12.

Avaliações

Atividade Relâmpago (AR)

As atividades relâmpago são atividades avaliativas opcionais que darão BôNUS adicionais ao aluno na próxima avaliação. Elas normalmente consistem de soluções simples para algum problema ou sistema. Elas são enunciadas na aula, e o prazo e a entrega serão definidos no Moodle. Não são aceitas entregas tardias, e apenas 2 alunos podem receber o bonus. A pontuação das atividades é informada a cada atividade.

Avaliação A1

- Conteúdo avaliado serão as unidades 2 a 4 (cap 1 - 5)

- Data da avaliação (25/04/2019) - Local: LabSiDi.

Avaliação A2

- Conteúdo avaliado serão as unidades 5 a 7 (Cap 6 a 9)

- Data da avaliação () - Local: LabSiDi.

Recuperação R12

- Esta avaliação somente será realizada se necessária, e deverá ser feita na última semana letiva do semestre

- Conteúdo avaliado será as unidades 2 a 7

- Data da avaliação () - Local: LabSiDi.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues:

- VHDL Quick Reference - SynthWorks

- VHDL Types and Operators Quick Reference - SynthWorks

- ModelSim Quick Reference - SynthWorks

- Tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni.

- Arquivo:Numeric std conversions.png

- Dica use também como fonte de consulta os templates do Quartus.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma Moodle com os arquivos solicitados.

Projeto Final (PF)

- O projeto final é uma atividade de avaliação desenvolvida em equipe, e consiste no desenvolvimento de um sistema que aplica os conhecimento adquiridos durante o semestre. A avaliação do projeto final corresponde a no mínimo 45% do peso no conceito final. São avaliados no projeto final os quesitos: 1) Sistema desenvolvido (projeto, simulação e realização, demostração do harware); 2) Relatório com a documentação completa do projeto; 3) A avaliação individual do aluno durante o desenvolvimento do projeto e/ou entrevista (avaliação oral).

| PF - Projeto Final - Sistema de transmissão serial assíncrono (Entrega e prazos ver Moodle) |

|---|

|

Links uteis para entender o projeto:

- artigo explicando o que é a transmissão serial.

- Exemplo de transmissor e receptor assincrono

- Raspberry Pi Hardware Reference, Warren Gay pag. 92-94

Atividades Extraclasse (AE)

- Entrega dos Atividades Extraclasse ao longo do semestre AE(0) a AE(N). A entrega, detalhes e prazos serão indicados na plataforma Moodle.

Estudos livres sem entrega de documentação (EL)

- Os estudos livres são fortemente recomendados aos alunos como forma de melhor compreender o assunto estudado em cada unidade. Nas listas de exemplos e exercícios, os essenciais estão destacados em negrito. Não há prazos nem entregas desses estudos no Moodle, mas pede-se que os alunos realizem esses estudos e tirem suas dúvidas nas aulas destinadas a resolução de exercícios, ou nos minutos iniciais das aulas.

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL3 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL4 - Resolução dos exercícios do Cap 5 |

|---|

|

| EL6 - Resolução dos exercícios do Cap 6 |

|---|

|

| EL7 - Resolução dos exercícios do Cap 7 |

|---|

|

| EL8 - Resolução dos exercícios do Cap 8 |

|---|

|

| EL9 - Resolução dos exercícios do Cap 9 |

|---|

|

| EL10 - Resolução dos exercícios do Cap 10 |

|---|

|

Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335