Mudanças entre as edições de "Experimento 4 para Circuitos Lógicos"

Ir para navegação

Ir para pesquisar

| (21 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| − | |||

__NOTOC__ | __NOTOC__ | ||

| + | ==Comparador de igualdade e programação no FPGA== | ||

;Objetivos: | ;Objetivos: | ||

| − | * Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas | + | * Compreender o funcionamento das portas XOR e XNOR; |

| + | * Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas XNOR; | ||

* Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | * Obter o sinal de saída simulado usando o QSIM - diagrama funcional; | ||

| − | |||

* Definir a pinagem de saída; | * Definir a pinagem de saída; | ||

| − | * Programar o FPGA para implementar um comparador de | + | * Programar o FPGA para implementar um comparador de igualdade. |

| − | |||

;Materiais necessários: | ;Materiais necessários: | ||

#CI [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386 XOR](disponível na biblioteca da ALTERA) | #CI [http://www.ti.com/lit/ds/symlink/sn74ls386a.pdf 74X386 XOR](disponível na biblioteca da ALTERA) | ||

| Linha 13: | Linha 12: | ||

#Computador com software Quartus II da Altera. | #Computador com software Quartus II da Altera. | ||

#Kit DE2-115; | #Kit DE2-115; | ||

| + | |||

=Porta Xor= | =Porta Xor= | ||

| + | *Símbolo: | ||

| + | [[Arquivo:pxor.png|80px]] | ||

| − | + | *Expressão booleana: | |

| − | |||

<math> A \oplus B = A \cdot \ \overline B + \ \overline A \cdot B </math> | <math> A \oplus B = A \cdot \ \overline B + \ \overline A \cdot B </math> | ||

| + | *Tabela verdade: | ||

{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

! colspan="2" style="background: #efefef;" | Entradas | ! colspan="2" style="background: #efefef;" | Entradas | ||

| Linha 38: | Linha 40: | ||

=Diagrama Esquemático do comparador de igualdade= | =Diagrama Esquemático do comparador de igualdade= | ||

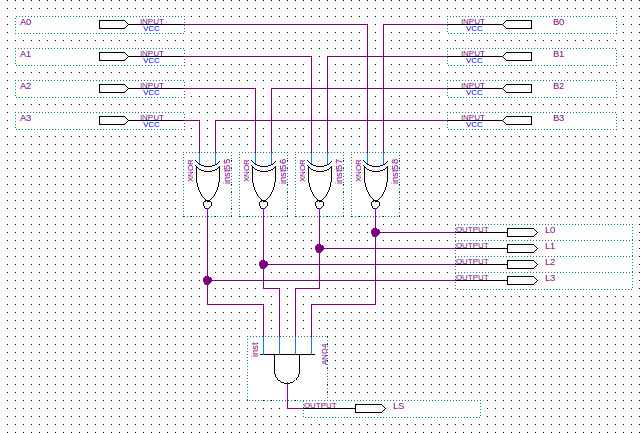

| − | Abra o Quartus II (versão 13.1) e insira o diagrama esquemático com portas XNor, conforme a figura abaixo. | + | Abra o Quartus II (versão 13.0.1 SE) e insira o diagrama esquemático com portas XNor, conforme a figura abaixo. |

| + | [[Imagem:exp4_diagr.png|650px|center]] | ||

| + | |||

| + | Após salvar o arquivo como portaXNor.bdf em uma pasta vazia com nome Exp4, e crie um projeto portasXNor.qpf utilizando a família family='''Cyclone IV E''' com o dispositivo device='''EP4CE115F29C7'''. Após isso compile o projeto. | ||

| + | |||

| + | ==Obter o sinal de saída simulado usando o QSIM - diagrama funcional== | ||

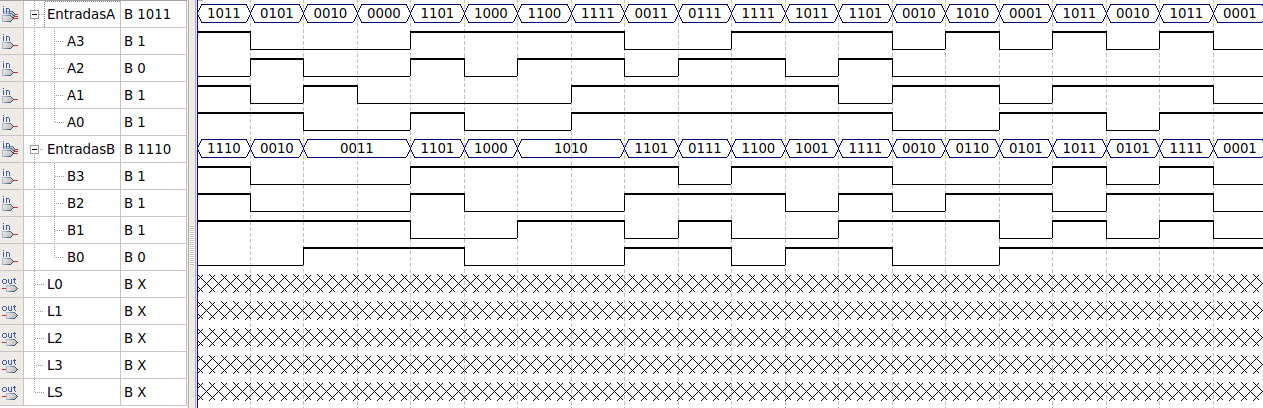

| + | *Agrupe as respectivas entradas e desenhe a forma de onda dos sinais selecionando a linha do agrupamento e clicando [[Imagem:random.png |Random]](Generage random values > Every grid interval) gerando formas de onda aleatórias, e salve com o nome EntradaFunc.vwf. | ||

| + | [[Imagem:Exp4_entrada.png|900px]] | ||

| + | |||

| + | *Analise o resultado obtido e confira se corresponde a resposta do circuito implementado. | ||

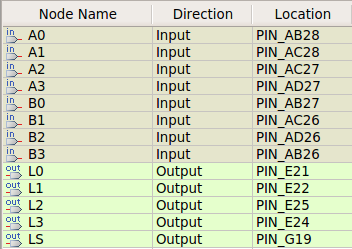

| − | [[Imagem: | + | ==Definir a pinagem de saída== |

| + | *Clique em [[Imagem:pinplaner.png]] para configurar a pinagem escolhida. | ||

| + | *Atribua os pinos conforme a [ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2-115/DE2_115.qsf pinagem do kit DE2-115]. | ||

| + | *Utilize os leds de LEDG[0] a LEDG[3] (verdes) para mostrar a saída de cada operação com porta XNor. | ||

| + | *Utilize os switchs para alterar o estado lógico das entradas, indicando-as de A0-A3 e B0-B3. | ||

| + | *Utilize um led LEDR[0](vermelho) para indicar a saída LS. | ||

| + | *Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem: | ||

| + | [[Arquivo:exp4_pinagem.png|300px|center]] | ||

| + | *Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático. | ||

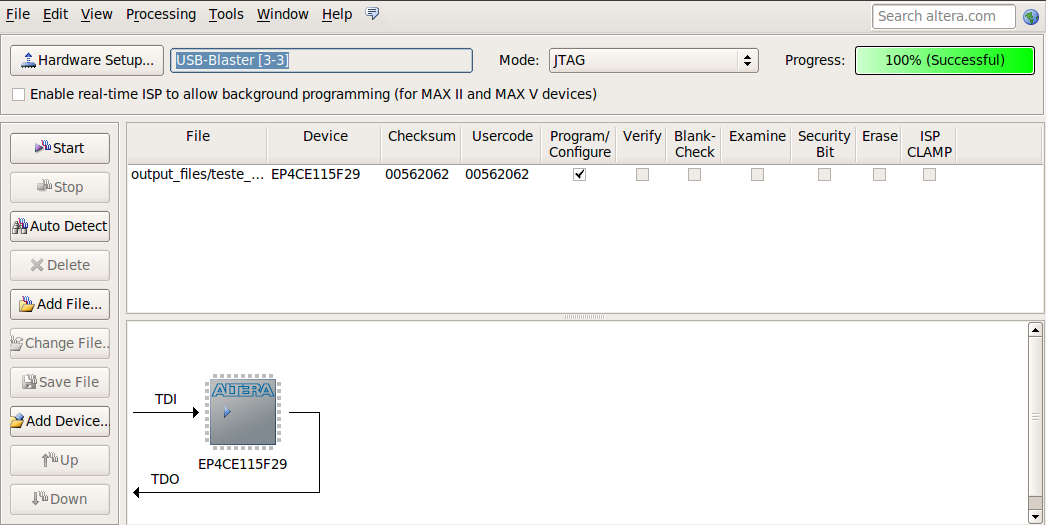

| − | + | ==Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade)== | |

| + | *Use a porta USB-Blaster para fazer a programação na placa DE2-115; | ||

| + | *No Quartus vá em (Tools > Programmer) para abrir a página de programação; | ||

| + | **Selecione o Hardware (Hardware Setup > USB-Blaster); | ||

| + | **Utilize o modo JTAG e clique em Start para começar a programação; | ||

| + | [[Arquivo:Programador.png|700px|center]] | ||

Edição atual tal como às 09h37min de 21 de outubro de 2014

Comparador de igualdade e programação no FPGA

- Objetivos

- Compreender o funcionamento das portas XOR e XNOR;

- Utilizar o diagrama esquemático do Quartus II para inserir um circuito com Portas XNOR;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional;

- Definir a pinagem de saída;

- Programar o FPGA para implementar um comparador de igualdade.

- Materiais necessários

- CI 74X386 XOR(disponível na biblioteca da ALTERA)

- CI 74X266 XNOR(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

- Kit DE2-115;

Porta Xor

- Símbolo:

- Expressão booleana:

- Tabela verdade:

| Entradas | Saídas | |

|---|---|---|

| A | B | S |

| 0 | 0 | 0 |

| 0 | 1 | 1 |

| 1 | 0 | 1 |

| 1 | 1 | 0 |

Diagrama Esquemático do comparador de igualdade

Abra o Quartus II (versão 13.0.1 SE) e insira o diagrama esquemático com portas XNor, conforme a figura abaixo.

Após salvar o arquivo como portaXNor.bdf em uma pasta vazia com nome Exp4, e crie um projeto portasXNor.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7. Após isso compile o projeto.

Obter o sinal de saída simulado usando o QSIM - diagrama funcional

- Agrupe as respectivas entradas e desenhe a forma de onda dos sinais selecionando a linha do agrupamento e clicando

(Generage random values > Every grid interval) gerando formas de onda aleatórias, e salve com o nome EntradaFunc.vwf.

(Generage random values > Every grid interval) gerando formas de onda aleatórias, e salve com o nome EntradaFunc.vwf.

- Analise o resultado obtido e confira se corresponde a resposta do circuito implementado.

Definir a pinagem de saída

- Clique em

para configurar a pinagem escolhida.

para configurar a pinagem escolhida. - Atribua os pinos conforme a pinagem do kit DE2-115.

- Utilize os leds de LEDG[0] a LEDG[3] (verdes) para mostrar a saída de cada operação com porta XNor.

- Utilize os switchs para alterar o estado lógico das entradas, indicando-as de A0-A3 e B0-B3.

- Utilize um led LEDR[0](vermelho) para indicar a saída LS.

- Ao final da configuração dos pinos, o Pin Planner deverá mostrar a seguinte pinagem:

- Compile o projeto. Note que agora a numeração dos pinos também aparece no diagrama esquemático.

Programar o FPGA para implementar um comparador de palavras (ou gerador de paridade)

- Use a porta USB-Blaster para fazer a programação na placa DE2-115;

- No Quartus vá em (Tools > Programmer) para abrir a página de programação;

- Selecione o Hardware (Hardware Setup > USB-Blaster);

- Utilize o modo JTAG e clique em Start para começar a programação;