Mudanças entre as edições de "Deserial/Serial - Pedroni VHDL"

Ir para navegação

Ir para pesquisar

m (→Simulações) |

|||

| (18 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 7: | Linha 7: | ||

{{Collapse top | Código}} | {{Collapse top | Código}} | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| + | -- PROGRAM "Quartus II 32-bit" | ||

| + | -- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version" | ||

| + | -- CREATED "Thu Mar 24 21:22:39 2016" | ||

| + | LIBRARY ieee; | ||

| + | USE ieee.std_logic_1164.all; | ||

| + | |||

| + | LIBRARY work; | ||

| + | |||

| + | entity deserial is | ||

| + | |||

| + | GENERIC (bits : INTEGER := 3; -- Bits do contador interno log2(n) | ||

| + | n : INTEGER := 8 -- Dados seriais transmitidos | ||

| + | ); | ||

| + | PORT | ||

| + | ( | ||

| + | din : IN STD_LOGIC; | ||

| + | inclk0 : IN STD_LOGIC; | ||

| + | areset : IN STD_LOGIC; | ||

| + | locked : OUT STD_LOGIC; | ||

| + | doutS : OUT STD_LOGIC; | ||

| + | count_outD : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0); | ||

| + | count_outS : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0); | ||

| + | doutD : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0) | ||

| + | ); | ||

| + | END entity; | ||

| + | |||

| + | ARCHITECTURE bdf_type OF deserial IS | ||

| + | |||

| + | COMPONENT fast_deserializer | ||

| + | GENERIC (bits : INTEGER; | ||

| + | n : INTEGER | ||

| + | ); | ||

| + | PORT(clk : IN STD_LOGIC; | ||

| + | din : IN STD_LOGIC; | ||

| + | count_out : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0); | ||

| + | dout : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0) | ||

| + | ); | ||

| + | END COMPONENT; | ||

| + | |||

| + | COMPONENT fast_serializer | ||

| + | GENERIC (bits : INTEGER; | ||

| + | n : INTEGER | ||

| + | ); | ||

| + | PORT(clk : IN STD_LOGIC; | ||

| + | din : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0); | ||

| + | dout : OUT STD_LOGIC; | ||

| + | count_out : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0) | ||

| + | ); | ||

| + | END COMPONENT; | ||

| + | |||

| + | COMPONENT altpll0 | ||

| + | PORT(inclk0 : IN STD_LOGIC; | ||

| + | areset : IN STD_LOGIC; | ||

| + | c0 : OUT STD_LOGIC; | ||

| + | locked : OUT STD_LOGIC | ||

| + | ); | ||

| + | END COMPONENT; | ||

| + | |||

| + | SIGNAL s_clk : STD_LOGIC; | ||

| + | SIGNAL deserial_data : STD_LOGIC_VECTOR(n-1 DOWNTO 0); | ||

| + | |||

| + | --Keep | ||

| + | --attribute keep: boolean; | ||

| + | --attribute keep of deserial_data: signal is true; | ||

| + | |||

| + | BEGIN | ||

| + | |||

| + | doutD <= deserial_data; | ||

| + | |||

| + | |||

| + | deserial_inst : fast_deserializer | ||

| + | GENERIC MAP(bits => bits, | ||

| + | n => n | ||

| + | ) | ||

| + | PORT MAP(clk => s_clk, | ||

| + | din => din, | ||

| + | count_out => count_outD, | ||

| + | dout => deserial_data); | ||

| + | |||

| + | |||

| + | serial_inst : fast_serializer | ||

| + | GENERIC MAP(bits => bits, | ||

| + | n => n | ||

| + | ) | ||

| + | PORT MAP(clk => s_clk, | ||

| + | din => deserial_data, | ||

| + | dout => doutS, | ||

| + | count_out => count_outS); | ||

| + | |||

| + | |||

| + | pll0_inst : altpll0 | ||

| + | PORT MAP(inclk0 => inclk0, | ||

| + | areset => areset, | ||

| + | c0 => s_clk, | ||

| + | locked => locked); | ||

| + | |||

| + | |||

| + | END architecture; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

{{Collapse bottom}} | {{Collapse bottom}} | ||

| Linha 14: | Linha 112: | ||

{{Collapse top | Código}} | {{Collapse top | Código}} | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| + | -- Testbench created online at: | ||

| + | -- www.doulos.com/knowhow/perl/testbench_creation/ | ||

| + | -- Copyright Doulos Ltd | ||

| + | -- SD, 03 November 2002 | ||

| + | |||

| + | library IEEE; | ||

| + | use IEEE.Std_logic_1164.all; | ||

| + | use IEEE.Numeric_Std.all; | ||

| + | |||

| + | entity deserial_tb is | ||

| + | GENERIC (bits : INTEGER := 3; | ||

| + | n : INTEGER := 8 | ||

| + | ); | ||

| + | end entity; | ||

| − | + | architecture bench of deserial_tb is | |

| − | |||

| − | + | component deserial | |

| − | + | GENERIC (bits : INTEGER := 2; | |

| − | + | n : INTEGER := 4 | |

| − | + | ); | |

| + | PORT | ||

| + | ( | ||

| + | din : IN STD_LOGIC; | ||

| + | inclk0 : IN STD_LOGIC; | ||

| + | areset : IN STD_LOGIC; | ||

| + | locked : OUT STD_LOGIC; | ||

| + | doutD : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0); | ||

| + | doutS : OUT STD_LOGIC; | ||

| + | count_outD : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0); | ||

| + | count_outS : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0) | ||

| + | ); | ||

| + | end component; | ||

| − | + | signal inclk0: std_logic := '0'; | |

| + | signal areset : std_logic := '0'; | ||

| + | signal din: std_logic := '0'; | ||

| + | signal count_outD: std_logic_vector(bits-1 downto 0); | ||

| + | signal count_outS: std_logic_vector(bits-1 downto 0); | ||

| + | signal doutD : std_logic_vector(n-1 downto 0); | ||

| + | signal doutS : std_logic; | ||

| − | * | + | constant clock_half_period: time := 10 ns; |

| + | constant din_rate: time := clock_half_period*2*bits; | ||

| + | signal stop_the_clock: boolean; | ||

| + | begin | ||

| + | |||

| + | -- Insert values for generic parameters !! | ||

| + | uut: deserial | ||

| + | generic map (bits => 3, n => 8 ) | ||

| + | port map ( inclk0 => inclk0, | ||

| + | areset => areset, | ||

| + | din => din, | ||

| + | count_outD => count_outD, | ||

| + | count_outS => count_outS, | ||

| + | doutD => doutD, | ||

| + | doutS => doutS); | ||

| + | -- Geraç~ao do estimulo clk | ||

| + | |||

| + | inclk0 <= not inclk0 after clock_half_period; | ||

| + | |||

| + | stimulus: process | ||

| + | begin | ||

| + | wait for 25 ns; | ||

| + | -- Geraç~ao do din | ||

| + | din <= '1'; | ||

| + | -- duraç~ao do din = 4 periodos de clk | ||

| + | wait for din_rate; | ||

| + | din <= '0'; | ||

| + | wait for din_rate; | ||

| + | din <= '1'; | ||

| + | wait for din_rate; | ||

| + | din <= '0'; | ||

| + | wait for din_rate; | ||

| + | end process; | ||

| + | |||

| + | end; | ||

| + | </syntaxhighlight> | ||

| + | {{Collapse bottom}} | ||

| + | |||

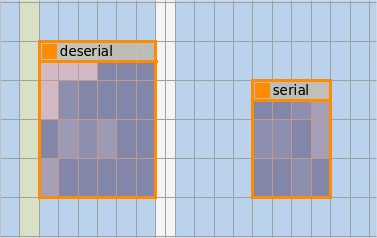

| + | *Chip Planner: | ||

| + | [[Arquivo: deserial_chip.png | 300px]] | ||

==Simulações== | ==Simulações== | ||

| Linha 32: | Linha 200: | ||

! colspan="1" style="background: #efefef;" | Nº Bits | ! colspan="1" style="background: #efefef;" | Nº Bits | ||

! colspan="1" style="background: #efefef;" | ALMs | ! colspan="1" style="background: #efefef;" | ALMs | ||

| − | |||

! colspan="1" style="background: #efefef;" | Potência (mW) | ! colspan="1" style="background: #efefef;" | Potência (mW) | ||

| + | ! colspan="1" style="background: #efefef;" | Report Path | ||

| + | ! colspan="1" style="background: #efefef;" | Report Timing | ||

| + | ! colspan="1" style="background: #efefef;" | Caminho crítico | ||

| + | ! colspan="1" style="background: #efefef;" | Logic Block | ||

| + | ! colspan="1" style="background: #efefef;" | Optimization | ||

| + | ! colspan="1" style="background: #efefef;" | Seed | ||

|- | |- | ||

| − | | | + | | 4 || || || 4.021 || 4.253 || deserial0-dout[0]-internal[3] || S || Balanced || 1 |

| − | |- | ||

| − | |||

|- | |- | ||

| − | | | + | | 32 || || || 18.954 || 19.186 || deserial1-dout[0]-internal[31] || S || Balanced || 1 |

|- | |- | ||

| − | | | + | | 128 || || || 64.238 || 64.791 (VIOLATED) || deserial0-dout[0]-internal[127]|| Auto || Balanced || 1 |

|- | |- | ||

|} | |} | ||

Edição atual tal como às 11h09min de 26 de abril de 2016

Estrutura

- Circuito deserializador/serializador (Recebe logic, sai logic_vector)

- Possui um contador de teste afim de depuração (Exemplo do Loop: conta até 3 e joga o bit que está na entrada ṕara a saída.)

VHDL

| Código |

|---|

-- PROGRAM "Quartus II 32-bit"

-- VERSION "Version 13.0.1 Build 232 06/12/2013 Service Pack 1 SJ Full Version"

-- CREATED "Thu Mar 24 21:22:39 2016"

LIBRARY ieee;

USE ieee.std_logic_1164.all;

LIBRARY work;

entity deserial is

GENERIC (bits : INTEGER := 3; -- Bits do contador interno log2(n)

n : INTEGER := 8 -- Dados seriais transmitidos

);

PORT

(

din : IN STD_LOGIC;

inclk0 : IN STD_LOGIC;

areset : IN STD_LOGIC;

locked : OUT STD_LOGIC;

doutS : OUT STD_LOGIC;

count_outD : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

count_outS : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

doutD : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0)

);

END entity;

ARCHITECTURE bdf_type OF deserial IS

COMPONENT fast_deserializer

GENERIC (bits : INTEGER;

n : INTEGER

);

PORT(clk : IN STD_LOGIC;

din : IN STD_LOGIC;

count_out : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

dout : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0)

);

END COMPONENT;

COMPONENT fast_serializer

GENERIC (bits : INTEGER;

n : INTEGER

);

PORT(clk : IN STD_LOGIC;

din : IN STD_LOGIC_VECTOR(n-1 DOWNTO 0);

dout : OUT STD_LOGIC;

count_out : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0)

);

END COMPONENT;

COMPONENT altpll0

PORT(inclk0 : IN STD_LOGIC;

areset : IN STD_LOGIC;

c0 : OUT STD_LOGIC;

locked : OUT STD_LOGIC

);

END COMPONENT;

SIGNAL s_clk : STD_LOGIC;

SIGNAL deserial_data : STD_LOGIC_VECTOR(n-1 DOWNTO 0);

--Keep

--attribute keep: boolean;

--attribute keep of deserial_data: signal is true;

BEGIN

doutD <= deserial_data;

deserial_inst : fast_deserializer

GENERIC MAP(bits => bits,

n => n

)

PORT MAP(clk => s_clk,

din => din,

count_out => count_outD,

dout => deserial_data);

serial_inst : fast_serializer

GENERIC MAP(bits => bits,

n => n

)

PORT MAP(clk => s_clk,

din => deserial_data,

dout => doutS,

count_out => count_outS);

pll0_inst : altpll0

PORT MAP(inclk0 => inclk0,

areset => areset,

c0 => s_clk,

locked => locked);

END architecture;

|

Testbench

| Código |

|---|

-- Testbench created online at:

-- www.doulos.com/knowhow/perl/testbench_creation/

-- Copyright Doulos Ltd

-- SD, 03 November 2002

library IEEE;

use IEEE.Std_logic_1164.all;

use IEEE.Numeric_Std.all;

entity deserial_tb is

GENERIC (bits : INTEGER := 3;

n : INTEGER := 8

);

end entity;

architecture bench of deserial_tb is

component deserial

GENERIC (bits : INTEGER := 2;

n : INTEGER := 4

);

PORT

(

din : IN STD_LOGIC;

inclk0 : IN STD_LOGIC;

areset : IN STD_LOGIC;

locked : OUT STD_LOGIC;

doutD : OUT STD_LOGIC_VECTOR(n-1 DOWNTO 0);

doutS : OUT STD_LOGIC;

count_outD : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0);

count_outS : OUT STD_LOGIC_VECTOR(bits-1 DOWNTO 0)

);

end component;

signal inclk0: std_logic := '0';

signal areset : std_logic := '0';

signal din: std_logic := '0';

signal count_outD: std_logic_vector(bits-1 downto 0);

signal count_outS: std_logic_vector(bits-1 downto 0);

signal doutD : std_logic_vector(n-1 downto 0);

signal doutS : std_logic;

constant clock_half_period: time := 10 ns;

constant din_rate: time := clock_half_period*2*bits;

signal stop_the_clock: boolean;

begin

-- Insert values for generic parameters !!

uut: deserial

generic map (bits => 3, n => 8 )

port map ( inclk0 => inclk0,

areset => areset,

din => din,

count_outD => count_outD,

count_outS => count_outS,

doutD => doutD,

doutS => doutS);

-- Geraç~ao do estimulo clk

inclk0 <= not inclk0 after clock_half_period;

stimulus: process

begin

wait for 25 ns;

-- Geraç~ao do din

din <= '1';

-- duraç~ao do din = 4 periodos de clk

wait for din_rate;

din <= '0';

wait for din_rate;

din <= '1';

wait for din_rate;

din <= '0';

wait for din_rate;

end process;

end;

|

- Chip Planner:

Simulações

| Nº Bits | ALMs | Potência (mW) | Report Path | Report Timing | Caminho crítico | Logic Block | Optimization | Seed |

|---|---|---|---|---|---|---|---|---|

| 4 | 4.021 | 4.253 | deserial0-dout[0]-internal[3] | S | Balanced | 1 | ||

| 32 | 18.954 | 19.186 | deserial1-dout[0]-internal[31] | S | Balanced | 1 | ||

| 128 | 64.238 | 64.791 (VIOLATED) | deserial0-dout[0]-internal[127] | Auto | Balanced | 1 |