MI1022806 2020 2 AULA08

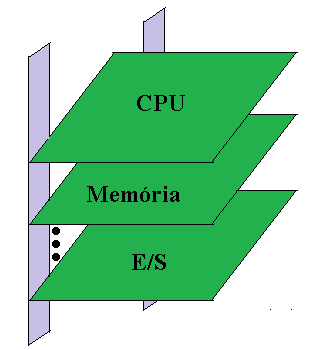

1 CPU - Unidade Central de Processamento

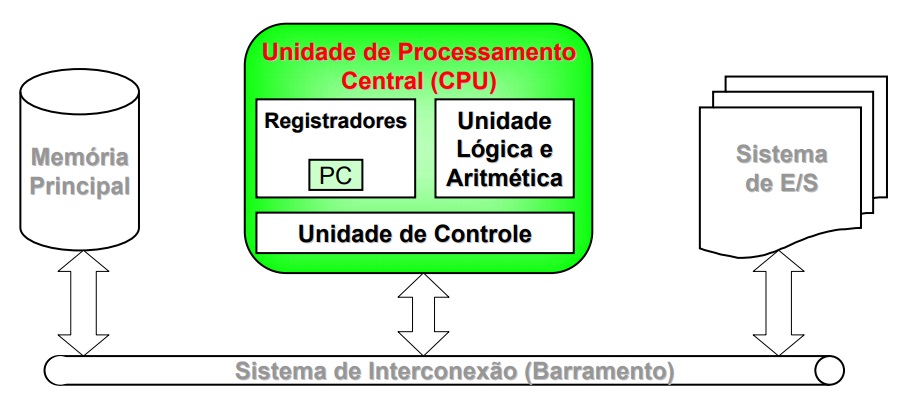

- A CPU é o "cérebro" do processador. E possui as funções de

- - Interpretação e execução dos programas da memória principal;

- - Controle dos demais componentes.

Figura 1 - Unidade Central de Processamento.

- Componentes

- - Registradores - armazenam temporariamente dados e instruções.

- - Unidade Lógica e Aritmética (ULA)- “processa” os dados e atualiza os registradores.

- - Unidade de Controle (UC) - “dispara” cada um das etapas de execução da instrução.

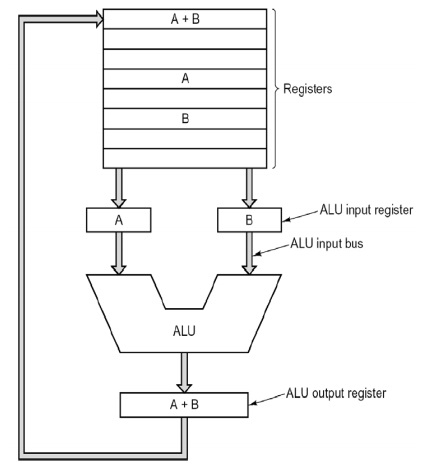

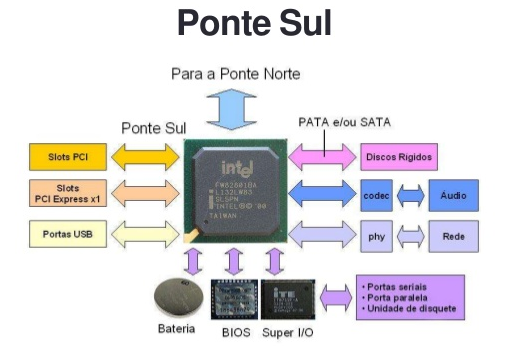

1.1 ULA

É o “núcleo” da CPU.

- Executa as operações de processamento de dados. Podem ser diferentes para cálculos com inteiros e ponto flutuante.

- Ativa bits especiais (flags), como resultado da operação. Ex: operação nula (bit Z), operação negativa (bit N), overflow, etc.

- Está conectada a um grupo de registradores pelo barramento interno, formando o caminho de dados.

- Pode-se utilizar um conjunto de ULAs para a execução paralela de instruções.

Figura 2 - Diagrama de funcionamento da Unidade Aritmética e Lógica - ULA.

1.2 Registradores

Um banco de registradores são pequenas unidades de memória com alta velocidade.

- Mais rápidas que as memórias principal e cache.

- Utilizam o barramento interno da CPU.

Armazenamento temporário de dados, instruções e endereços, em utilização pelo processador.

- Possuem diferentes funções, mas têm um uso bem definido, dentro da arquitetura.

- Possibilitam operações de leitura e escrita.

1.2.1 Registradores de uso geral

- Utilizados para armazenar dados que serão processados ou produzidos pela ULA. Ex: AX-DX, AC, R0-R13.

- Coletivamente são chamados conjunto de registradores de dados (data register file).

1.2.2 Registradores de controle

- Utilizados no controle das operações pela CPU e nas trocas de informações com a MP. Ex: PC, IR, MAR, MBR.

- Alguns desses são invisíveis aos programadores.

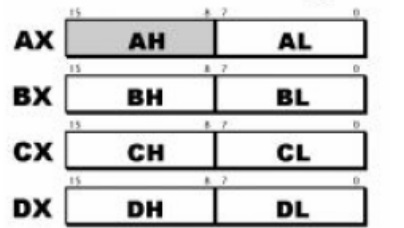

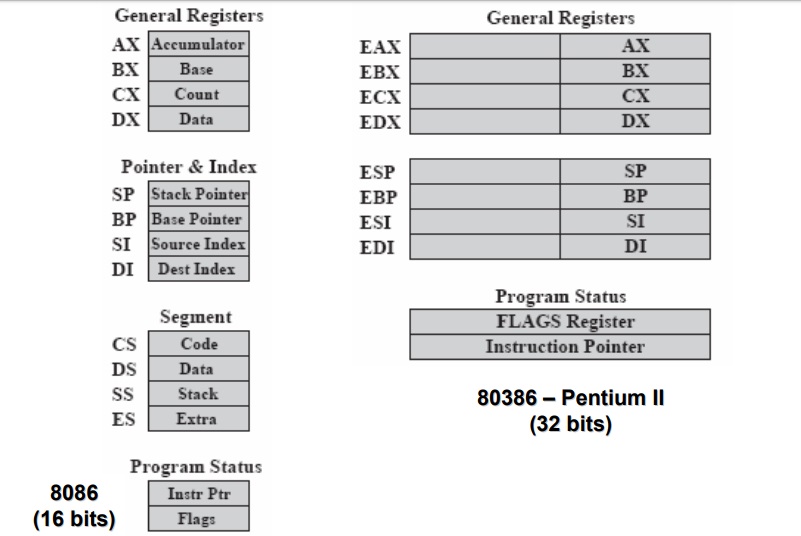

1.2.3 Registradores (Processador 8088/8086)

- CPU possui 14 registradores de 16 bits visíveis.

- 4 registradores de uso geral:

- AX (Acumulador): armazena operandos e resultados dos cálculos aritméticos e lógicos.

- BX (Base): armazena endereços indiretos.

- CX (Contador): conta iterações de loops ou especifica o n° de caracteres de uma string.

- DX (Dados): armazena overflow e endereço de E/S.

- Podem ser usados como registradores de 8 bits: Ex: AH e AL (byte alto e byte baixo de AX).

Figura 3 - Bloco de registradores dos processadores 8088/8086.

- 4 registradores de segmento:

- CS (Segmento de Código): contém o endereço da área com as instruções de máquina em execução.

- DS (Segmento de Dados): contém o endereço da área com os dados do programa. Geralmente aponta para as variáveis globais do programa.

- SS (Segmento de Pilha): contém o endereço da área com a pilha. Que armazena informações importantes sobre o estado da máquina, variáveis locais, endereços de retorno e parâmetros de subrotinas.

- ES (Segmento Extra): utilizado para ganhar acesso a alguma área da memória quando não é possível usar os outros registradores de segmento. Ex: transferências de bloco de dados.

- 5 registradores de offset:

- PC (Program Counter) ou IP (Instruction Pointer): usado em conjunto com o CS para apontar a próxima instrução.

- SI (source index) e DI (destiny index): utilizados para mover blocos de bytes de um lugar (SI) para outro (DI) e como ponteiros para endereçamento (junto com os registradores CS, DS, SS e ES).

- BP (Base Pointer): usado em conjunto com o SS para apontar a base da pilha. Similar ao registrador BX. Usado para acessar parâmetros e variáveis locais.

- SP (Stack Pointer): usado em conjunto com o SS para apontar o topo da pilha.

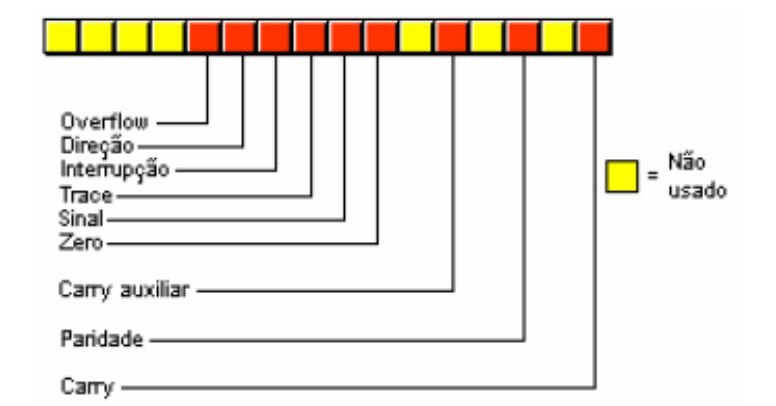

- 1 registrador de estado do processador (PSW) :

- Registrador especial composto por sinalizadores (flags) que ajudam a determinar o estado atual do processador. Coleção de valores de 1 bit. Apenas 9 bits são utilizados:

- 4 mais utilizados: ZF - zero; CF - carry ("vai um“) ou borrow (“vem um”); SF - sinal; e OF - overflow ou underflow.

Figura 4 - Bits do Registrador de estado do Processador (PSW).

Figura 5 - Organização dos Registradores – Família Intel.

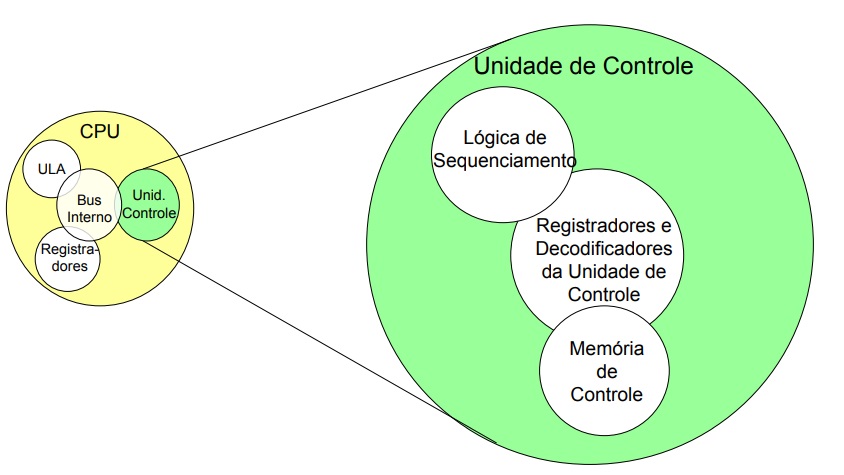

1.3 Unidade de Controle

- Gerencia os recursos disponíveis e o fluxo de dados entre os componentes.

- Controla a execução das instruções pela CPU:

- Busca as instruções na memória principal.

- Decodificação das instruções (geração dos sinais de controle correspondentes).

- Sequenciamento das operações.

- Disparo da execução (envio dos sinais de controle).

- Representa uma das partes mais difíceis de ser projetada em um computador, devido à complexidade dos processadores.

Figura 6 - Estrutura da Unidade de Controle.

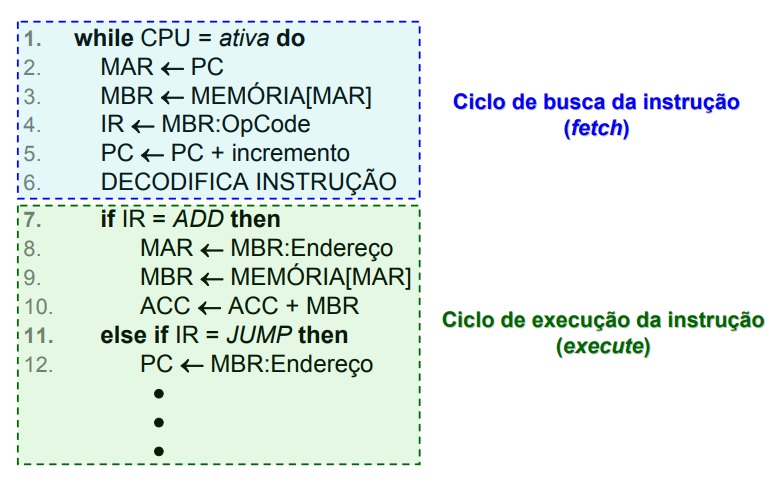

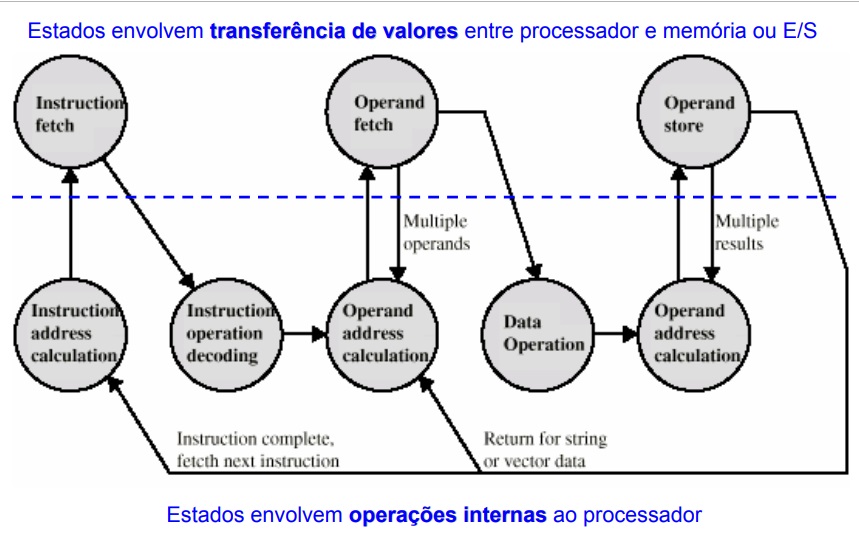

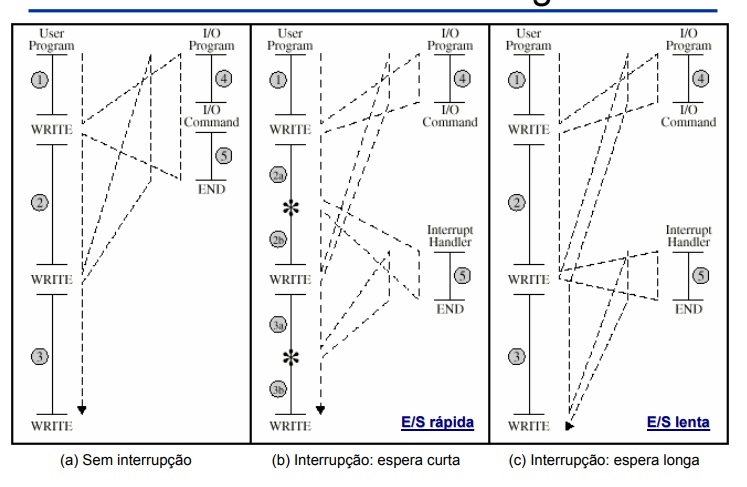

1.4 Ciclo de Busca-Execução (fetch-execute)

- Busca a instrução (memória → IR);

- Altera PC para indicar a próxima instrução;

- Decodifica a instrução atual;

- Determina o endereço e busca o operando na memória (quando necessário);

- Executa a operação (sinais de controle);

- Armazena os resultados;

- Repete passos anteriores.

Figura 7 - Ciclo de Busca-Execução (fetch-execute).

Figura 8 - Transferência de dados entre processador e Memória ou E/S.

1.5 Categorias de Instruções

- Movimentação processador – memória: Transferência de dados entre CPU e memória principal.

- Movimentação processador - E/S: Transferência de dados entre CPU e módulos de E/S.

- Processamento de dados: Realiza alguma operação lógica ou aritmética nos dados.

- Operações de controle: Alteração na sequência de execução de instruções. Ex: desvios condicionais e não-condicionais (jump)

- Qualquer combinação das operações acima

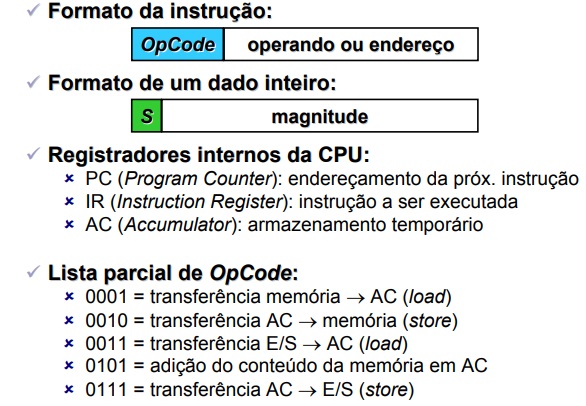

1.6 Máquina Hipotética (32 bits)

Figura 9 - Máquina Hipotética de 32 bits.

Figura 10 - Exemplo do ciclo de busca e execução das instruções.

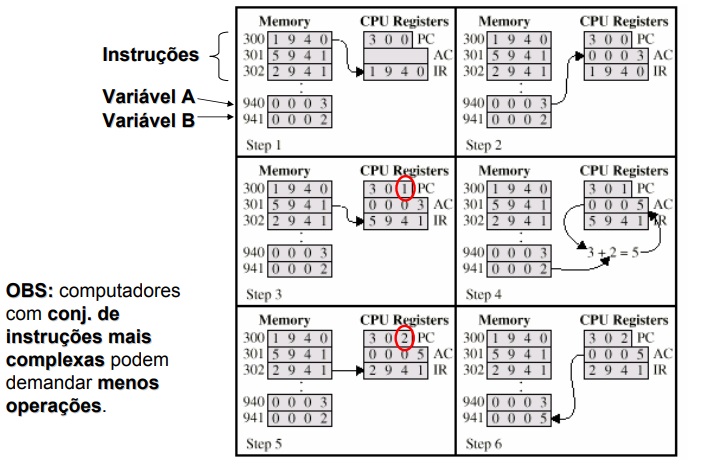

1.7 Interrupções

Mecanismos pelos quais outros componentes podem interromper a sequência normal do processamento.

- Visa melhorar a eficiência do processamento.

- Fontes de interrupções mais comuns:

- Programa (Software): gerada por alguma condição que ocorra como resultado da execução de uma instrução. Ex: overflow, divisão por zero, instrução ilegal etc.

- Timer: gerada pelo processamento interno do relógio (timer). Usado em sistemas sistemas multitarefa preemptivos para executar certas funções a intervalos regulares de tempo.

- E/S: gerada pelo módulo de E/S para sinalizar a conclusão uma operação ou a ocorrência de uma situação de erro.

- Falha de Hardware: gerada na ocorrência de uma falha. Ex: queda de energia, erro de paridade de memória

1.7.1 Controle do fluxo do programa

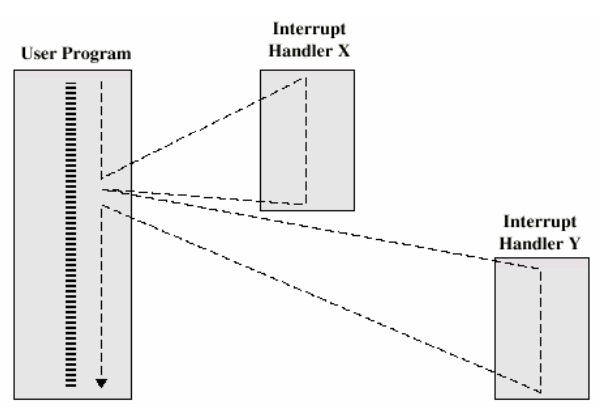

Figura 11 - Controle do fluxo do programa.

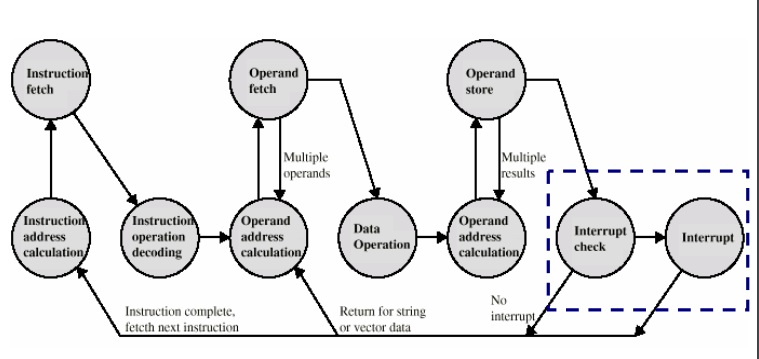

Ciclo de interrupção:

- Acrescentado ao ciclo de instrução.

- Processador verifica se há interrupção: Indicado por um sinal de interrupção.

- Se não há interrupção, busca a próxima instrução na memória.

- Se houver interrupção pendente:

- Suspende a execução do programa corrente.

- Salva o contexto na pilha.

- Configura PC com o endereço de início da rotina de rotina de tratamento da interrupção (interrupt handler routine).

- Processa a interrupção.

- Restaura o contexto.

- Continua a execução do programa interrompido.

Figura 12 - Ciclo de Instruções com interrupção.

1.8 Múltiplas interrupções

Desabilitar interrupções:

- O processador ignora futuras interrupções enquanto processa uma interrupção.

- Interrupção são manipuladas na sequência em que elas acontecem.

Definir prioridades:

- Interrupções de baixa prioridade são interrompidas por interrupções de alta prioridade;

- Quando a interrupção de mais alta prioridade foi processada, o processador retorna à interrupção anterior.

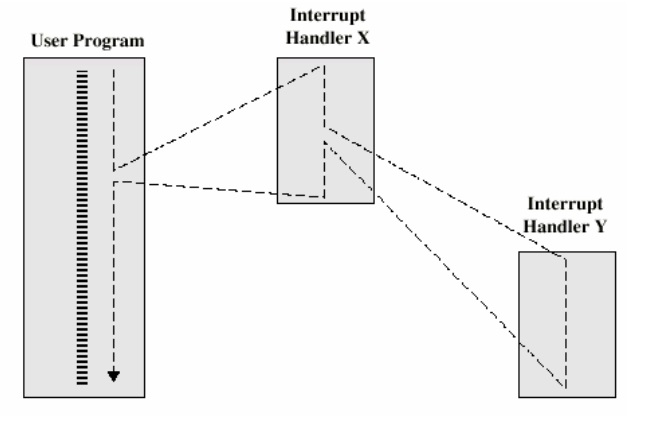

Figura 13 - Múltiplas interrupções com execução sequencial.

Figura 14 - Múltiplas interrupções com execução aninhada.

1.9 Sinal de clock

- Utilizado para atender as relações de tempo requeridas nas operações (sincronismo).

- Novas operações básicas são iniciadas em um novo ciclo de clock.

- A execução de uma instrução consome um certo nº de ciclos de clock.

- Varia de acordo com o nº de operações básicas requeridas e o tempo de execução de cada uma delas.

- O tamanho do ciclo de clock é um dos fatores que determinam o desempenho de um processador.

< tamanho do ciclo ⇒ < tempo de execução ⇒ > nº de instruções/seg.

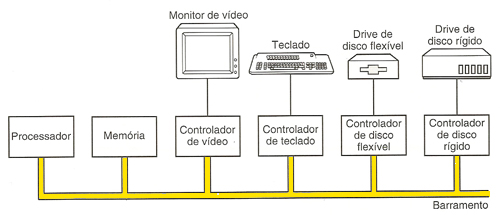

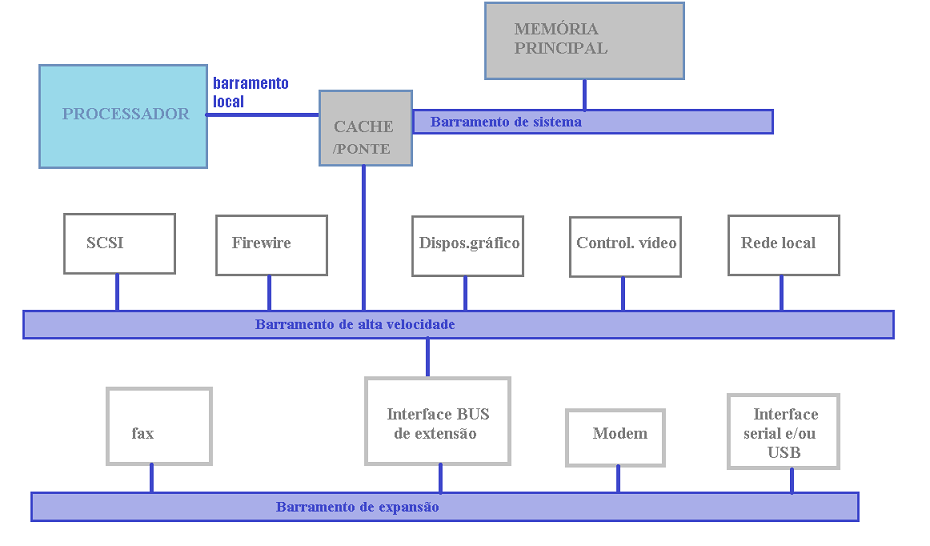

2 Barramentos do Computador

Barramento é um caminho de comunicação entre dois ou mais dispositivos; é um conjunto de linhas de comunicação (condutor elétrico ou fibra ótica) que permitem a interligação entre dispositivos de um sistema de computação (CPU; Memória Principal; HD e outros periféricos), ou entre vários sistemas de computação.

O conjunto de barramentos (bus, em inglês) é a forma de interconexão dos módulos e dispositivos do computador que permite troca de sinais de controle e dados.

O mecanismo mais comum de interconexão usa um barramento do sistema compartilhado com múltiplas linhas. Os sistemas mais modernos usam uma hierarquia de barramentos para obter melhor desempenho.

Normalmente, quando se fala em barramento, está se referindo ao barramento de sistema, que é fundamental, em termos de desempenho do sistema ou ao barramento de E/S, que é acessível ao usuário:

Figura 15 - Exemplo de Barramento de um Computador.

Os demais barramentos são internos ao processador, ou à placa mãe.

Os principais aspectos de um projeto de sistema de barramento são:

- arbitragem - decisão sobre permissões para envio de sinais por meio das linhas do barramento; pode ser centralizada ou distribuída

- temporização - envio de sinais sincronizado por um relógio central, ou assíncrono, com base na transmissão mais recente

- largura do barramento - quantidade de bits que podem ser transmitidos ao mesmo tempo; número de linhas de endereço e dados - 8 bits, 16 bits, 32 bits, 64 bits, etc

- velocidade de transmissão de dados - como cada linha pode conduzir apenas 1 bit por vez, o número de linhas determina quantos bits podem ser transferidos por vez. A velocidade é medida em bps (bits por segundo) - 10 bps, 160 kbps, 100 Mbps, 1 Gbps etc.

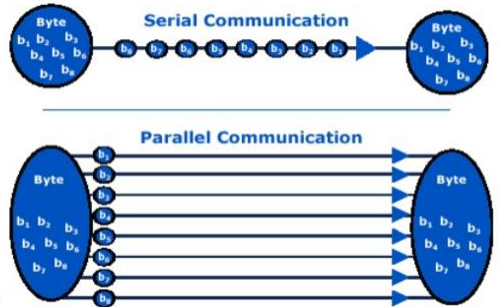

2.1 Classificação

- Barramento Serial

- O barramento possui um único fio, por onde passa um sinal de cada vez, ou seja, um bit de cada vez. Exemplo: USB, PCI Express, Hyper-Transport, Firewire.

- Barramento Paralelo

- O barramento possui vários fios por onde passam vários sinais simultaneamente, sendo um sinal para cada fio. Exemplo: UNIBUS, MCA, ISA, EISA, PCI, AGP.

Figura 16 - Comunicação Serial vs. comunicação Paralela.

2.2 Estrutura de barramento

- De 50 a centenas de linhas

- Cada linha com uma função em particular

- DADOS – 32,64, 128 ou mais linhas. Largura determina em geral o desempenho do sistema

- ENDEREÇOS - 8, 16 ou 32 - Endereça memória, E/S, (designa a origem ou destino dos dados). Largura determina a capacidade de memória máxima do sistema

- CONTROLE:

- Transmitem informações de comando e sincronização

- Sincronização – validade das informações de dados e endereços

- Comando – especificam operações a serem realizadas

- Pode haver linha de distribuição de potência

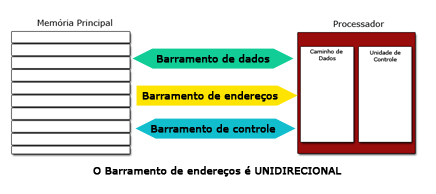

2.2.1 Linhas de Dados

Fornecem um caminho para a transferência de dados entre os módulos do sistema.

O barramento de dados contém, tipicamente, 32, 64 ou 128 linhas (largura do barramento).

Se o barramento de dados tem largura de 8 bits e cada instrução tem tamanho de 16 bits, o processador terá que acessar duas vezes o módulo de memória em cada ciclo de instrução.

Normalmente o barramento de dados é bidirecional.

2.2.2 Linhas de Endereço

São utilizadas para designar a fonte, ou o destino, dos dados transferidos.

Por exemplo, quando o processador deseja ler uma palavra da memória, ele coloca o endereço da mesma nas linhas de endereço.

A largura do barramento determina a capacidade máxima da memória do sistema.

Em geral, as linhas de endereço também são empregadas para endereçar as portas de E/S. Tipicamente, os bits mais significativos (parte alta do endereço) são utilizados para identificar um módulo particular do sistema (p.e., em um pente de memória), enquanto os bits menos significativos identificam uma posição particular na memória, ou porta de E/S deste módulo.

Tipicamente as linhas de endereço são unidirecionais.

2.2.3 Linhas de Controle

São usadas para controlar o acesso e a utilização das linhas de dados e de endereço.

Como as linhas de dados e endereço são compartilhadas por todos os componentes, deve existir uma maneira de controlar sua utilização.

Os sinais de controle são utilizados tanto para transmitir comandos, quanto para transmitir informações de temporização entre os módulos do sistema.

Os sinais de temporização indicam a validade das informações de dados e de endereço e os sinais de comando especificam as operações a serem executadas.

Linhas de controle típicas incluem comandos para:

- Escrita na memória

- Leitura de memória

- Escrita em porta de E/S

- Leitura em porta de E/S

- Confirmação de transferência de dados

- Requisição do barramento

- Concessão do barramento

- Requisição de interrupção

- Confirmação de interrupção

- Relógio

- Inicialização

Quando um dispositivo ou módulo do sistema deseja enviar ou requisitar dados para outro, ele deve:

- obter o controle do barramento

- publicar o endereço destino/fonte do dado no barramento de endereços

- transferir/ler os dados por meio do barramento de dados

- confirmar a transferência

- liberar o barramento

2.3 Características principais

Fisicamente, o barramento de sistema é, na verdade, um conjunto de condutores elétricos paralelos. São linhas de metal impressas em um cartão ou placa.

O barramento se estende por todos os componentes do sistema, cada um dos quais se liga a algumas, ou a todas as linhas do barramento.

Figura 17 - Arranjo físico típico das linhas de barramentos.

Existem vários tipos de barramentos em um sistema computacional típico:

Figura 18 - Barramentos de um sistema computacional típico.

Um barramento também pode ser dedicado ou multiplexado.

Uma linha de barramento dedicada tem função fixa ou é associada a um subconjunto específico de componentes físicos do computador.

Exemplo: barramento que interliga placa-mãe ao HD (IDE ou Sata)

Figura 19 - Slot do barramento SATA que liga a placa-mãe ao HD.

Figura 20 - Cabo com conector SATA.

2.4 Arbitragem, ou arbitração

Na maioria dos sistemas, mais de um módulo pode precisar ter o controle do barramento, ao mesmo tempo.

A arbitragem de barramento é utilizada para decidir qual módulo terá prioridade no uso do barramento.

Os vários métodos podem ser classificados como centralizados, ou distribuídos.

Em um esquema centralizado, um único dispositivo de hardware conhecido como controlador, ou árbitro de barramento é responsável por alocar tempo de utilização do barramento a cada módulo do sistema.

Um processo típico de arbitragem, em um barramento do tipo PCI, seria:

- Em algum ponto anterior ao início do ciclo de relógio 1, o dispositivo A ativa seu sinal REQ (requisição de uso do bus). O árbitro verifica esse sinal no início do ciclo 1 do clock.

- Durante o ciclo 1, o dispositivo B requisita também o uso do barramento, ativando seu sinal REQ.

- Ao mesmo tempo, o árbitro ativa o sinal GNT (indica ao dispositivo que o árbitro permitiu o acesso) do dispositivo A, cedendo a esse dispositivo o controle do bus

- O dispositivo A verifica o sinal GNT-A na sua linha, tomando conhecimento no início do ciclo 2 de relógio que obteve o controle do bus. Verifica também que não existe sinal nas linhas IRDY (Iniciador pronto) e TRDY (Alvo pronto), o que significa que o barramento está ocioso.

- O dispositivo A ativa seu sinal FRAME (indica início e duração de uma transação) e coloca a informação de endereço no bus de endereços e o comando C/BE no barramento. Além disto, mantém seu sinal REQ, uma vez que terá uma segunda transação a realizar em seguida.

- O árbitro testa todas as linhas GNT, no início do ciclo 3 de relógio e decide ceder o controle do barramento para o dispositivo B, na próxima transação, isto é, quando o barramento estiver ocioso. Então, ativa o sinal GNT do dispositivo B e desativa o sinal GNT do dispositivo A.

- O dispositivo A desativa seu sinal FRAME, indicando que a sua única transação autorizada está em andamento. Coloca os dados no barramento de dados e envia o sinal IRDY para o alvo. O alvo lê os dados no início do ciclo de relógio 5.

- O dispositivo B utiliza o barramento, no início do ciclo 5. Verifica os sinais IRDY e FRAME desativados e portanto, pode ativar o seu sinal FRAME. Além disto, desativa seu sinal REQ, uma vez que deseja efetuar apenas uma transação.

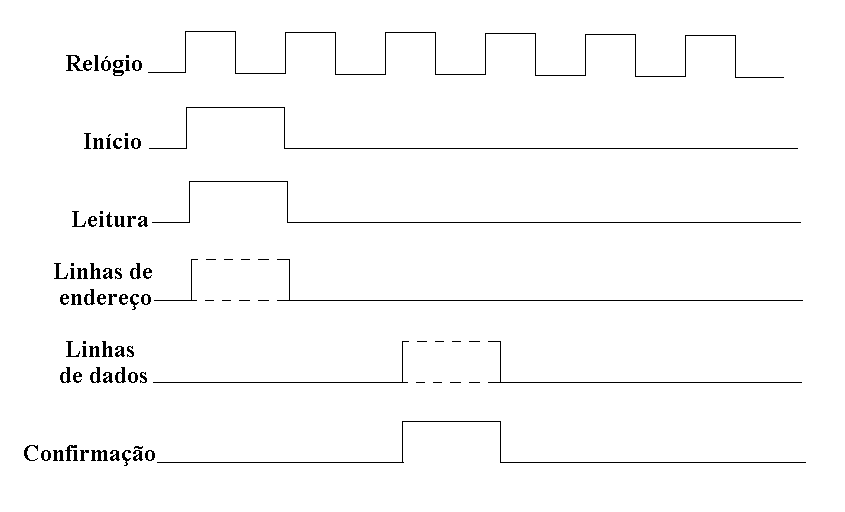

2.5 Temporização

Refere-se ao modo pelo qual os eventos nesse barramento são coordenados.

Em um esquema de transmissão síncrona, a ocorrência de eventos é determinada por um relógio. O barramento inclui uma linha de clock, por meio da qual um sinal de onda quadrada é transmitido.

Todos os eventos no barramento síncrono devem começar no início de um ciclo de relógio.

A figura abaixo ilustra uma requisição de leitura em barramento síncrono:

Figura 21 - Requisição de leitura em barramento síncrono.

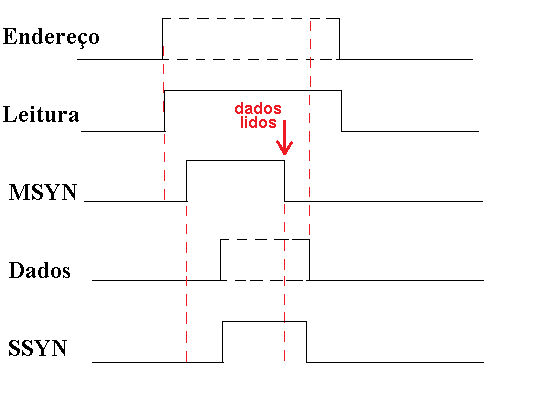

Em um esquema de transmissão assíncrona, a ocorrência de um evento depende de outros eventos e sinais, ocorridos e transmitidos anteriormente.

Um exemplo simples é ilustrado abaixo:

Figura 22 - Esquema de transmissão assíncrona.

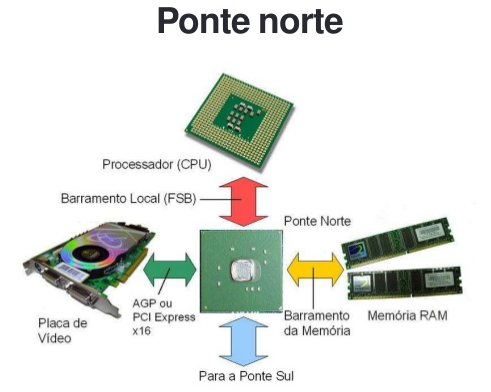

3 Barramento do processador

É utilizado pelo processador internamente, para interligar este e o chipset do PC, e para envio de sinais para outros componentes do sistema computacional.

Figura 23 - Barramento do Processador: Ponte Norte.

Figura 24 - Barramento do Processador: Ponte Sul.

Atualmente, os barramentos dos processadores (os de transferência de dados) têm sido bastante aprimorados com o objetivo de maior velocidade de processamentos de dados.

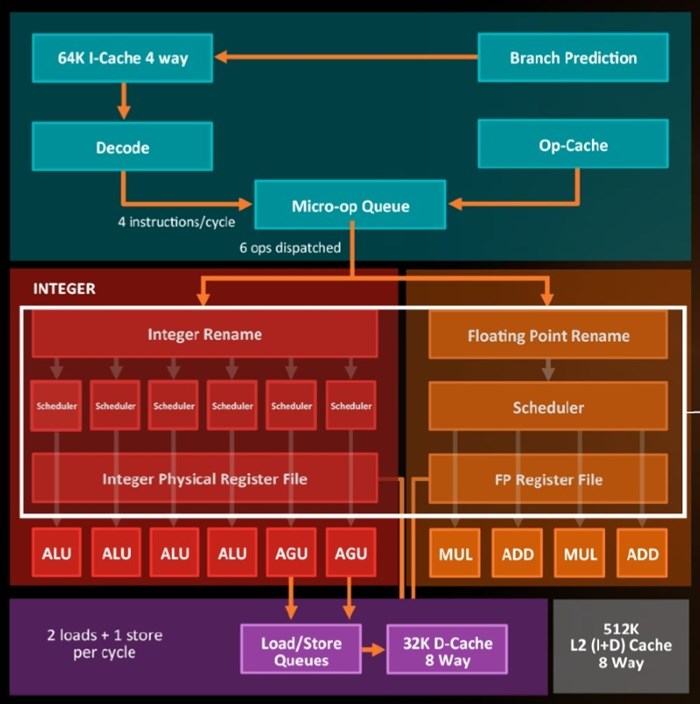

4 Barramento de Cache

O processador tem um barramento local especial, que o interconecta diretamente à memória cache.

Figura 25 - Barramento de Cache.

É o barramento dedicado para acesso à memória cache do computador, memória estática de alto desempenho localizada próximo ao processador.

5 Barramento de Memória

É o barramento responsável pela conexão da memória principal ao processador. É um barramento de alta velocidade que varia de micro para micro e atualmente gira em torno de 512 MHz a 8192 MHz, como nas memórias do tipo DDR3.

Figura 26 - Barramento de Memória.

6 Barramento de Entrada e Saída

É o barramento I/O (ou E/S), responsável pela comunicação das diversas interfaces e periféricos ligados à placa-mãe, possibilitando a instalação de novas placas.

Os mais conhecidos são: PCI, AGP e USB.

Os periféricos não se conectam diretamente ao barramento de sistema devido:

- haver uma larga variedade de periféricos com vários métodos de operação sendo inviável incorporar diversas lógicas de controle dentro do processador...

- A taxa de transferência de dados dos periféricos é normalmente (muito) mais baixa do que a da memória do processador, sendo inviável usar o barramento de alta velocidade para comunicação com periférico.

- Os periféricos usam normalmente formatos de dados e tamanhos de palavras diferentes dos do computador a que estão conectados.

Permitem a conexão de dispositivos como:

- Placa gráfica;

- Rede;

- Placa de Som;

- Mouse;

- Teclado;

- Modem;

- etc.

São exemplos de Barramentos de Entrada e Saída:

- AGP;

- AMR;

- EISA;

- IrDA;

- ISA;

- MCA;

- PCI;

- PCI-e;

- Pipeline; SCSI; VESA; USB, e;

- PS/2.

7 Tipos de barramentos de E/S

A seguir, serão descritos os principais tipos de barramentos de expansão, utilizados nos PCs comerciais.

Note que o termo slot faz referência aos encaixes físicos de cada barramento para a conexão de dispositivos (placas de vídeo, placas de rede, etc).

Em geral, o que diferencia um barramento de outro é o tipo de slot.

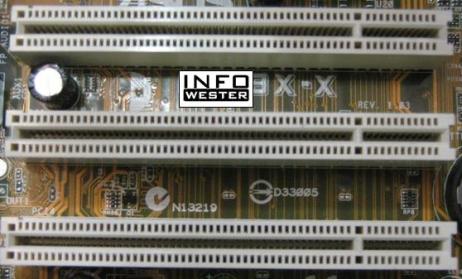

7.1 Barramento ISA (Industry Standard Architecture)

O barramento ISA é um padrão não mais utilizado, sendo encontrado apenas em computadores antigos. Seu aparecimento se deu na época do IBM PC e essa primeira versão trabalha com transferência de 8 bits por vez e clock de 8,33 MHz (na verdade, antes do surgimento do IBM PC-XT, essa valor era de 4,77 MHz).

Na época do surgimento do processador 286, o barramento ISA ganhou uma versão capaz de trabalhar com 16 bits. Dispositivos anteriores que trabalhavam com 8 bits funcionavam normalmente em slots com o padrão de 16 bits, mas o contrário não era possível, isto é, de dispositivos ISA de 16 bits trabalharem com slots de 8 bits, mesmo porque os encaixes ISA de 16 bits tinham uma extensão que os tornavam maiores que os de 8 bits, conforme indica a imagem abaixo:

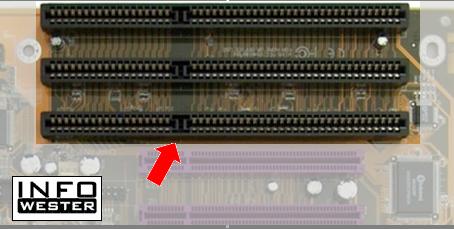

Figura 27 - Placa de som com barramento ISA.

Figura 28 - Slots de barramento ISA em uma placa-mãe.

Repare na imagem acima que o slot contém uma divisão. As placas de 8 bits utilizam somente a parte maior. Como você já deve ter imaginado, as placas de 16 bits usam ambas as partes. Por conta disso, as placas-mãe da época passaram a contar apenas com slots ISA de 16 bits. Curiosamente, alguns modelos foram lançados tendo tanto slots de 8 bits quanto slots de 16 bits.

Se você está acostumado com slots mais recentes, certamente percebeu o quão grandes são os encaixes ISA. O de 16 bits, por exemplo, conta com 98 terminais. Por aí, é possível perceber que as placas de expansão da época (isto é, placas de vídeo, placas de som, placas de modem, etc) eram igualmente grandes. Apesar disso, não era difícil encontrar placas que não utilizavam todos os contatos dos slots ISA, deixando um espaço de sobra no encaixe.

Com a evolução da informática, o padrão ISA foi aos poucos perdendo espaço. A versão de 16 bits é capaz de proporcionar transferência de dados na casa dos 8 MB por segundo, mas dificilmente esse valor é alcançado, ficando em torno de 5 MB. Como essa taxa de transferência era suficiente para determinados dispositivos (placas de modem, por exemplo), por algum tempo foi possível encontrar placas-mãe que contavam tanto com slots ISA quanto com slots PCI (o padrão sucessor).

7.2 Barramento PCI (Peripheral Component Interconnect)

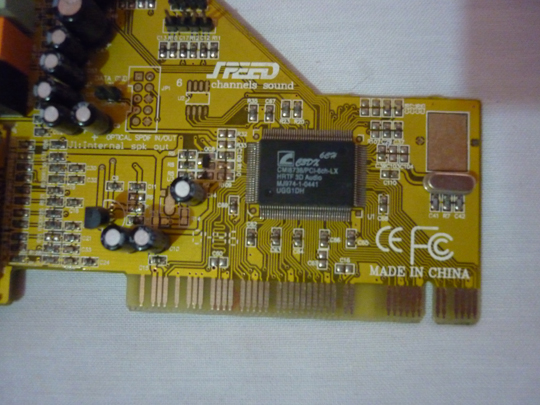

O barramento PCI surgiu no início de 1990 pelas mãos da Intel. Suas principais características são a capacidade de transferir dados a 32 bits e clock de 33 MHz, especificações estas que tornaram o padrão capaz de transmitir dados a uma taxa de até 132 MB por segundo. Os slots PCI são menores que os slots ISA, assim como os seus dispositivos, obviamente.

Mas, há uma outra característica que tornou o padrão PCI atraente: o recurso Bus Mastering. Em poucas palavras, trata-se de um sistema que permite a dispositivos que fazem uso do barramento ler e gravar dados direto na memória RAM, sem que o processador tenha que "parar" e interferir para tornar isso possível. Note que esse recurso não é exclusivo do barramento PCI.

Figura 29 - Placa de som barramento PCI.

Figura 30 - Barramento PCI na placa-mãe de um PC.

Outra característica marcante do PCI é a sua compatibilidade com o recurso Plug and Play (PnP), algo como "plugar e usar". Com essa funcionalidade, o computador é capaz de reconhecer automaticamente os dispositivos que são conectados ao slot PCI. Atualmente, tal capacidade é trivial nos computadores, isto é, basta conectar o dispositivo, ligar o computador e esperar o sistema operacional avisar sobre o reconhecimento de um novo item para que você possa instalar os drivers adequados (isso se o sistema operacional não instalá-lo sozinho). Antigamente, os computadores não trabalhavam dessa maneira e o surgimento do recurso Plug and Play foi uma revolução nesse sentido. Além de ser utilizada em barramentos atuais, essa funcionalidade chegou a ser implementada em padrões mais antigos, inclusive no ISA.

O barramento PCI também passou por evoluções: uma versão que trabalha com 64 bits e 66 MHz foi lançada, tendo também uma extensão em seu slot. Sua taxa máxima de transferência de dados é estimada em 512 MB por segundo. Apesar disso, o padrão PCI de 64 bits nunca chegou a ser popular. Um dos motivos para isso é o fato de essa especificação gerar mais custos para os fabricantes. Além disso, a maioria dos dispositivos da época de auge do PCI não necessitava de taxas de transferência de dados maiores.

7.3 Barramento PCI-X (Peripheral Component Interconnect Extended)

Muita gente confunde o barramento PCI-X com o padrão PCI Express (mostrado mais abaixo), mas ambos são diferentes. O PCI-X nada mais é do que uma evolução do PCI de 64 bits, sendo compatível com as especificações anteriores. A versão PCI-X 1.0 é capaz de operar nas frequências de 100 MHz e 133 MHz. Neste última, o padrão pode atingir a taxa de transferência de dados de 1.064 MB por segundo. O PCI-X 2.0, por sua vez, pode trabalhar também com as frequências de 266 MHz e 533 MHz.

Figura 31 - Detalhe de um barramento PCI-X.

7.4 Barramento AGP (Accelerated Graphics Port)

Se antes os computadores se limitavam a exibir apenas caracteres em telas escuras, hoje eles são capazes de exibir e criar imagens em altíssima qualidade. Mas, isso tem um preço: quanto mais evoluída for uma aplicação gráfica, em geral, mais dados ela consumirá. Para lidar com o volume crescente de dados gerados pelos processadores gráficos, a Intel anunciou em meados de 1996 o padrão AGP, cujo slot serve exclusivamente às placas de vídeo.

A primeira versão do AGP (chamada de AGP 1.0) trabalha a 32 bits e tem clock de 66 MHz, o que equivale a uma taxa de transferência de dados de até 266 MB por segundo, mas na verdade, pode chegar ao valor de 532 MB por segundo. Explica-se: o AGP 1.0 pode funcionar no modo 1x ou 2x. Com 1x, um dado por pulso de clock é transferido. Com 2x, são dois dados por pulso de clock.

Em meados de 1998, a Intel lançou o AGP 2.0, cujos diferenciais estão na possibilidade de trabalhar também com o novo modo de operação 4x (oferecendo uma taxa de transferência de 1.066 MB por segundo) e alimentação elétrica de 1,5 V (o AGP 1.0 funciona com 3,3 V). Algum tempo depois surgiu o AGP 3.0, que conta com a capacidade de trabalhar com alimentação elétrica de 0,8 V e modo de operação de 8x, correspondendo a uma taxa de transferência de 2.133 MB por segundo.

Além da alta taxa de transferência de dados, o padrão AGP também oferece outras vantagens. Uma delas é o fato de sempre poder operar em sua máxima capacidade, já que não há outro dispositivo no barramento que possa, de alguma forma, interferir na comunicação entre a placa de vídeo e o processador (lembre-se que o AGP é compatível apenas com placas de vídeo). O AGP também permite que a placa de vídeo faça uso de parte da memória RAM do computador como um incremento de sua própria memória, um recurso chamado Direct Memory Execute.

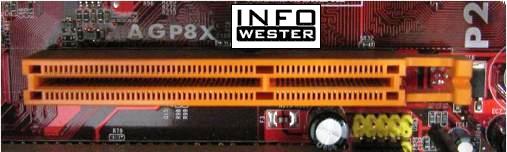

Figura 32 - Detalhe do barramento AGP.

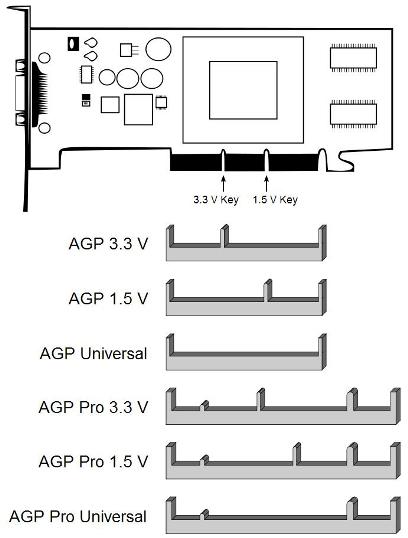

Quanto ao slot, o AGP é ligeiramente menor que um encaixe PCI. No entanto, como há várias versões do AGP, há variações nos slots também (o que é lamentável, pois isso gera muita confusão). Essas diferenças ocorrem principalmente por causa das definições de alimentação elétrica existentes entre os dispositivos que utilizam cada versão. Há, por exemplo, um slot que funciona para o AGP 1.0, outro que funciona para o AGP 2.0, um terceiro que trabalha com todas as versões (slot universal) e assim por diante. A ilustração abaixo mostra todos os tipos de conectores:

Figura 33 - Tipos de conectores do tipo AGP.

Como você deve ter reparado na imagem acima, o mercado também conheceu versões especiais do AGP chamadas AGP Pro, direcionadas a placas de vídeo que consomem grande quantidade de energia.

Apesar de algumas vantagens, o padrão AGP acabou perdendo espaço e foi substituído pelo barramento PCI Express.

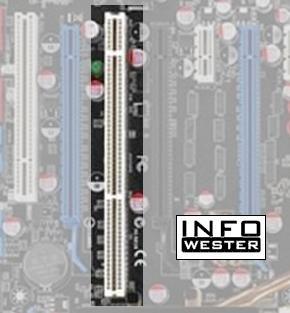

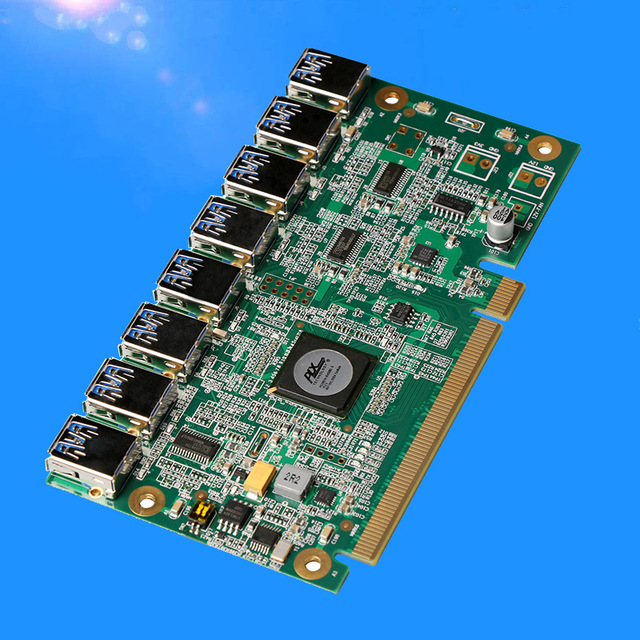

7.5 Barramento PCI Express

O padrão PCI Express (ou PCIe ou, ainda, PCI-EX) foi concebido pela Intel em 2004 e se destaca por substituir, ao mesmo tempo, os barramentos PCI e AGP.

Isso acontece porque o PCI Express está disponível em vários segmentos: 1x, 2x, 4x, 8x e 16x (há também o de 32x, mas até o fechamento deste artigo, este não estava em uso pela indústria).

Quanto maior esse número, maior é a taxa de transferência de dados. Como mostra a imagem abaixo, esse divisão também reflete no tamanho dos slots PCI Express:

Figura 34 - Placa de expansão com conectores tipo USB.

Figura 35 - Detalhe do barramento PCIe ou PCI-EX.

O PCI Express 16x, por exemplo, é capaz de trabalhar com taxa de transferência de cerca de 4 GB por segundo, característica que o faz ser utilizado por placas de vídeo, um dos dispositivos que mais geram dados em um computador.

O PCI Express 1x, mesmo sendo o mais "fraco", é capaz de alcançar uma taxa de transferência de cerca de 250 MB por segundo, um valor suficiente para boa parte dos dispositivos mais simples.

Figura 36 - Placa de expansão de comunicação serial e paralela.

Com o lançamento do PCI Express 2.0, que aconteceu no início de 2007, as taxas de transferência da tecnologia praticamente dobraram.

7.6 Barramentos AMR, CNR e ACR

Os padrões AMR (Audio Modem Riser), CNR (Communications and Network Riser) e ACR (Advanced Communications Riser) são diferentes entre si, mas compartilham da ideia de permitir a conexão à placa-mãe de dispositivos Host Signal Processing (HSP), isto é, dispositivos cujo controle é feito pelo processador do computador.

Para isso, o chipset da placa-mãe precisa ser compatível. Em geral, esses slots são usados por placas que exigem pouco processamento, como placas de som, placas de rede ou placas de modem simples.

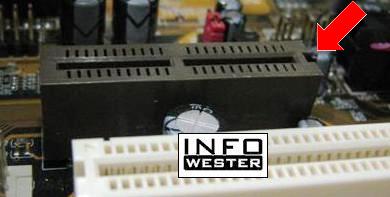

O slot AMR foi desenvolvido para ser usado especialmente para funções de modem e áudio. Seu projeto foi liderado pela Intel. Para ser usado, o chipset da placa-mãe precisava contar com os circuitos AC'97 e MC'97 (áudio e modem, respectivamente). Se comparado aos padrões vistos até agora, o slot AMR é muito pequeno:

Figura 37 - Destaque do slot tipo AMR.

O padrão CNR, por sua vez, surgiu praticamente como um substituto do AMR e também tem a Intel como principal nome no seu desenvolvimento. Ambos são, na verdade, muito parecidos, inclusive nos slots. O principal diferencial do CNR é o suporte a recursos de rede, além dos de áudio e modem.

Em relação ao ACR, trata-se de um padrão cujo desenvolvimento tem como principal nome a AMD. Seu foco principal são as comunicações de rede e USB. Esse tipo foi por algum tempo comum de ser encontrado em placas-mãe da Asus e seu slot é extremamente parecido com um encaixe PCI, com a diferença de ser posicionado de forma contrária na placa-mãe, ou seja, é uma espécie de "PCI invertido".

7.7 Barramento USB

Este tipo de barramento, ao contrário dos demais, faz transmissão SERIAL de dados.

7.8 Outros barramentos

Os barramentos mencionados neste texto foram ou são bastante utilizados pela indústria, mas há vários padrões que, por razões diversas, tiveram aceitação mais limitada no mercado. É o caso, por exemplo, dos barramentos VESA, MCA e EISA:

7.8.1 VESA:

Também chamado de VLB (VESA Local Bus), esse padrão foi estabelecido pela Video Electronics Standards Association (daí a sigla VESA) e funciona, fisicamente, como uma extensão do padrão ISA (há um encaixe adicional após um slot ISA nas placas-mãe compatíveis com o padrão). O VLB pode trabalhar a 32 bits e com a frequência do barramento externo do processador (na época, o padrão era de 33 MHz), fazendo com que sua taxa de transferência de dados pudesse alcançar até 132 MB por segundo. Apesar disso, a tecnologia não durou muito tempo, principalmente com a chegada do barramento PCI;

7.8.2 MCA:

Sigla para Micro Channel Architecture, o MCA foi idealizado pela IBM para ser o substituto do padrão ISA. Essa tecnologia trabalha à taxa de 32 bits e à frequência de 10 MHz, além de ser compatível como recursos como Plug and Play e Bus Mastering. Um dos empecilhos que contribuiu para a não popularização do MCA foi o fato de este ser um barramento proprietário, isto é, pertencente à IBM. Por conta disso, empresas interessadas na tecnologia tinham que pagar royalties para inserí-la em seus produtos, ideia essa que, obviamente, não foi bem recebida;

7.8.3 EISA:

Sigla de Extended Industry Standard Architecture, o EISA é, conforme o nome indica, um barramento compatível com a tecnologia ISA. Por conta disso, pode operar a 32 bits, mas mantém sua frequência em 8,33 MHz (a mesma do ISA). Seu slot é praticamente idêntico ao do padrão ISA, no entanto, é mais alto, já que utiliza duas linhas de contatos: a primeira é destinada aos dispositivos ISA, enquanto que a segunda serve aos dispositivos de 32 bits.

8 Nota

Os barramentos abordados neste material servem, essencialmente, à conexão de dispositivos diretamente na placa-mãe, através de slots específicos. No entanto, há outras tecnologias com finalidades semelhantes, como o SATA, além daquelas que permitem a conexão de um dispositivo sem a necessidade de abertura do computador, como o USB, o FireWire e o Bluetooth (este último, sem fio).