Limitações do HDL coder

Ao usar o HDL coder para gerar códigos VHDL, é importante ler algumas páginas de informações da Mathworks.

- hdlsetup - Configura o modelo simulink para conversão para HDL.

- checkhdl - Verifica se o modelo simulink está usando blocos compatíveis com HDL coder.

- makehdl - Utilizado para gerar o código HDL do DUT.

- makehdltb - Utilizado para gerar o código HDL do tb.

Algumas limitações do HDL coder documentadas em makehdltb.

This test bench is not supported when you generate HDL code for the top-level Simulink model. Your DUT subsystem must meet the following conditions: - Input and output data types of the DUT cannot be larger than 64 bits. - Input and output ports of the DUT cannot use enumerated data types. - Input and output ports cannot be single-precision or double-precision data types. - The DUT cannot have multiple clocks. You must set the Clock inputs code generation option to Single. - Use trigger signal as clock must not be selected. - If the DUT uses vector ports, you must use Scalarize vector ports to flatten the interface.

Para gerar o código VHDL do DUT e também do testbench (tb), pode ser utilizado o [HDL Workflow Advisor (HWA). Antes o sistema DUT e o testbench devem ser simulados no Simulink e mostrar os resultados desejados.

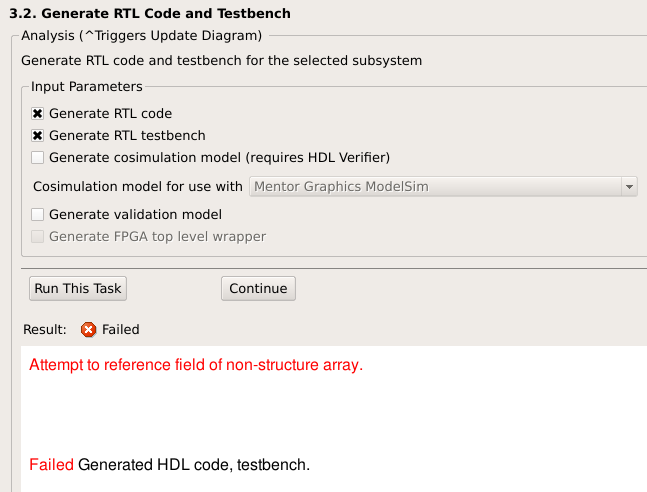

- Relato do problema

No semestre 2020-1, ao utilizar o HDL coder em um sistema com um testbench usando chirp e um time scope e um DUT constituído de um filtro IIR passa faixa de ordem 8, foram detectados os seguintes erros / warnings.

Para contornar o problema foi gerado o tb usando comandos de linha. Neste exemplo o modelo testado tem nome test_model.slx e o DUT é um subsystem com nome DUT. Os comandos também assumem que a pasta corrente é onde está o modelo a ser simulado e convertido.

hdlsetup('test_model')

makehdl('test_model/DUT')

makehdltb('test_model/DUT')

| Warning na geração do HDL do tb usando comandos de linha |

|---|

|

Considerando a entrada e saída do DUT como double a mensagem de warning foi: Warning: Single/Double-precision data type is not supported with the UseFileIOInTestBench option. The generated code will write data to testbench file directly. No entanto, o código VHDL com entradas e saídas do tipo REAL foi gerado com sucesso tanto para o tb como para o DUT, sendo possível realizar a simulação usando o Modelsim. |

- Evitando o problema

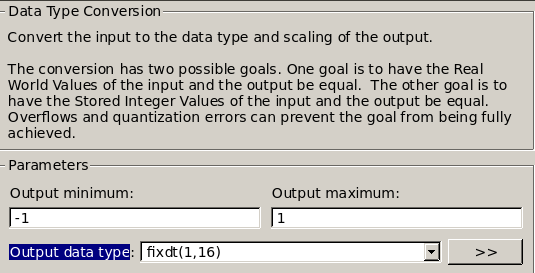

Conforme descrito na documentação da Mathworks, existe uma limitação (Input and output ports cannot be single-precision or double-precision data types) que nem sempre gera o erro relatado. Por isso para evitar-se esse erro é necessário converter o tipo de dado da entrada do DUT para ponto fixo (sfix), usando o bloco Data Type Conversion e definindo o tipo de dado como sfix.

Figura 2 - Configuração do Data Type Conversion

Havendo alguma incompatibilidade no tipo de dado, também é possível deixar o bloco Data Type Conversion com tipo de dado como [Inherit: Inherit via back propagation], modo no qual o Simulink define o tipo de dado da saída desse bloco a partir do tipo de dado que o bloco sucessor exige.