ELD2-EngTelecom (Plano de Ensino)

Ir para navegação

Ir para pesquisar

|

MINISTÉRIO DA EDUCAÇÃO |

- Dados da disciplina

- COMPONENTE CURRICULAR:ELD129003 - ELETRÔNICA DIGITAL II

- CARGA HORÁRIA: 80 horas semestrais (4 horas semanais). Teoria: 50 horas; prática: 30 horas.

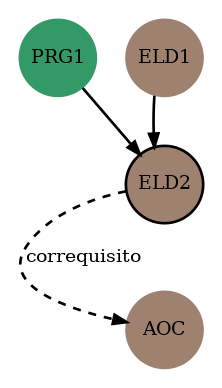

- PRÉ-REQUISITO(S): PRG129001, ELD129002.

- CORREQUISITO(S): nenhum.

- DISCIPLINA(S) SUCESSORA(S): nenhuma.

- EIXO FORMATIVO: Sistemas Computacionais.

- Objetivos

- Conhecer as famílias lógicas e tipos de dispositivos lógicos programáveis;

- Conhecer e utilizar a linguagem de descrição de hardware VHDL para código sequencial;

- Conhecer e utilizar o projeto hierárquico de sistemas digitais em VHDL, desenvolvendo sistemas configuráveis e parametrizáveis;

- Conhecer e projetar máquinas de estado;

- Utilizar ferramentas de simulação para teste do hardware, utilizar testbenches em VHDL;

- Desenvolver e implementar sistemas digitais em dispositivos FPGA utilizando metodologia RTL e síncrona.

- Ementa

- Dispositivos lógicos programáveis. Circuitos sequenciais. Metodologia síncrona. Projeto hierárquico e parametrizado. Máquinas de estados finita. Register Transfer Methodology. Teste de circuitos digitais. Implementação em FPGA. Introdução a Linguagem de Descrição de Hardware.

- Conteúdo programático

- 1. Dispositivos lógicos programáveis: Abstração digital. Famílias lógicas. Interfaces de E/S (8h)

- 2. Circuitos sequenciais (Implementação com HDL): Sinal de clock, reset sincrono e assincrono; Elementos de memória, Flip Flop D e Latches; Registradores, Contadores, Deslocadores (16h)

- 3. Metodologia síncrona: Tipos de sincronismo de circuitos; Circuitos sequenciais síncronos; Projetos síncronos; Boas práticas em projetos sequenciais; Contadores; Registradores. (14h)

- 4. Projeto hierárquico e parametrizado: Uso de declaração e especificação de configuração; Forma de especificação de parâmetros; Particionamento; (10h)

- 5. Máquinas de estados finitos - MEF: Representação; Análise temporal e desempenho; Tipos Moore vs Mealy; Descrição em VHDL; Otimizações. (10h)

- 6. Register Transfer Methodology: Visão geral da metodologia; Máquinas de estados finitos com fluxo de dados (MEFD); Análise temporal, desempenho, e síntese de MEFD. (10h)

- 7. Teste de circuitos digitais: simulação com Modelsim e uso de testbench em VHDL (4h)

- 8. Projeto Final em equipes: Especificação, projeto, simulação, implementação em hardware, documentação, apresentação oral. (8h)

- 9. Linguagem de descrição de hardware - VHDL Uso de ARRAY, TYPE SUBTYPE, Uso de ATTRIBUTE; Código VHDL sequencial: uso de PROCESS, IF, WAIT, LOOP, CASE; Código para projeto hierárquico uso de PACKAGE, COMPONENT, CONFIGURATION, FUNCTION, PROCEDURE, ASSERT, IF GENERATE. (A carga horária desse tópico está distribuída dentro dos tópicos 2 a 8).

- Metodologia

- O conteúdo da unidade curricular será apresentado por meio de aulas expositivas dialogadas, aulas práticas de maneira articulada com aplicações do conhecimento.

- As aulas práticas serão conduzidas nos laboratórios voltados para análise e projeto de Sistemas Digitais, utilizando softwares como Quartus e Modelsim, disponibilizados nos Laboratório de Sistemas Digitais, Laboratório de Programação e Laboratório de Redes de Computadores.

- Para a fixação do conteúdo, serão desenvolvidos exercícios e trabalhos individuais e em grupo.

- A avaliação da unidade curricular será realizada através de avaliações escritas individuais, projetos de sistemas, experimentos de laboratório, atividades extraclasse. Os critérios de aprovação serão definidos no plano de ensino da unidade curricular.

- Critérios e instrumentos de avaliação

- O resultado final (RF) do aluno na disciplina será calculado realizando a média ponderadas dos valores.

- ,

- onde os pesos de ponderação são:

- cada avaliação e também o resultado final (RF) será atribuído um valor entre 0 e 10.

- valores não inteiros obtidos na média do RF serão arredondados:

- a) para baixo se a parte fracionária for menor que 0,4.

- b) para cima se a parte fracionária for maior que 0,6.

- c) de acordo com a avaliação subjetiva e frequência do aluno se a parte fracionária estiver entre 0,4 e 0,6.

- O aluno deve ter os conceitos superiores ou iguais a 4 nas avaliações A1 a A3 e no PF.

- O resultado final (RF) mínimo para aprovação é 6 (seis).

- Ao aluno que tiver frequência inferior a 75% na disciplina será atribuído RF = 0;

- As avaliações de A1 a AN podem ter parte escrita e parte de laboratório.

- Para estas avaliações haverá no final do semestre a possibilidade de realizar uma recuperação REC cobrindo todas as unidades, para os aluno que estiverem com valores inferiores a 6 nas avaliações A1 a AN, cujo conceito máximo nessas avaliações após a recuperação será de 6.

- A nota AE será cálculada pela média ponderada do conjunto de atividades Atividades Extraclasse AE1 a AEN realizada ao longo do semestre. Para cada uma dessas atividades o aluno/equipe que não entregá-la no prazo preestabelecido, como forma de recuperação será admitido a entrega da atividade com atraso, sendo descontado 0,2 pontos por dia de atraso. Após 50 dias de atraso não será atribuído nenhum conceito a esta atividade;

- A nota PF será constituída pela avaliação no projeto final, no qual serão analisados os quesitos:

- 1 - Implementação do projeto, atendimento as especificações e requisitos do sistema. (PFp)

- 2 - Relatório de documentação do projeto e especificações iniciais. (PFr)

- 3 - Avaliação do aluno durante o desenvolvimento do projeto (ou em defesa individual). (PFi)

- 4 - Apresentação do projeto para a turma (15 minutos por equipe) (PFa)

- Canais e horários de atendimento

- Para a comunicação entre professor-estudante, além dos avisos no SIGAA, utilizaremos o espaço da turma no Chat Institucional. Para acessar é necessário utilizar o email institucional <login@aluno.ifsc.edu.br>.

- Os horários de atendimento aos discentes estão publicados na Agenda pública do prof. Marcos Moecke.

1 Bibliografia

- Bibliografia Básica

- PEDRONI, V. A. Eletrônica digital moderna e VHDL. Rio de Janeiro: Elsevier, 2010.

- BIGNELL, J. W.; DONOVAN, R. Eletrônica digital. Tradução da 5ª edição norte-americana. São Paulo: Cengage Learning, c2010.

- TOCCI, R. J.; WIDMER, N. S.; MOSS, G. L. Sistemas digitais: princípios e aplicações. 10. ed. São Paulo: Pearson Prentice Hall, 2007.

- Bibliografia Complementar

- PEDRONI, V. A. Circuit design and simulation with VHDL. 2nd. ed. New Delhi: PHI Learning Private, 2015.

- TOKHEIM, R. L. Fundamentos de eletrônica digital: volume 2: sistemas sequenciais. 7. ed. Porto Alegre: AMGH, 2013.

- HARRIS, D. M.; HARRIS, S. L. Digital design and computer architecture. Amsterdam: Morgan Kaufmann, 2007. [Tradução em português] Disponível em: https://www.embarcados.com.br/e-book-gratis-projeto-digital-e-arquitetura-de-computadores. Acesso em 10 mai 2022.

- PEDRONI, V. A. Finite state machines in hardware: theory and design (with VHDL and SystemVerilog). London: The MIT press, c2013.

- ASHENDEN, P. J. The designer's guide to VHDL. 3rd ed. Amsterdam; Boston: Morgan Kaufmann Publishers, c2008.