DIG222802 2016 2 AULA01

1 Apresentação

Na unidade curricular Eletrônica Digital I, você aprendeu sobre como funciona um circuito combinacional, constituído por um conjunto de portas lógicas, as quais determinam os valores das saídas diretamente a partir dos valores atuais das entradas, ao contrário dos circuitos sequencias que veremos de agora em diante, não há alterações dos estados do circuito em função do tempo. Portanto em Eletrônica Digital II vamos identificar e resolver problemas que envolvam a variável tempo, cuja solução seja expressa pela lógica binária e implementada através de circuitos eletrônicos digitais sequencias, sejam eles Flip-Flops, Contadores, Registradores e Memórias. Ao final, vamos dar uma olhada em nas linguagens de descrição de hardware e também FPGA.

Sejam muito bem vindos!

Bons Estudos!!

Prof. Douglas A.

2 Circuitos Sequencias

Os circuitos lógicos dos sistemas digitais podem ser classificados em dois tipos: circuitos combinacionais ou circuitos sequenciais. Um circuito combinacional é constituído de um conjunto de portas lógicas, as quais determinam os valores das saídas diretamente a partir dos valores atuais das entradas.

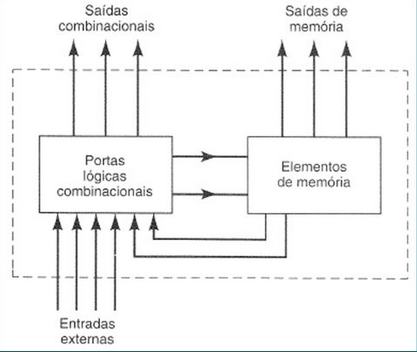

Um circuito sequencial é composto por um circuito combinacional e elementos de memória. As entradas e as saídas do circuito sequencial estão conectadas somente ao circuito combinacional. Os elementos de memória são circuitos capazes de armazenar informação codificada em binário. Algumas das saídas do circuito combinacional são entradas para os elementos de memória, recebendo o nome de variáveis do próximo estado. Já as saídas dos elementos de memória constituem parte das entradas para o circuito combinacional e recebem o nome de variáveis do estado atual. As conexões entre o circuito combinacional e os elementos de memória configuram o que se costuma chamar laço de realimentação, pois a saída de um bloco é entrada para o outro e vice-versa. A Figura 1 mostra o diagrama de blocos de um circuito sequencial. [1]

Figura 1 - Diagrama geral de um sistema digital. [2]

A informação armazenada nos elementos de memória num dado instante determina o

estado em que se encontra o circuito sequencial. O circuito sequencial recebe informação

binária das entradas que, juntamente com a informação do estado atual, determinam os

valores das saídas e os valores do próximo estado. Desta forma, fica

evidente que as saídas de um circuito sequencial dependem não apenas das entradas, mas

também do estado atual, armazenado nos elementos de memória. E o mesmo pode ser dito

para as variáveis de próximo estado. Em função deste comportamento sequencial, um circuito

sequencial é especificado pela sequência temporal de entradas, saídas e estados internos.

Os circuitos sequenciais podem ser divididos em dois tipos: síncronos e assíncronos.

2.1 Síncrono

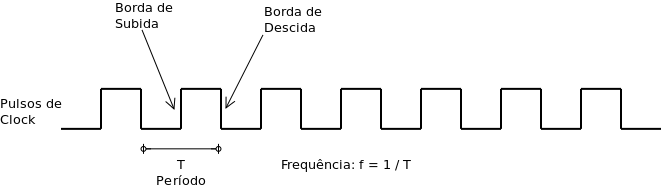

Um circuito sequencial síncrono utiliza um sinal denominado de relógio (clock) o qual tem a função de cadenciar uma eventual troca de estado. A Figura 2 mostra um exemplo de sinal de relógio. A forma de onda de um sinal de relógio é dita monótona, pois não se altera ao longo do tempo. Nela podem ser identificados a borda de subida, a borda de descida, o nível lógico zero e o nível lógico um. O tempo que decorre para o sinal se repetir é denominado período e é representado por T. Por exemplo, o tempo entre duas bordas de subida sucessivas é igual a T. Da mesma forma, o tempo entre duas bordas de descida sucessivas é igual a T.

Figura 2 - Exemplo de sinal de relógio (clock).

A frequência de um sinal de relógio, representada por f, é definida como sendo o

inverso do período, ou seja:

Para medir-se o período (T), usa-se os múltiplos do segundo: ms, us ns e ps. Para se medir

a frequência, usa-se os múltiplos do hertz: kHz, MHz e GHz. Um hertz equivale a uma vez por segundo.

2.1.1 Exercício de Fixação

Desenhe uma forma de onda que represente um clock de 100kHz.

(os alunos fazem, eles desenham)

2.2 Assíncrono

Em um circuito sequencial assíncrono as entradas mudam de acordo com uma ordem, isto faz com que o estado do circuito possa ser alterado a qualquer tempo, como consequência de uma mudança de suas entradas. Os elementos de memória utilizados nos circuitos sequenciais assíncronos apresentam uma capacidade de armazenamento que está associada diretamente ao atraso de propagação dos circuitos que os compõem. Em outras palavras, o tempo que esses circuitos levam para propagar uma mudança de suas entradas até suas saídas pode ser encarado como o tempo durante o qual eles retêm os valores aplicados antes da mudança, e esse fenômeno coincide com o conceito de memória, para os circuitos digitais. Nos circuitos sequenciais assíncronos, os elementos de memória são compostos por portas lógicas que proveem um atraso de propagação com valor adequado para o funcionamento do circuito. Então, um circuito sequencial assíncrono pode ser visto como um circuito combinacional com realimentação. O projeto de circuitos com realimentação apresenta grandes dificuldades, uma vez que seu funcionamento correto é dependente das características temporais dos componentes (portas lógicas e fios). A principal dificuldade provém do fato de que os componentes apresentam atrasos que não são fixos, podendo ser diferentes mesmo para exemplares com mesma função e de um mesmo fabricante. Desta forma, os circuitos sequenciais assíncronos têm sido evitados, sempre que possível, em favor do uso de circuitos sequenciais síncronos.

3 Latches

Os vários flip-flops existentes se diferenciam pelo número de entradas que possuem e na maneira pela qual tais entradas afetam o estado em que o flip-flop se encontra. Os tipos mais básicos de flip-flops são denominados latches. Os latches operam por níveis dos sinais de entrada (diz-se que são sensíveis a nível) e servem como base na construção dos flip-flops mais sofisticados. Apesar de serem capazes de armazenar informação binária, os latches são pouco utilizados na construção de circuitos seqüenciais síncronos por serem menos práticos do que os flip-flops.

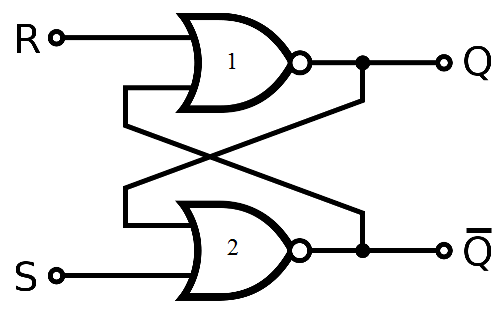

3.1 RS

O RS é o latch mais simples que existe. Ele pode ser construído com o uso de duas portas NOR de 2 entradas cada, conectadas conforme mostra a Figura 3. Note que há duas entradas, chamadas R e S, e duas saídas, e . Note também que existe uma conexão entre a saída e a outra entrada da NOR 2. Existe também uma conexão entre a saída e a outra entrada da NOR 1. Conexões entre saída e entrada são denominadas realimentações, e no caso de circuitos digitais, são responsáveis pela propriedade de armazenamento apresentada pelo circuito.

Figura 3 - Latch RS com portas NOR.

Assim, a análise do funcionamento do latch RS obedecerá a identificação de uma combinação de entradas (passo 1) capaz de determinar o estado do latch de maneira independente do estado anterior (se isso for possível). Desta forma Assumindo o estado determinado no passo 1 como sendo o estado inicial, aplicação de

uma nova combinação de entradas para verificar como o circuito se comporta (se muda de

estado ou não); Repetição dos passos 1 e 2 para cada combinação de entradas capaz de determinar o

estado do circuito de maneira independente.

A partir do procedimento anterior encontrar-se-á uma tabela de comportamento

denominada tabela de transição de estados (ou simplesmente, tabela de transição), a qual é

característica deste latch. Em particular, cada latch e cada flip-flop possui um comportamento

que pode ser expresso em termos de uma tabela de transferência que lhe é própria.

| R | S | Q | Q\ |

|---|---|---|---|

| 0 | 0 | Q | Q\ |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 1 | proibido | proibido |

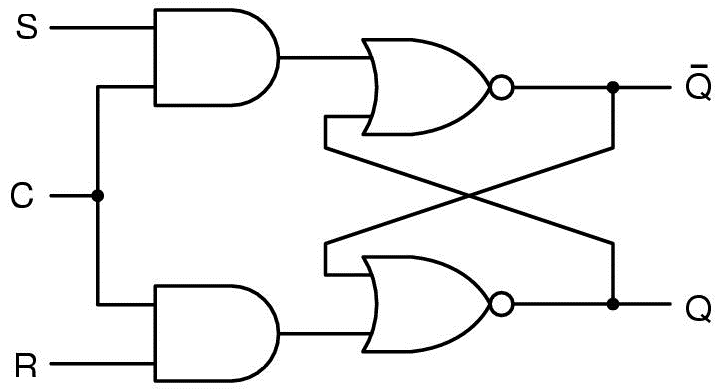

3.1.1 Latch RS Controlado

No latch RS uma alteração das entradas R e S pode acarretar uma troca de estado. Porém, em alguns casos pode ocorrer que os sinais conectados às entradas R e S sofram variações não desejadas, sendo válidos somente em alguns intervalos de tempo bem determinados. Nesse caso, seria interessante que houvesse uma entrada de maior prioridade que fosse encarregada de controlar a habilitação do latch, deixando-o sensível ou não aos valores das entradas R e S. A Figura 4 apresenta um latch RS controlado.

Figura 4 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

- Qa: saída do estado anterior.

3.2 Latch D

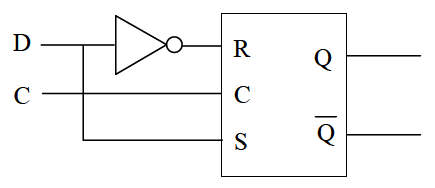

Para evitar a ocorrência do estado proibido foi criado O latch D que é construído a partir do latch RS, com a colocação de um inversor entre as entradas S e R, assim, fica assegurado que nunca ocorrerá a situação de entradas R=1 e S=1, responsáveis pelo surgimento do estado proibido. Desta forma, a tabela de transição do latch D pode ser derivada da tabela do latch RS controlado, onde as entradas R e S passam a ser a entrada D (com D=S). Duas combinações de entradas desaparecem: uma que resultava na manutenção do estado e outra que resultava no estado proibido. O símbolo do latch D é mostrado na Figura 5.

Figura 5 - Latch D.

| C | D | Q |

|---|---|---|

| 0 | X | Qa |

| 1 | 0 | 0 |

| 1 | 1 | 1 |

Conforme visto até agora, os latches controlados D e RS são ativados ou controlados pelo nível lógico do sinal de controle. Isso significa que, enquanto o sinal de controle estiver ativando o latch, eventuais variações das entradas D ou R e S serão percebidas pelo latch e este poderá mudar de estado. Essa característica é particularmente imprópria para a construção de circuitos sequenciais síncronos, uma vez que em tais circuitos qualquer troca de estado deve ocorrer de maneira sincronizada com o sinal de relógio.

4 Referências

[1] http://www.inf.ufsc.br/~guntzel/isd/isd4.pdf

[2] TOCCI, Ronald J.; WIDMER N. S.; GREGOGRY L. M. Sistemas digitais: princípios e aplicações. São Paulo: Prentice Hall, 2003.

| << | <> | >> |

|---|