DI2022802 2020 2 AULA14

1 Ambiente de Software EDA

Software EDA é uma categoria de ferramentas de software para projetar sistemas eletrônicos, tais como placas de circuitos impressos e circuitos integrados. Nesse material o software utilizado foi o Quartus®II Web Edition versão 9.2. Por intermédio desse ambiente é possível fazer simulação, testes e programação de dispositivos FPGAs. As fases de implementação de um projeto de circuito digital podem ser divididas em entradas de dados, compilação, simulação e programação.

A entrada de dados do projeto consiste em fornecer ao programa a especificação do projeto. Essa entrada pode ser realizada das seguintes formas:

[1] Editor Gráfico: Um diagrama lógico, desenvolvido a partir de elementos primitivos, portas lógicas básicas e outros componentes disponíveis em bibliotecas, que podem ser inseridos e interligados para criar o projeto.

[2] Editor de Texto: Uma descrição abstrata do circuito lógico, utilizando se comandos de uma linguagem estruturada de descrição de hardware como AHDL, VHDL ou Verilog, que descrevem o comportamento ou o funcionamento do circuito lógico.

[3] Editor de Símbolo Gráfico: Nesse caso, os elementos do diagrama lógico são símbolos gráficos criados pelo usuário ou macroinstruções gráficas existentes nas bibliotecas do software, que implementam alguma função lógica.

[4] Editor de forma de onda: Nesse caso, os dados de entrada são formas de onda que implementam alguma função desejada. A partir das formas de onda de entrada e saída o programa implementa a função lógica.

1.1 Software Quartus®II

Ao longo do curso será utilizado o software Quartus®II da Altera Corp., para se implementar e testar projetos de sistemas digitais, a serem desenvolvidos em aulas práticas. Este software é um ambiente de desenvolvimento integrado, ou EDA (Electronic Design Automation), que permite a realização de todas as etapas envolvidas no projeto de um sistema digital, desde a descrição de sua lógica, por meio de diagramas esquemáticos ou linguagens de descrição, simulação do circuito desenvolvido, até a gravação do projeto em um dispositivo lógico programável como um CPLD ou FPGA. O Quartus®II trabalha com um sistema orientado a projetos, ou seja, o software associa diversos arquivos à um projeto. Este sistema possibilita a utilização de componentes básicos em diversos projetos e simplifica a elaboração de projetos mais complexos uma vez que as funcionalidades de um grande sistema podem ser divididas em diversos sistemas mais simples e por fim, agrupados.

1.2 Criando Projeto com Quartus®II

A forma mais simples de se criar um projeto no Quartus®II é por meio do aplicativo Project Wizard. Para executar tal aplicativo, clique no menu File > New Project Wizard. Com isto a tela de apresentação do aplicativo Project Wizard irá se abrir. Clique em Next. Nesta tela pode-se escolher o diretório do projeto, o nome do projeto e o nome da entidade principal do projeto. É recomendável que para cada projeto, uma pasta diferenciada seja criada, para que não haja conflito entre os diversos arquivos gerados para cada projeto. Uma vez preenchidos os campos corretamente, clique em Next novamente. Nesta tela é possível incluir arquivos ao projeto. Através do botão “...” ao lado do campo File Name é possível definir o diretório do arquivo a ser incluído. Uma vez selecionado o arquivo, clique em Add para adicioná-lo ao projeto. Quando todos os projetos desejados forem incluídos, clique em Next. Com isso a próxima tela aparecerá.

OBS1: Caso esteja criando um projeto que não se utiliza de componentes previamente criados apenas clique em Next. Nesta tela deve-se escolher o componente a ser utilizado para implementar o projeto, ou seja, em qual dispositivo lógico programável o sistema será gravado. A família do dispositivo pode ser definida no campo Device Family. Na seção Show in Avaliable device list, na lista Available devices são apresentados todos os componentes da família escolhida que atendam aos requisitos definidos pelo filtro de componentes. Selecione o dispositivo adequado e clique em Next para prosseguir para a próxima tela.

OBS2: Observe no kit de desenvolvimento qual o dispositivo utilizado. Nesta janela é possível utilizar outras ferramentas de desenvolvimento em conjunto com o Quartus®II, para isto a ferramenta a ser utilizada deve estar instalada no computador, uma vez que estas ferramentas não acompanham o pacote de instalação do Quartus®II. No curso de sistemas digitais não será utilizada nenhuma ferramenta adicional. Assim sendo, clique em Next. Esta tela apresenta um resumo do projeto a ser criado. Verifique se todos os dados conferem com os desejados, caso haja algo incorreto, retorne à tela adequada, por meio do botão back e corrija o erro. Caso não haja erros, clique em Finish. Ao final do processo, a janela de projeto (Project Navigator) conterá o projeto criado.

1.3 Desenvolvendo um projeto usando diagrama esquemático

O uso de diagramas esquemáticos é uma das maneiras de se definir a lógica de um sistema digital dentro do ambiente de projeto do Quartus®II. Neste modo de projeto os componentes básicos de eletrônica digital como portas lógicas, flip-flops e multiplexadores, são representados por meio de blocos, os quais podem ser arranjados e associados de forma a se definir uma lógica de funcionamento.

Para se iniciar o desenvolvimento de um projeto que utilize o modo de diagrama esquemático, é necessário, primeiramente, adicionar ao projeto principal um arquivo que comporte este tipo de entrada. Assim sendo, para adicionar um arquivo de diagrama esquemático ao projeto clique em File -> New..., e uma nova janela aparecerá. Nessa janela é possível escolher o tipo de arquivo que se deseja criar. Selecione a opção Block Diagram / Schematic File e clique em Ok. Um novo arquivo de diagrama esquemático aparecerá na janela principal do Quartus®II. Para salvar este arquivo clique em File > Save as... e dê um nome ao arquivo, salvando-o na pasta do projeto principal.

OBS: Para arquivos de descrição de hardware, deve-se sempre lembrar que o nome da entidade principal do arquivo deve ser igual ao nome do arquivo.

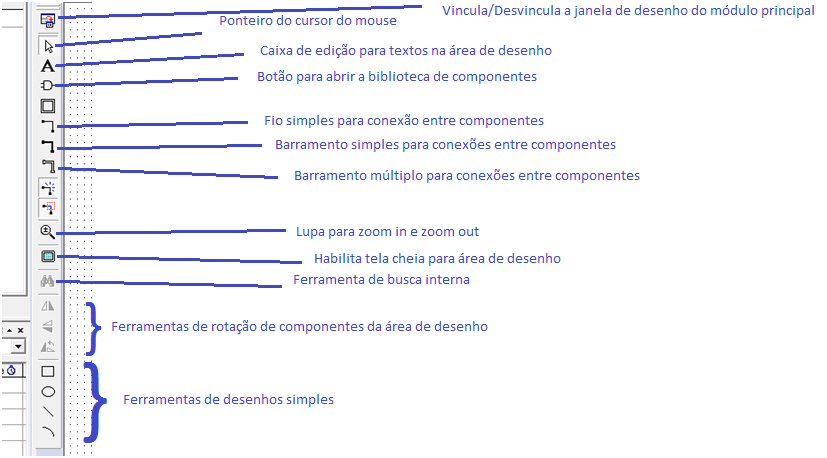

A tela de edição de diagramas esquemáticos é aberta, onde devemos destacar as funções de alguns botões:

- Atracar/Desatracar Janela: Permite separar a janela de diagrama esquemático da janela principal do Quartus®II.

- Ferramenta de Seleção: Permite selecionar elementos inseridos no arquivo.

- Ferramenta de texto: Permite inserir texto no arquivo, com fins explicativos ou de documentação.

- Ferramenta de símbolo: Permite inserir símbolos (componentes). Seu uso será detalhado posteriormente.

- Ferramenta de conexão: Realiza a ligação entre terminais dos componentes.

- Ferramenta de barramento: Realiza a ligação de barramentos (conjunto de sinais associados).

Através da ferramenta de símbolos é possível inserir componentes no arquivo. Clique nela, ou dê dois cliques na tela em branco, para inserir um componente. Feito isso uma janela com a biblioteca de componentes do software será aberta. Nessa janela, no campo Libraries, é possível explorar as diversas coleções de componentes do Quartus®II. As mais relevantes são listadas abaixo:

- Megafunctions: Tratam-se de funções complexas já prontas, necessitando muitas vezes de configuração. Serão melhor explicadas futuramente.

- Others: esta coleção possui modelos de componentes equivalentes aos da família de dispositivos 74xx. Dessa forma é possível realizar qualquer combinação lógica feita com componentes discretos dentro do CPLD.

- Primitives: componentes básicos:

- Buffers: diversos tipos de buffers, incluindo os de saída tri-state.

- Logic: elementos lógicos básicos (AND, OR, NOR, XOR, etc.) com diversos números de entradas.

- Others: elementos diversos.

- Pin: diversos tipos de pinos suportados pelo componente: entrada, saída ou bidirecional.

- Storage: elementos de armazenamento de dados, ou seja, flip-flops de diversos tipos.

2 Tutorial Quartus II

Este documento é um guia rápido que se aplica à versão 9.1 do Quartus(R) II para a plataforma Windows da Microsoft, no intuito de facilitar o aprendizado dos alunos num primeiro contato com essa ferramenta.

Este tutorial será apresentado utilizando um simples circuito digital, cujo objetivo é apresentar alguns dos comandos mais básicos do software Altera Quartus(R) II 9.1. Essa tarefa será realizada passo a passo.

Esta aula na WiKi foi criada a partir do documento Tutorial para Criar e Simular Circuitos Digitais no Altera Quartus(R) II - versão 9.1 - Laboratório Digital, elaborada por:

- Marlim Pereira Menezes

- Profa. Dra. Liria M. Sato

- Prof. Dr. Edson Midorikawa

Departamento de Engenharia de Computação e Sistemas Digitais Escola Politécnica - USP - Campus São Paulo, 2011.

2.1 Problema proposto

Deseja-se montar e simular o circuito digital, utilizando portas lógicas discretas, representado pela expressão booleana:

Utilizando-se a ferramenta Quartus(R) II versão 9.1 da Altera.

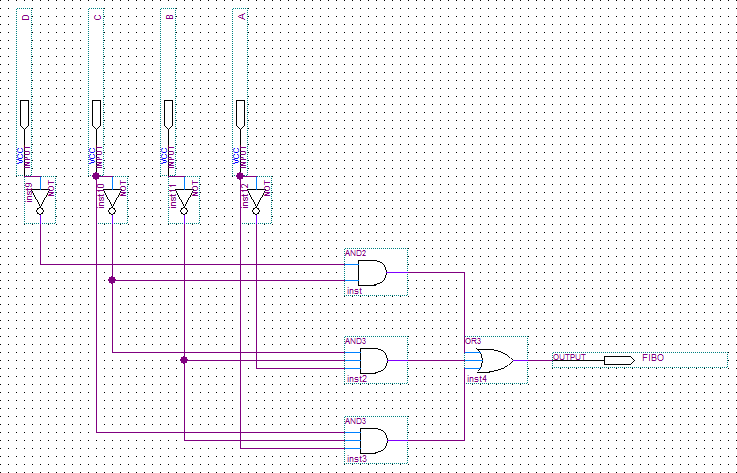

A Figura 1 mostra o circuito lógico obtido da expressão booleana anterior e, foi desenhado utilizando-se o software Quartus(R) II 9.1. O objetivo deste tutorial é reproduzi-lo, passo a passo da forma mais simples possível.

Figura 1 - Circuito da expressão F(A,B,C,D) modelado no Quartus(R) II 9.1.

Certifique-se de que o Altera Quartus(R) II versão 9.1 esteja instalado e pronto para uso no seu microcomputador.

2.1.1 Passo 1: Iniciando o Quartus(R) II

Localize o ícone de partida do Quartus(R) II na área de trabalho do Windows, dê duplo clique ou clique em iniciar e em seguida Pesquisar por programas e arquivos digite Quartus e tecle <Enter>.

Se aparecer uma janela intitulada Getting Started With Quartus(R) II Software, então clique com o botão esquerdo do mouse no "X" localizado no canto superior direito, para fechá-la. Aguarde a janela de Splash sumir e o Quartus(R) II estará pronto para o uso.

2.1.2 Passo 2: Criando um novo Projeto Digital

Criaremos um projeto para o circuito apresentado na Figura 1. O nome deste projeto será tutorial.

- File -> New Project Wizard... (na janela New Project Wizard: Introduction) -> Next >;

Aparecerá uma sequência de cinco páginas numeradas, mas não será necessário preencher todas neste tutorial. Para cancelar a criação do projeto, em qualquer momento, basta clicar no botão Cancel da página corrente. Preencha os campos necessários ao projeto nas páginas conforme indicado nas linhas que se seguem:

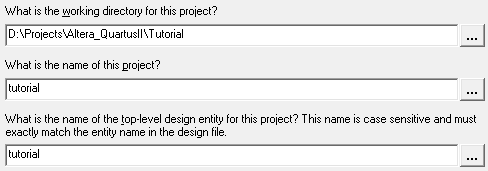

- Tela 1 de 5: New Project Wizard: Directory, Name, Top-Level Entity

- Na primeira caixa de texto, clique no botão () para escolher uma pasta onde será criado o seu projeto, na segunda caixa de texto digite tutorial para o nome do projeto e, a terceira será automaticamente preenchida com o texto digitado na segunda caixa de texto, mas poderá ser alterado. Em nosso caso, aceitaremos o mesmo nome dado ao projeto (tutorial). A Figura 2 mostra a parte da tela de criação do projeto.

Figura 2 - Tela 1 de criação do projeto.

- Pressione no botão Next > para avançar;

- Tela 2 de 5: New Project Wizard: Add Files

- Não será inserido arquivo externo, então pressione em Next > para avançar;

- Página 3 de 5: New Project Wizard: Family & Device Settings

- Aqui é possível selecionar o FPGA a ser utilizado no projeto durante a sua criação. Mas, esta opção será mostrada mais adiante no Passo 4 deste tutorial;

- Pressione em Next > para avançar;

- Página 4 de 5: New Project Wizard: EDA Tool Settings

- Ignore esta página e pressione em Next > para avançar;

- Página 5 de 5: New Project Wizard: Summary

- Esta página contém um resumo das configurações feitas anteriormente para o projeto sendo criado;

- Pressione em Finish para concluir a criação do projeto.

2.1.3 Passo 3: Criando o arquivo para o projeto do circuito digital

Um projeto criado no Quartus(R) II 9.1, normalmente estará vazio, entretanto, deveremos criar os módulos que o compõe. Neste passo prepararemos o ambiente de desenvolvimento para receber o circuito digital que será simulado. Para isto execute os comandos a seguir:

- File -> New (Aparecerá uma janela intitulada New);

- Design Files -> Block Diagram/Schematic File -> OK, note que a área á direita da janela principal do Quartus(R) II aparecerá com uma grade de pontos (esses pontos são utilizados como coordenadas da tela para a disposição dos diversos componentes que constituem o circuito digital).

Na margem esquerda da área de desenho há uma régua vertical com alguns botões, que disponibilizam as opções de projeto tais como a biblioteca dos componentes, caixa de edição de texto, lupa para zoom etc. A Figura 3 mostra os elementos da régua de ferramentas do Quartus(R) II 9.1.

Figura 3 - Régua de ferramentas de desenvolvimento do Quartus(R) II 9.1.

2.1.4 Passo 4: Escolhendo o FPGA a ser usado no projeto

Para especificar o FPGA que será usado no projeto execute as seguintes instruções:

- Assignments -> Device... (Aparecerá a janela Settings); então selecione:

- (Category: Device) -> (Family: Ciclone II) -> (Available devices: Name: EP2C35F672C6) -> OK (Este chip FPGA foi selecionado porque é o que tem no Laboratório Digital).

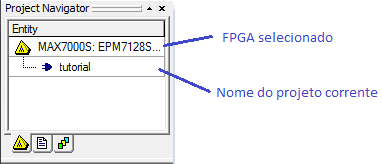

Para verificar qual é o FPGA sendo usado no projeto, basta observar a região Project Navigator: Entity, normalmente localizado à esquerda do ambiente do Quartus(R) II 9.1. Veja a Figura 4.

Figura 4 - Project Navigator: Entity com o FPGA selecionado.

2.1.5 Passo 5: Colocando os componentes na área de desenho

Utilize a Figura 1 como referência, se necessário.

Execute uma das sequências de comandos abaixo para abrir a janela Symbol contendo a biblioteca dos diversos componentes disponibilizados pelo Quartus(R) II 9.1.

- [Botão direito do mouse, na área de desenho] -> Insert -> Symbol... ou;

- [Botão direito do mouse, na área de desenho] -> Insert -> Symbol as Block... ou;

- Clique no botão com o desenho de uma porta lógica (AND), localizado na régua de ferramentas.

Na janela Symbol, execute a sequência de comandos:

Se você desejar mais de uma cópia do componente selecionado, então ative o recurso [Repeat-insert mode], caso contrário mantenho-o desativado. Este recurso estando ativado não nos impede de colocar apenas uma cópia do componente desejado na área de desenho, bastando para isto pressionar a tecla [ESC] ou executando a sequência de comandos com o mouse: [Botão direito do mouse] -> Cancel.

Vamos colocar os componentes necessários ao nosso exemplo na área de desenho. Para isto, execute os comandos a seguir:

- Uma porta lógica AND de duas entradas:

- (AND2) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic -> and2 -> OK -> [Botão esquerdo do mouse]

- Duas portas lógicas AND de três entradas:

- (AND3) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic -> and3 -> OK -> [Botão esquerdo do mouse]

- Uma porta lógica OR de três entradas:

- (OR3) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic -> or3 -> OK -> [Botão esquerdo do mouse]

- Quatro portas inversoras NOT:

- (NOT) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] logic -> not -> OK -> [Botão esquerdo do mouse]

- Quatro pinos INPUT para as entradas A, B, C e D:

- (INPUT) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] pin -> input -> OK -> [Botão esquerdo do mouse]

- Um pino OUTPUT para a saída FIBO:

- (OUTPUT) -> Libraries -> [+] c:/altera/91/quartus/libraries/ -> [+] Primitives -> [+] pin -> output -> OK -> [Botão esquerdo do mouse]

Arraste o pino OUTPUT para próximo da saída da porta lógica or3, conforme Figura 1.

Vamos girar os quatro pinos de entrada INPUT em 270o, de modo que fiquem com a extremidade "pontiaguda" para baixo, vide Figura 1. Para isto, selecione um pino de cada vez (clicando com o mouse sobre ele) e execute os seguintes passos:

- [Botão direito do mouse] -> Rotate by Degrees -> 270

Repita a operação anterior para girar os quatro inversores em 270o.

Agora reorganize todos os componentes na área de desenho, de modo a ficarem dispostos como na Figura 1. Salve o projeto conforme descrito no Passo 6.

2.1.6 Passo 6: Salvando o projeto em disco

É uma boa prática de desenvolvimento salvar, frequentemente, o projeto ao longo de seu desenvolvimento. Execute os comandos a seguir:

- File -> Save -> (Save as type: Block Diagram/Schematic File (*.bdf)) -> (File Name: tutorial) -> (Save in: Tutorial) -> Save.

2.1.7 Passo 7: Dando nomes aos componentes

Para dar nome a um componente basta dar duplo clique sobre o componente desejado e seguir os passos (use a figura 1 como referência, se necessário):

Pinos de entrada: D, C, B, A.

- Pin name(s): D -> OK (Na janela "Pin Properties").

- Pin name(s): C -> OK (Na janela "Pin Properties").

- Pin name(s): B -> OK (Na janela "Pin Properties").

- Pin name(s): A -> OK (Na janela "Pin Properties").

Pino de saída: FIBO

- Pin name(s): FIBO -> OK (Na janela "Pin Properties").

Não será necessário mudar os nomes das portas lógicas, mas os procedimentos são os mesmos.

2.1.8 Passo 8: Conectando os diversos componentes

Conectar os componentes do circuito (veja a Figura 1) é muito simples, bastando para isto posicionarmos o ponteiro do mouse sobre o terminal desejado do componente de origem, pressionar o botão esquerdo, mantê-lo pressionado e arrastar até o ponto ou terminal desejado do componente destino, soltando-o em seguida. O aspecto do ponteiro do mouse será uma cruz com o desenho Fio simples.

- Lembrete

- É boa prática de desenvolvimento usando computador sempre salvar o arquivo, para se prevenir contra uma eventual queda de energia ou travamentos na máquina.

2.1.9 Passo 9: Salvando o arquivo do circuito

Execute:

- File -> Save

2.1.10 Passo 10: Compilando o projeto

Uma vez terminado o desenho do circuito, devemos compilá-lo, para em seguida fazermos a simulação. A compilação é feita seguindo-se os passos abaixo:

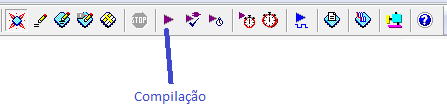

- Processing -> Start Compilation, ou um clique no botão indicado na Figura 5, da barra de ferramentas do Quartus(R) II 9.1.

Figura 5 - Barra de ferramentas do Quartus(R) II 9.1, destacando o botão de compilação.

2.1.11 Passo 11: Criando a Simulação do projeto

Execute os comandos a seguir, para criar uma simulação:

- File -> New -> [+] Verification/Debugging Files -> Vector Waveform File -> OK

Neste momento um arquivo que conterá os dados da simulação será criado e uma janela própria da ferramenta de simulação do Quartus(R) II 9.1 será aberta e ficará pronta para uso. Essa janela é dividida em quatro partes:

- Régua de ferramentas para as configurações da simulação;

- Régua com as bases de tempo;

- Coluna para os nomes dos pontos de teste com a base de tempo e;

- Área das cartas de tempo (timing chart) do circuito.

2.1.12 Passo 12: Salvando a simulação

Salve o arquivo de simulação com o mesmo nome do projeto, ou seja, tutorial. Para isto execute a sequência de comandos a seguir:

- File -> Save -> (Save as type: Vector Waveform File (*.vwf)) -> (Save in: Tutorial) -> (File name: tutorial) -> Save

2.1.13 Passo 13: Incluindo os pontos de teste para a Simulação

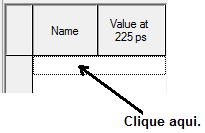

Clique o botão direito do mouse sobre a região dos pontos de teste do circuito simulado (colunas: Name e Value at). Veja a Figura 6:

Figura 6 - Área destinada à declaração dos pontos de teste do circuito.

Podemos entrar com um ponto de teste de cada vez ou um conjunto, dentre os disponíveis, em uma operação só. Veremos os dois jeitos:

- Entrando um ponto de teste por vez

- [Botão Diteiro do Mouse] -> Insert -> Insert Node or Bus... -> (Name: A) -> OK

- Entrando um conjunto dentre ospontos de teste disponíveis ou todos de uma só vez

- [Botão Diteiro do Mouse] -> Insert -> Insert Node or Bus... -> Node Finder... -> (Named: *) -> (Filter: Pins: All) -> List -> [>>] -> OK -> OK

2.1.14 Passo 14: Determinando os sinais dos pontos de teste para simulação

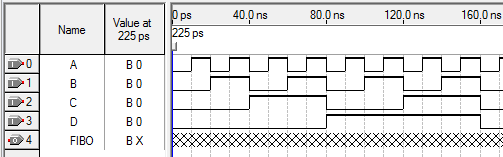

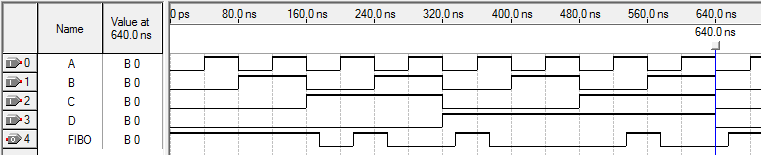

No nosso caso temos cinco pontos de teste, isto é, quatro variáveis de entrada (D, C, B, A) e uma de saída (FIBO), então configuraremos os sinais das entradas conforme disposto numa tabela verdade de quatro variáveis, onde 0 indica nível lógico zero e 1 indica nível lógico um. Veja a Figura 7.

Figura 7 - Variáveis de entrada/saída para análise da simulação do projeto.

Siga os passos abaixo: Utilize a região das variáveis, vide Figura 7:

- Variável A (linha 0): [Clique no desenho >>0] -> (Radix: Binary) ->Timing -> (Multiplied by: 1) -> OK

- Variável B (linha 1): [Clique no desenho >>1] -> (Radix: Binary) ->Timing -> (Multiplied by: 2) -> OK

- Variável C (linha 2): [Clique no desenho >>2] -> (Radix: Binary) ->Timing -> (Multiplied by: 4) -> OK

- Variável D (linha 3): [Clique no desenho >>3] -> (Radix: Binary) ->Timing -> (Multiplied by: 8) -> OK

- Deixe a variável FIBO com a configuração original.

2.1.15 Passo 15: Configurando a simulação

O Altera Quartus(R) II 9.1 tem três modos de simulação: Functional; Timing e; Timing using Fast Timing Model. O default é o modo Timing que considera os atrasos internos do tempo no FPGA e será aqui adotado. Na seção Outras Informações é apresentado como proceder para configurar o modo de simulação Functional. Vamos configurar o instante final (End Time) e a largura da grade de tempos (Grid Size) da simulação. Clique na aba tutorial.vwf, para trazer a sua janela ao primeiro plano do ambiente de desenvolvimento.

- Edit -> End Time... -> (Time: 1.0 μs) -> OK (Para podermos analisar melhor o comportamento do circuito)

- Edit -> Grid Size… -> (Period: 40.0 ns) -> OK

Nota: Salve o arquivo com a sequência de teclas [Ctrl+S] ou executando os comandos do Passo 12.

2.1.16 Passo 16: Executando a simulação

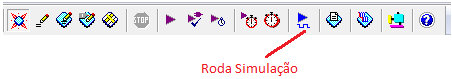

A simulação pode ser iniciada por três caminhos diferentes:

- Clique na aba [Quartus II] -> Simulator Tool -> Start -> OK (Janela de Diálogo informando o resultado da compilação) -> Report;

- Processing -> Start Simulation -> OK (Janela de Diálogo informando o resultado da compilação) e;

- Através da régua de ferramentas, conforme indicado na Figura 8:

Caso a simulação tenha sido iniciada a partir do menu (caminho 1) ou pressionando-se o botão em destaque na Figura 8 (caminho 3), então poderemos visualizar os relatórios (inclusive a carta de tempos) executando a sequência de comandos: Processing -> Simulation Report, ou pelo atalho [Ctrl+Shift+R]. A Figura 8 mostra o botão da barra de ferramentas usado para executar a simulação.

Figura 8 - Botão para iniciar a simulação no Simulador do Quartus(R) II 9.1.

O resultado da simulação é mostrado na Figura 9:

Figura 9 - Carta de tempos (Timing Chart) da simulação no modo Timing.

Note que o FPGA escolhido (Ciclone II– EP2C35F672C6) apresenta atraso significativo no pino de saída em relação aos pinos de entrada.

Próximo passo é transformar a simulação em um arquivo .sof para a gravação do FPGA.

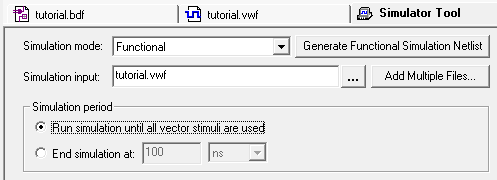

2.2 Configurando o Modo de Simulação Funcional

Para mudar o modo de simulação, que é visto na Figura 10, execute a sequencia de comando, a seguir:

- Processing -> Simulator Tool

Para configurar o modo Funcional, deve-se preencher o modo de simulação com Functional.

Figura 10 - Modo de simulação funcional.

Note que no modo Functional o botão [Generate Functional Simulation Netlist] ficou ativo e esse deve ser pressionado, para que a simulação neste modo funcione corretamente. Então, a próxima sequência de comandos a ser seguida é:

- Clique em [Generate Functional Simulation Netlist] -> OK -> Start -> OK -> Report

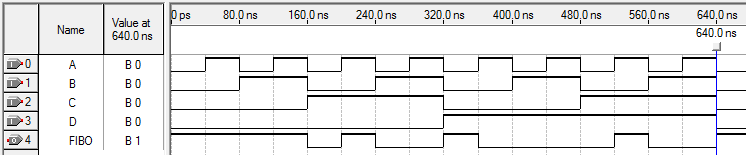

O resultado da simulação é mostrado na Figura 11:

Figura 11 - Carta de tempos (Timing Chart) da simulação no modo funcional.

Compare as cartas de tempo das Figuras 9 e 11. Observe a diferença clara entre os resultados das simulações nos modos Timing e Functional.

2.3 Conclusão

Este tutorial procurou iniciar o usuário no Altera Quartus(R) II 9.1 passo a passo, de forma bastante simples, de modo que o mesmo possa se aperfeiçoar, por conta própria, a partir deste ponto.

- Resumindo

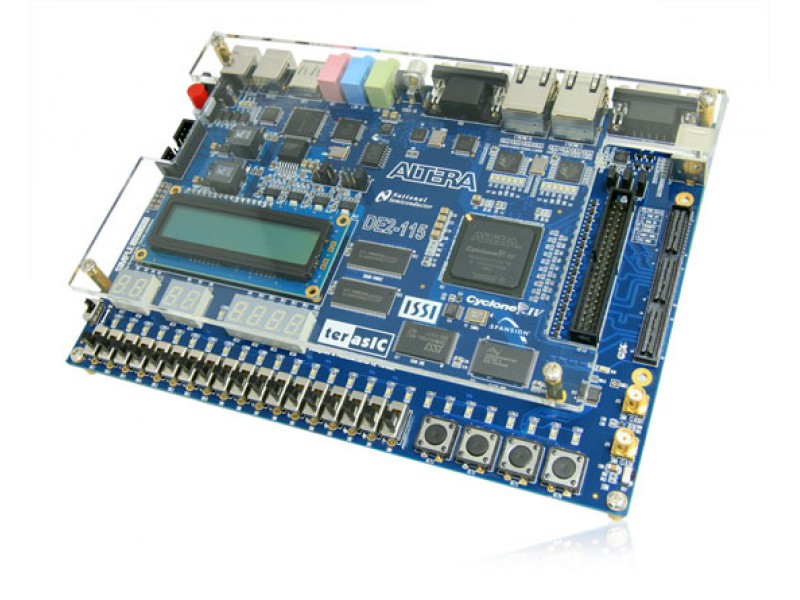

3 Kit DE2

- DEVICE

- EP2C35F672C6

- FAMILIA

- "Cyclone II"

Figura 12 - Placa de Desenvolvimento DE2.

| Resumo dos Pinos |

|---|

|

DEVICE EP2C35F672C6

FAMILY "Cyclone II"

|

- Pinagem completa

- ftp://ftp.altera.com/up/pub/Altera_Material/12.1/Boards/DE2/DE2.qsf

4 Exercícios

4.1 Parte 1

- O que é um Ambiente de Software EDA?

- Um software EDA normalmente possui quatro entrada de dados do projeto. Quais são e para que servem?

- Qual a maneira mais fácil de criar um projeto no software Quartus?

- O que é um diagrama esquemático?

- O que é a ferramenta "símbolos" (componentes)?

- Quais as bibliotecas principais de "componentes"?

- Como se divide a biblioteca "Primitives".

- Quais os três tipos de "pinos"?

- Nos projetos, porque usar Ciclone II - EP2C35F672C6?

- Por que o nome do projeto deve ser o mesmo que da entidade (entity)?

- Para que eu devo "compilar" meu projeto?

- Para que simular meu projeto?

- Na configuração da simulação, para que definir "End Time" e "Grid Size"?

- Ao rodar a simulação eu posso configurá-la para Timing ou Functional? Qual a diferença entre os dois tipos de simulação?

4.2 Parte 2

[1] Desenvolvimento via diagrama esquemático, utilizando portas lógicas discretas, a montagem de um circuito combinacional capaz de executar a seguinte operação:

[2] Desenvolva via diagrama esquemático, utilizando FF tipo D (CI 7474), a montagem de um circuito do contador Johnson de 4 bits. Simule o funcionamento do circuito

[3] Desenvolva via diagrama esquemático, um circuito MUX de 4 entradas. Simule o funcionamento do circuito.

[4] Desenvolva via diagrama esquemático, um circuito do contador em anel de 4 saídas com clear e preset em apenas um dos FF. Simule o funcionamento do circuito.

[5] Desenvolva um relógio digital com segundos e minutos, utilizando os blocos acima.

| Relógio MM:SS |

|---|

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY relogio_digital IS

PORT( clock : IN STD_LOGIC;

disp_uni_s : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

disp_dez_s : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

disp_uni_m : OUT STD_LOGIC_VECTOR(6 DOWNTO 0);

disp_dez_m : OUT STD_LOGIC_VECTOR(6 DOWNTO 0)

);

END relogio_digital;

ARCHITECTURE Relogio OF relogio_digital IS

SIGNAL clock1Hz : STD_LOGIC := '0';

SIGNAL seg : INTEGER RANGE 0 TO 59 := 0;

SIGNAL min : INTEGER RANGE 0 TO 59 := 0;

SIGNAL BCD_uni_s : INTEGER RANGE 0 TO 9 := 0;

SIGNAL BCD_dez_s : INTEGER RANGE 0 TO 9 := 0;

SIGNAL BCD_uni_m : INTEGER RANGE 0 TO 9 := 0;

SIGNAL BCD_dez_m : INTEGER RANGE 0 TO 9 := 0;

COMPONENT divisor_de_clock

GENERIC( freq_entrada : INTEGER := 27000000;

freq_saida : INTEGER := 1

);

PORT( clock27MHz : IN STD_LOGIC;

clock1Hz : OUT STD_LOGIC

);

END COMPONENT;

COMPONENT BCD_7seg_AC

PORT( BCD : IN INTEGER;

segmentos : OUT STD_LOGIC_VECTOR(6 DOWNTO 0) --abcdefg

);

END COMPONENT;

BEGIN

divisor1 : divisor_de_clock

GENERIC MAP(2700000,1)

PORT MAP(clock,clock1Hz);

PROCESS(clock1Hz)

BEGIN

IF RISING_EDGE(clock1Hz) THEN

IF seg = 59 THEN

seg <= 0;

IF min = 59 THEN

min <= 0;

ELSE

min <= min+1;

END IF;

ELSE

seg <= seg + 1;

END IF;

END IF;

END PROCESS;

BCD_uni_s <= seg MOD 10;

BCD_dez_s <= seg / 10;

BCD_uni_m <= min MOD 10;

BCD_dez_m <= min / 10;

DISP1 : BCD_7seg_AC

PORT MAP(BCD_uni_s,disp_uni_s);

DISP2 : BCD_7seg_AC

PORT MAP(BCD_dez_s,disp_dez_s);

DISP3 : BCD_7seg_AC

PORT MAP(BCD_uni_m,disp_uni_m);

DISP4 : BCD_7seg_AC

PORT MAP(BCD_dez_m,disp_dez_m);

END Relogio;

|

5 Referências

[1] Quartus II Introduction Using Schematic