Como obter o Fmax do projeto no Quartus

Para obter o valor da frequência máxima (Fmax) em que o circuito opera é necessário fazer no mínimo a etapa de Timing Analysis. Dependendo da familia de FPGAs, é possível que seja mostrado um único valor ou até 3 valores correspondentes a diferentes modelos de simulação. Por exemplo no caso do Cyclone IV E, existem os modelos:

- Slow 1200mV 85C Model (mais lento)

- Slow 1200mV 0C Model

- Fast 1200mV 0C Model (mais rápido)

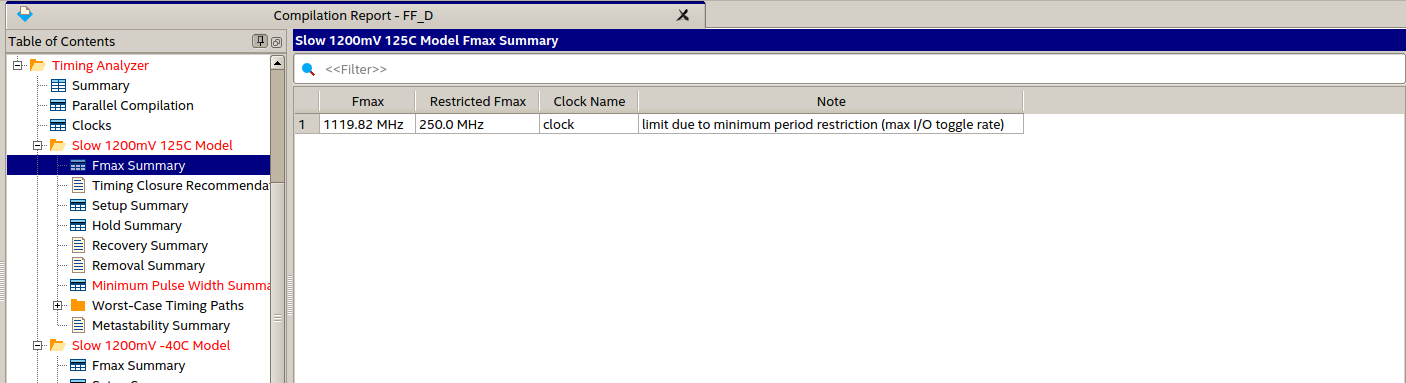

A visualização do Fmax pode aparecer diretamente no Compilation Report na pasta Timing Analyzer.

Figura 1 - Fmax no Compilation Report

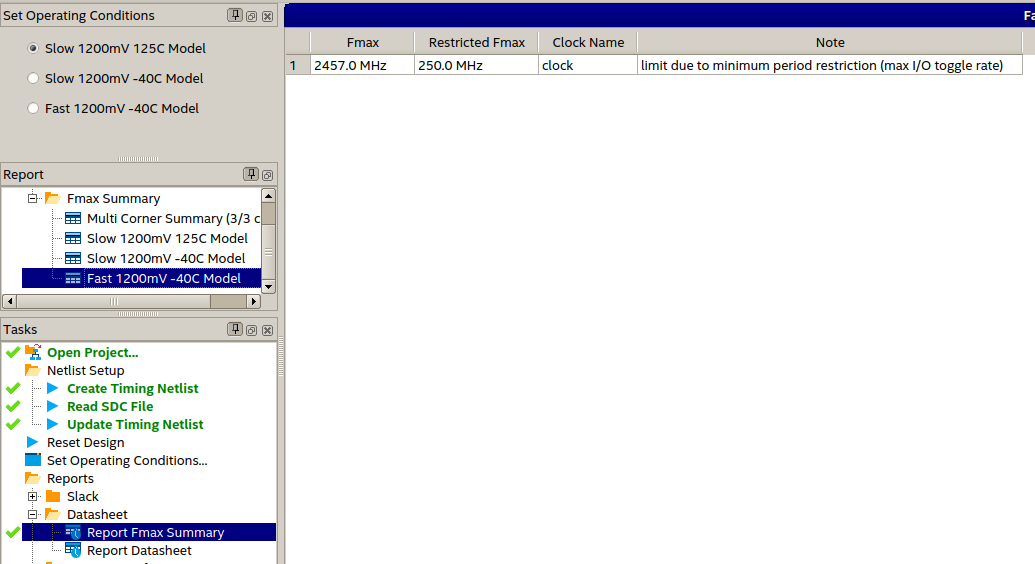

Quando o valor do Fmax não aparece no Compilation Report, é necessário abrir adicionalmente o [Tools > Timing Analyser] e:

- 1) no painel Tasks clicar em [Update Timing Netlist]

- 2) no painel Set Operating Conditions selecionar o modelo de simulação

- 3) no painel Tasks, na pasta Datasheet, clicar em [Report Fmax Summary] para cada modelo.

Após fazer a análise para os modelos, o resultado do Fmax será mostrado na pasta [Fmax Summary] da aba Report

Figura 2 - Fmax no Timing Analyzer

Em ambos os casos são mostrados dois valores de frequência máxima (Fmax).

A frequencia máxima é o máximo clock que pode ser aplicado se violar os tempos de setup (tSU) e de hold (tH).

- O Fmax é a frequencia máxima que o projeto pode utilizar.

- O Fmax restrito considera os limites do dispositivo. Exemplo:

limit due to minimum period restriction (max I/O toggle rate)

Nota: Em comparações de implementações nas aulas recomendamos sempre observar o valor de Fmax (sem restrições).