Predefinição:DiegoMedeiros-SST20707

Ementa e referências bibliográficas

Informações da disciplina

- Professor: Diego da Silva de Medeiros

- Plano de Ensino 2015-1

Diário de aula

| 2015-1 - Clicar no "+" para expandir | |||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

| |||||||||||||||||||||

Aulas

Apresentação da disciplina

- Roteiro

- Apresentação do professor;

- Apresentação da disciplina (Plano de Ensino);

- Avaliações: Trabalhos e Projeto Final

- Grupo da disciplina: IFSCTeleSST

- Atividade

- Ler capítulo 18 do Livro do Pedroni

Dispositivos lógicos programáveis - PLD

PLDs em sistemas digitais

- Sistema digital: Saída digital definida em função de processamento realizado em entrada digital.

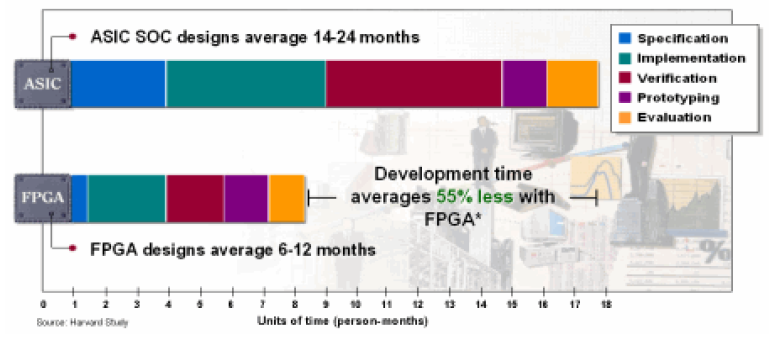

- Os sistemas digitais foram por muito tempo projetados usando a chamada lógica fixa, composta por CIs (circuitos integrados) TTL que implementavam portas lógicas. Em meados de 1970, foram introduzidos os PLDs (Programmable Logic Devices), chips de uso geral cujo hardware pode ser configurado para atender especificações. Com os PLDs, sistemas digitais poderiam ser projetados a partir de CIs genéricos, com funções definidas a partir de configurações armazenadas em memórias. Desta forma, os PLDs possuem as seguintes vantagens sobre sistemas de lógica fixa [2]:

- Redução de custos de projeto, chamados de custos NRE (nonrecurring engineering cost - custo de engenharia não recorrente), com a abolição de desenvolvimentos complexos de placas

- Rapidez de desenvolvimento

- Flexibilidade no desenvolvimento: a adição de funcionalidades é feita por simples mudanças no arquivo de configuração

- Rapidez de produção do CI: por serem padronizados, os PLDs possuem entrega imediata

- Atualização de hardware em tempo real

- Uma alternativa de projeto é o uso de microcontroladores, dispositivos programáveis a nível de software. Porém, mesmo nesses casos, os PLDs possuem vantagens [3]:

- PLDs são mais simples de desenvolver, pois alterações no projeto são feitas instantaneamente

- Sistemas com processadores customizados possuem desenvolvimento lento e oneroso

- Sistemas mais genéricos tendem a ter custos menores pela possibilidade de uso em diversas aplicações, facilitando o estoque de itens

Em função da arquitetura e tecnologia empregada, os PLDs foram classificados em SPLDs (simple PLDs) ou CPLDs (complex PLDs).

SPLDs

São denominados SPLDs os seguintes dispositivos:

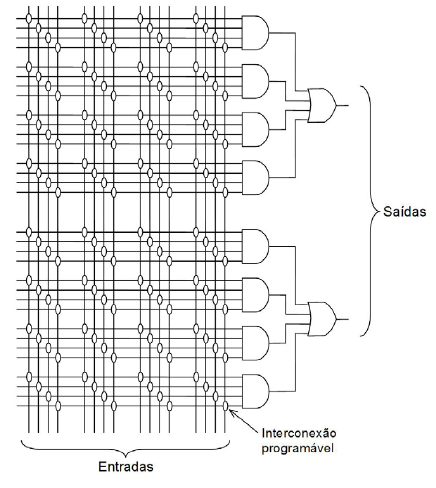

- PAL - Programmable Array Logic

Um arranjo programável de portas AND seguido por um arranjo fixo de portas OR.

Essa foi a primeira implementação de PLDs, e se baseia no fato de que qualquer função lógica pode ser reescrita como uma soma de produtos (SOP - sum of products) [4]. Por exemplo, sendo abaixo a tabela verdade da soma aritmética de um bit u de uma posição de um circuito somador, como função de x e y e do carry ci

| ci | x | y | u(ci,x,y) |

|---|---|---|---|

| 0 | 0 | 0 | 0 |

| 0 | 0 | 1 | 1 |

| 0 | 1 | 0 | 1 |

| 0 | 1 | 1 | 0 |

| 1 | 0 | 0 | 1 |

| 1 | 0 | 1 | 0 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | 1 |

Sendo as linhas 2, 3, 5 e 8, as que possuem saída 1, podemos escrever u como [5]:

Os PAL tem, porém, como limitação, a implementação apenas em circuitos combinacionais.

- PLA - Programmable Logic Array

Muito semelhante aos PALs, os PLA diferenciam-se no fato de que tanto as ligações AND quanto OR são programáveis.

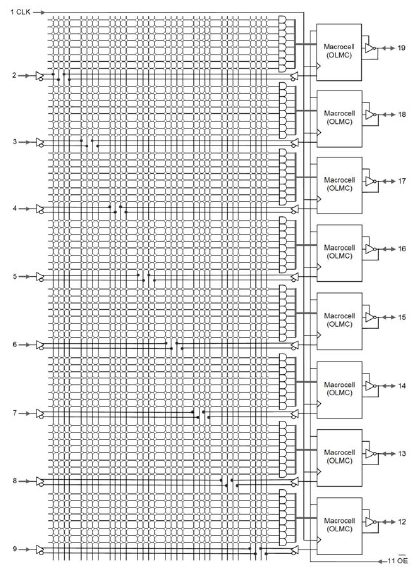

- GAL - Generic Array Logic

Características adicionais com relação aos PALs:

- Célula de saída (chamada de OLMC - output logic macrocell) com flip-flop, porta XOR, multiplexadores

- Inclusão de um sinal de retorno (feedback)

- Utilização de memórias EEPROM na programação do circuito

Um exemplo dessa arquitetura pode ser visto na figura abaixo:

CPLDs

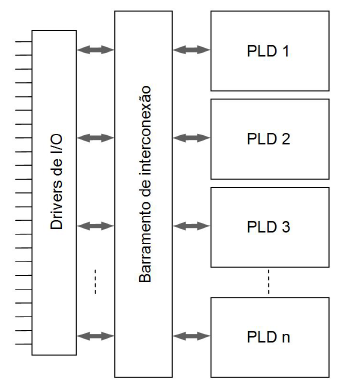

Como o próprio nome já adianta, os CPLDs possuem arquitetura muito mais complexa que os SPLDs. De fato, os primeiros CPLDs eram formados pela interconexão programável de vários SPLDs, além de outros avanços. Na figura abaixo, a arquitetura básica de um CPLD:

FPGAs - Field programmable gate arrays - Arranjo de portas programável em campo

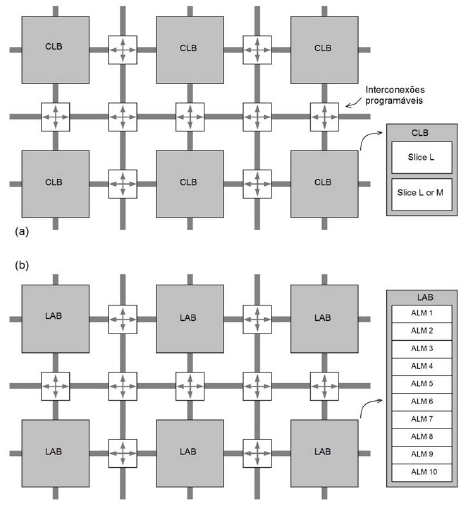

Os FPGAs estendem as capacidades dos CPLDs, sendo diferentes em arquitetura, tecnologia, características embutidas e custo. Por serem voláteis, precisam de uma memória de configuração não volátil para armazenar a programação do hardware. Uma simplificação da arquitetura de FPGAs pode ser vista na figura abaixo. No caso, CLBs (configurable logic blocks) e LABs (logic array blocks) são blocos semelhantes à SPLDs GAL.

Além desses blocos, FPGAs costumam possuir também:

- Blocos RAM: Possibilitam o uso direto de memória, sem a necessidade de projetá-las

- Blocos DSP: Muito utilizados em aplicações de processamento de áudio e vídeo digitais, o bloco DSP implementa operações de soma, multiplicação e variáveis.

Referências

[1] Midorikawa, Edson. Projeto de sistemas digitais. Disponível em Link. Acesso em 09/02/2015.

[2] Xilinx. What is Programmable Logic? Disponível em Link. Acesso em 09/02/2015.

[3] Parnell, Karen & Bryner, Roger. Comparing and contrasting FPGA and microprocessor system design and development. Disponível em Link. Acesso em 09/02/2015.

[4] Pedroni, Volnei A. Eletrônica digital moderna e VHDL. Disponível em Link. Acesso em 09/02/2015.

[5] Wikipedia. Canonical normal form. Disponível em Link. Acesso em 09/02/2015.