Mudanças entre as edições de "Pinagem dos dispositivos de entrada e saída do kit MERCURIO IV"

(→SDRAM) |

(→SDRAM) |

||

| Linha 162: | Linha 162: | ||

==SDRAM== | ==SDRAM== | ||

| − | A placa Mercurio IV possui um chip de SDRAM de 512Mbits (64 MBytes). As tabelas abaixo apresentam as o timming para configuração do controlador de memória e o roteamento dos pinos para a FPGA da placa. | + | A placa Mercurio IV possui um chip de SDRAM de 512Mbits (64 MBytes). As tabelas abaixo apresentam as o timming para configuração do controlador de memória e o roteamento dos pinos para a FPGA da placa. Para integração com o NIOS2, é necessário utilizar um PLL para dar um atraso de 3ns na fase do clock encaminhado ao chip de memória. |

| − | |||

<table border="1" cellpadding="2"> | <table border="1" cellpadding="2"> | ||

| − | <tr><th> Signal <th> | + | <tr><th>Signal</th><th>Name FPGA</th><th>Pin No. Description</th><th>I/O Standard</th></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[0]</td><td>P2</td><td>SDRAM Address Bit 0</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[1]</td><td>R1</td><td>SDRAM Address Bit 1</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[2]</td><td>P3</td><td>SDRAM Address Bit 2</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[3]</td><td>R2</td><td>SDRAM Address Bit 3</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[4]</td><td>P4</td><td>SDRAM Address Bit 4</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[5]</td><td>P5</td><td>SDRAM Address Bit 5</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[6]</td><td>N5</td><td>SDRAM Address Bit 6</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[7]</td><td>M4</td><td>SDRAM Address Bit 7</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[8]</td><td>N1</td><td>SDRAM Address Bit 8</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[9]</td><td>M2</td><td>SDRAM Address Bit 9</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[10]</td><td>P1</td><td>SDRAM Address Bit 10</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[11]</td><td>M3</td><td>SDRAM Address Bit 11</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_A[12]</td><td>L6</td><td>SDRAM Address Bit 12</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_BA[0]</td><td>J4</td><td>SDRAM Bank Select Bit 0</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_BA[1]</td><td>H2</td><td>SDRAM Bank Select Bit 1</td><td>3v3</td></tr> |

| − | <tr><td> | + | <tr><td>SDRAM_D[0]</td><td>B2</td><td>SDRAM Data Bit 0</td><td>3v3</td></tr> |

| + | <tr><td>SDRAM_D[1]</td><td>B1</td><td>SDRAM Data Bit 1</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[2]</td><td>C2</td><td>SDRAM Data Bit 2</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[3]</td><td>C1</td><td>SDRAM Data Bit 3</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[4]</td><td>D2</td><td>SDRAM Data Bit 4</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[5]</td><td>E3</td><td>SDRAM Data Bit 5</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[6]</td><td>F2</td><td>SDRAM Data Bit 6</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[7]</td><td>F1</td><td>SDRAM Data Bit 7</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[8]</td><td>J2</td><td>SDRAM Data Bit 8</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[9]</td><td>H6</td><td>SDRAM Data Bit 9</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[10]</td><td>H5</td><td>SDRAM Data Bit 10</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[11]</td><td>J3</td><td>SDRAM Data Bit 11</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[12]</td><td>G3</td><td>SDRAM Data Bit 12</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[13]</td><td>G4</td><td>SDRAM Data Bit 13</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[14]</td><td>G5</td><td>SDRAM Data Bit 14</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_D[15]</td><td>E4</td><td>SDRAM Data Bit 15</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_DQM[0]</td><td>E1</td><td>SDRAM Byte Enable 0</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_DQM[1]</td><td>J5</td><td>SDRAM Byte Enable 1</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_CLK</td><td>E5</td><td>SDRAM Clock In</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_CKE</td><td>M5</td><td>SDRAM Clock Enable</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_CAS_N</td><td>M1</td><td>SDRAM Column Address Strobe (N)</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_CS_N</td><td>H1</td><td>SDRAM Chip Select (N)</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_RAS_N</td><td>N2</td><td>SDRAM Row Address Strobe (N)</td><td>3v3</td></tr> | ||

| + | <tr><td>SDRAM_WE_N</td><td>J1</td><td>SDRAM Write Enable (N)</td><td>3v3</td></tr> | ||

</table> | </table> | ||

| − | + | ||

| + | |||

;Datasheet: | ;Datasheet: | ||

*[http://www.issi.com/WW/pdf/42S16320B-86400B.pdf 512Mb SYNCHRONOUS DRAM] | *[http://www.issi.com/WW/pdf/42S16320B-86400B.pdf 512Mb SYNCHRONOUS DRAM] | ||

Edição das 21h42min de 21 de junho de 2016

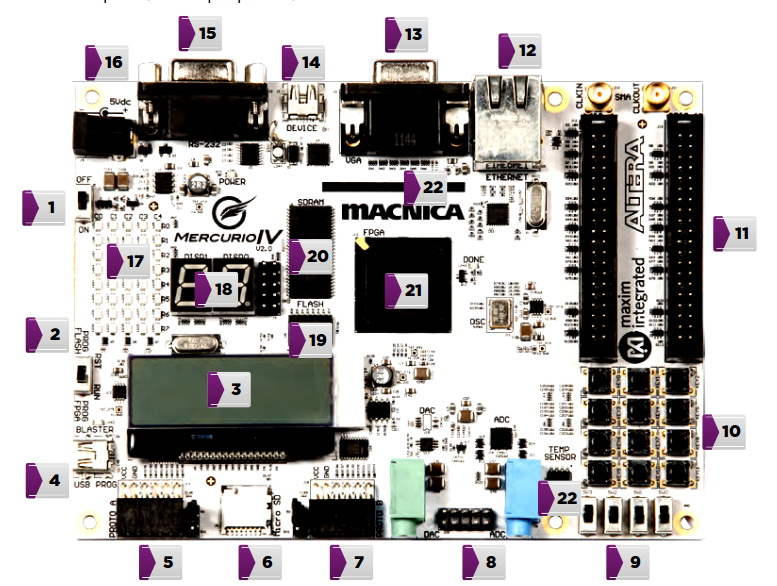

Para encontrar as informações completas sobre o kit Mercurio IV consulte diretamente o Manual do Usuário, [1] e o Diagrama Esquemático, [2] do fabricante. Para facilitar o acesso as informações mais utilizadas nos projetos didáticos, são listadas a seguir alguns dos pinos e sua ligação externa no kit.

O FPGA que equipa a placa Mercurio IV é uma Cyclone IV EP4CE30F23, a qual possui 30 mil elementos lógicos.

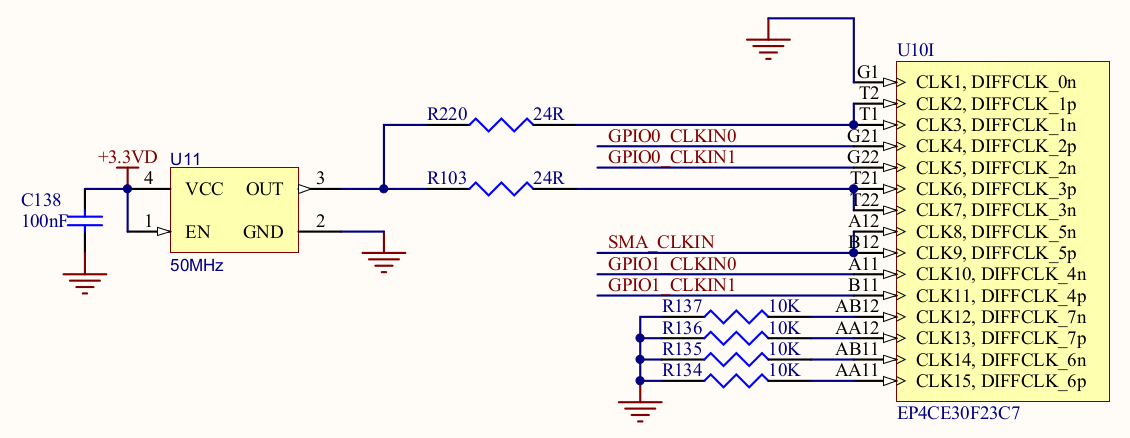

Clock

O clock de entrada do FPGA é de 50 MHz. O sinal de CLOCK_50MHZ está disponível nos pinos T1, T2, T21 e T22 do FPGA. Um clock externo diferente pode ser conectado ao FPGA através do conector SMA (SMA_CLKIN), e da mesma forma um clock internamente gerado por ser conectado o conector SMA (SMA_CLKOUT).

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| CLOCK_50MHz | T1 | 50 MHz clock input | 3.3V |

| CLOCK1_50MHz | T2 | 50 MHz clock input | 3.3V |

| CLOCK2_50MHz | T21 | 50 MHz clock input | 3.3V |

| CLOCK3_50MHz | T22 | 50 MHz clock input | 3.3V |

| SMA_CLKIN | A12 | SMA clock input | 3.3V |

| SMA_CLKIN1 | B12 | SMA clock input | 3.3V |

| SMA_CLKOUT | E6 | SMA clock outpur | 3.3V |

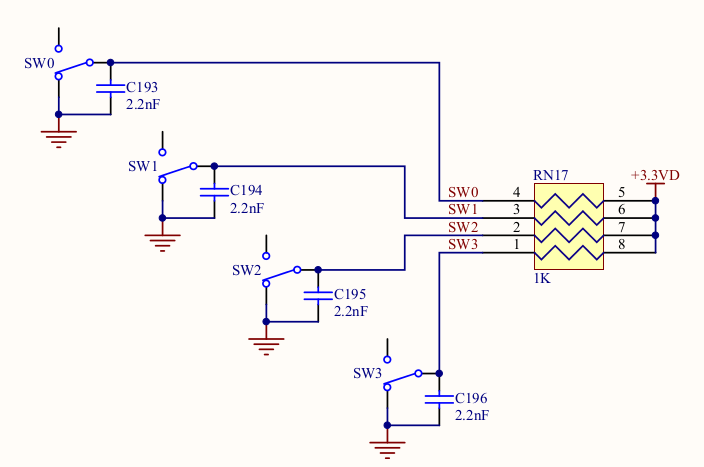

Chaves

A placa Mercurio® IV possui quatro chaves do tipo Slide Switch que são conectadas diretamente ao FPGA. Se a chave estiver posicionada na parte de baixo, o nível lógico na porta do FPGA será ‘0’, se a chave estiver posicionada para cima o nível lógico produzido será ‘1’. Elas estão ligadas a filtros RC, porém, mesmo assim, pode ser interessante implementar um processo de debounce do sinal, a fim de evitar glitches na troca de posição das chaves.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SW[0] | PIN_V21 | Chave tipo Slide Switch 0 | 3.3V |

| SW[1] | PIN_W22 | Chave tipo Slide Switch 1 | 3.3V |

| SW[2] | PIN_W21 | Chave tipo Slide Switch 2 | 3.3V |

| SW[3] | PIN_Y22 | Chave tipo Slide Switch 3 | 3.3V |

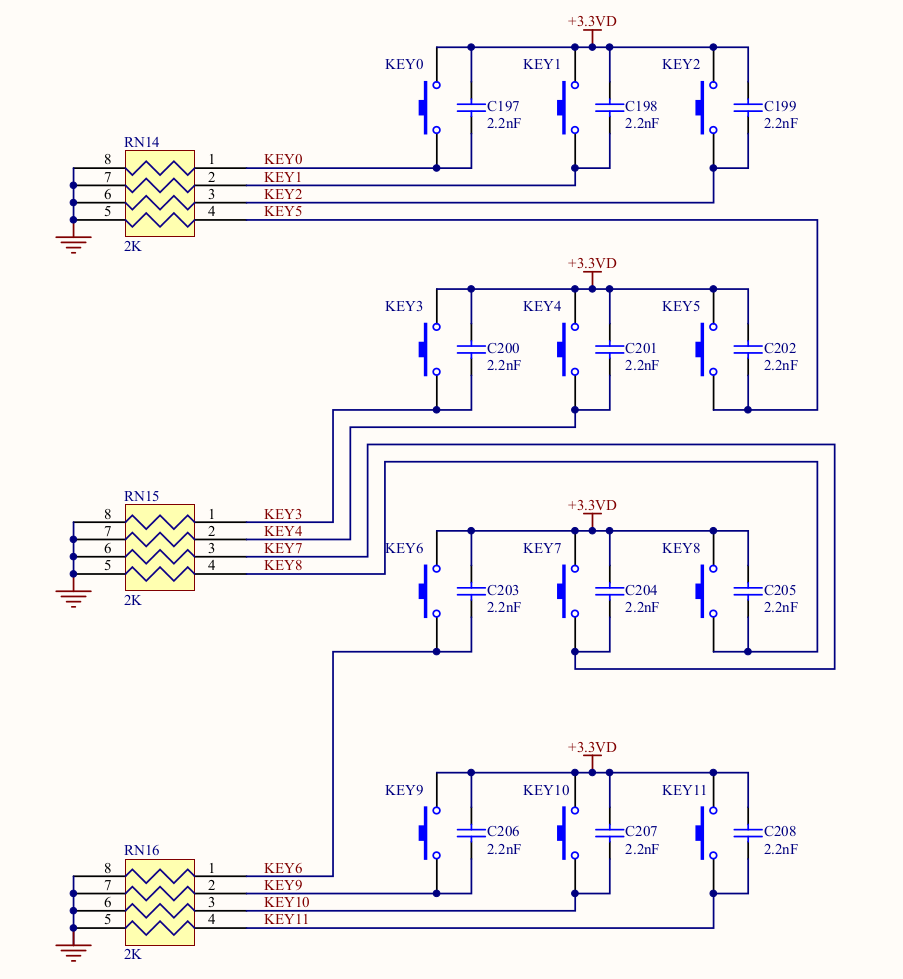

Teclado numérico

Na placa Mercurio IV existe uma organização de 12 botões do tipo push button que estão arranjados de forma a simular um teclado telefônico. Os botões não pressionados geram sinal de nível Lógico baixo na entrada do FPGA, e quando apertados geram um pulso de nível lógico alto.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| KEY[0] | V22 | Botão tipo Push Button 0 | 3.3V |

| KEY[1] | U20 | Botão tipo Push Button 1 | 3.3V |

| KEY[2] | U22 | Botão tipo Push Button 2 | 3.3V |

| KEY[3] | U16 | Botão tipo Push Button 3 | 3.3V |

| KEY[4] | W20 | Botão tipo Push Button 4 | 3.3V |

| KEY[5] | U21 | Botão tipo Push Button 5 | 3.3V |

| KEY[6] | V15 | Botão tipo Push Button 6 | 3.3V |

| KEY[7] | W17 | Botão tipo Push Button 7 | 3.3V |

| KEY[8] | W19 | Botão tipo Push Button 8 | 3.3V |

| KEY[9] | W15 | Botão tipo Push Button 9 | 3.3V |

| KEY[10] | U17 | Botão tipo Push Button 10 | 3.3V |

| KEY[11] | Y17 | Botão tipo Push Button 11 | 3.3V |

Placa de Expansão com 16 chaves

A Mercurio IV é acompanhada de uma placa de expansão com 16 chaves, dispostas em dois grupos de 8. O grupo da esquerda posicionado sobre o conector de GPIO compreede as chaves do grupo A (SA[0..7]), e as da direita as chaves do grupo B (SB[0..7]). Estas chaves estão ligadas a um filtro RC, porém ainda é indicado utilizar processos de eliminação de repique para evitar a introdução de glitches na FPGA. A placa pode ser conectada em uma das interfaces GPIO, porém é recomendado utilizar a interface GPIO0 (o conector "DE DENTRO") para evitar a inversão da placa, o que pode levar a problemas de sobretensão por haver um sinal de 5V no GPIO0.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SA[0] | E16 | Chave tipo Slide Switch 0 | 3.3V |

| SA[1] | H22 | Chave tipo Slide Switch 1 | 3.3V |

| SA[2] | F16 | Chave tipo Slide Switch 2 | 3.3V |

| SA[3] | F19 | Chave tipo Slide Switch 3 | 3.3V |

| SA[4] | H21 | Chave tipo Slide Switch 4 | 3.3V |

| SA[5] | J22 | Chave tipo Slide Switch 5 | 3.3V |

| SA[6] | F20 | Chave tipo Slide Switch 6 | 3.3V |

| SA[7] | H19 | Chave tipo Slide Switch 7 | 3.3V |

| SB[0] | J21 | Chave tipo Slide Switch 0 | 3.3V |

| SB[1] | K21 | Chave tipo Slide Switch 1 | 3.3V |

| SB[2] | H20 | Chave tipo Slide Switch 2 | 3.3V |

| SB[3] | H18 | Chave tipo Slide Switch 3 | 3.3V |

| SB[4] | L22 | Chave tipo Slide Switch 4 | 3.3V |

| SB[5] | L21 | Chave tipo Slide Switch 5 | 3.3V |

| SB[6] | J18 | Chave tipo Slide Switch 6 | 3.3V |

| SB[7] | M21 | Chave tipo Slide Switch 7 | 3.3V |

Matriz de Leds

A matriz de LEDs da placa Mercurio IV é composta por oito linhas e cinco colunas de LEDs, conforme a Figura 13. Cada linha e cada coluna está conectada a um pino do FPGA, portanto, para acender apenas o LED superior esquerdo, por exemplo, é necessário colocar a linha superior e a coluna esquerda em nível baixo, os demais sinais devem permanecer em nível alto (lógica invertida). Ou seja, o acesso à matriz deve ser multiplexado, ou por linhas ou por colunas.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LEDM_C[0] | J7 | Coluna 0 da matriz de LEDs | 3.3V |

| LEDM_C[1] | J6 | Coluna 1 da matriz de LEDs | 3.3V |

| LEDM_C[2] | K8 | Coluna 2 da matriz de LEDs | 3.3V |

| LEDM_C[3] | J8 | Coluna 3 da matriz de LEDs | 3.3V |

| LEDM_C[4] | L8 | Coluna 4 da matriz de LEDs | 3.3V |

| LEDM_R[0] | F10 | Linha 0 da matriz de LEDs | 3.3V |

| LEDM_R[1] | C8 | Linha 1 da matriz de LEDs | 3.3V |

| LEDM_R[2] | E9 | Linha 2 da matriz de LEDs | 3.3V |

| LEDM_R[3] | G9 | Linha 3 da matriz de LEDs | 3.3V |

| LEDM_R[4] | F9 | Linha 4 da matriz de LEDs | 3.3V |

| LEDM_R[5] | F8 | Linha 5 da matriz de LEDs | 3.3V |

| LEDM_R[6] | G8 | Linha 6 da matriz de LEDs | 3.3V |

| LEDM_R[7] | H11 | Linha 7 da matriz de LEDs | 3.3V |

- Datasheet

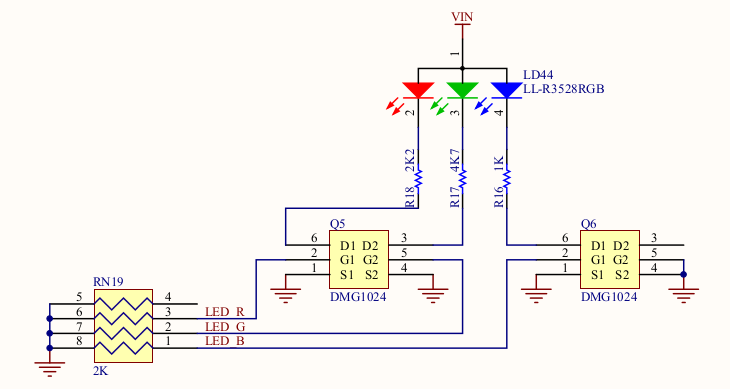

Led RGB

O LED RGB de alto brilho possui três elementos internos, o vermelho, o verde e o azul. Esses três elementos são utilizados para que o LED possa emitir sete cores diferentes:

- Vermelho – elemento R;

- Verde – elemento G;

- Azul – elemento B;

- Amarelo – elementos R e G;

- Ciano – elementos G e B;

- Magenta – elementos R e B;

- Branco – elementos R, G e B.

Cada elemento possui um pino associado, sendo os três elementos conectados ao FPGA e o pino comum é conectado ao VCC. Assim o FPGA pode ativar ou desativar cada elemento do LED RGB colocando ‘0’ no pino associado, sendo possível gerar as sete cores do LED.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| LED_R | D6 | Elemento vermelho do LED RGB | 3.3V |

| LED_G | D7 | Elemento verde do LED RGB | 3.3V |

| LED_B | E7 | Elemento azul do LED RGB | 3.3V |

- Datasheets

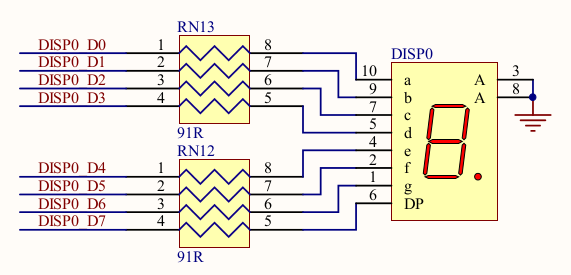

Display de 7 segmentos

Na placa Mercurio IV existem dois displays de 7 segmentos arranjados um ao lado do outro, para ser possível exibir um número com dois algarismos. O display DISP0 fica a direita e o DISP1 a esquerda. Cada display possui um barramento de oito sinais ligado no FPGA, sete sinais para os segmentos e um sinal para o ponto decimal. Os displays são do tipo Anodo Comum, portanto, nível ‘1’ no pino de entrada acende o segmento do display e nível ‘0’ apaga o segmento.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| DISP0_D[0] | V2 | Segmento A - Display 0 | 3.3V |

| DISP0_D[1] | V1 | Segmento B - Display 0 | 3.3V |

| DISP0_D[2] | U2 | Segmento C - Display 0 | 3.3V |

| DISP0_D[3] | U1 | Segmento D - Display 0 | 3.3V |

| DISP0_D[4] | Y2 | Segmento E - Display 0 | 3.3V |

| DISP0_D[5] | Y1 | Segmento F - Display 0 | 3.3V |

| DISP0_D[6] | W2 | Segmento G - Display 0 | 3.3V |

| DISP0_D[7] | W1 | Ponto decimal - Display 0 | 3.3V |

| DISP1_D[0] | R5 | Segmento A - Display 1 | 3.3V |

| DISP1_D[1] | T5 | Segmento B - Display 1 | 3.3V |

| DISP1_D[2] | T3 | Segmento C - Display 1 | 3.3V |

| DISP1_D[3] | T4 | Segmento D - Display 1 | 3.3V |

| DISP1_D[4] | M6 | Segmento E - Display 1 | 3.3V |

| DISP1_D[5] | N7 | Segmento F - Display 1 | 3.3V |

| DISP1_D[6] | N6 | Segmento G - Display 1 | 3.3V |

| DISP1_D[7] | P6 | Ponto decimal - Display 1 | 3.3V |

- Datasheet

SDRAM

A placa Mercurio IV possui um chip de SDRAM de 512Mbits (64 MBytes). As tabelas abaixo apresentam as o timming para configuração do controlador de memória e o roteamento dos pinos para a FPGA da placa. Para integração com o NIOS2, é necessário utilizar um PLL para dar um atraso de 3ns na fase do clock encaminhado ao chip de memória.

| Signal | Name FPGA | Pin No. Description | I/O Standard |

|---|---|---|---|

| SDRAM_A[0] | P2 | SDRAM Address Bit 0 | 3v3 |

| SDRAM_A[1] | R1 | SDRAM Address Bit 1 | 3v3 |

| SDRAM_A[2] | P3 | SDRAM Address Bit 2 | 3v3 |

| SDRAM_A[3] | R2 | SDRAM Address Bit 3 | 3v3 |

| SDRAM_A[4] | P4 | SDRAM Address Bit 4 | 3v3 |

| SDRAM_A[5] | P5 | SDRAM Address Bit 5 | 3v3 |

| SDRAM_A[6] | N5 | SDRAM Address Bit 6 | 3v3 |

| SDRAM_A[7] | M4 | SDRAM Address Bit 7 | 3v3 |

| SDRAM_A[8] | N1 | SDRAM Address Bit 8 | 3v3 |

| SDRAM_A[9] | M2 | SDRAM Address Bit 9 | 3v3 |

| SDRAM_A[10] | P1 | SDRAM Address Bit 10 | 3v3 |

| SDRAM_A[11] | M3 | SDRAM Address Bit 11 | 3v3 |

| SDRAM_A[12] | L6 | SDRAM Address Bit 12 | 3v3 |

| SDRAM_BA[0] | J4 | SDRAM Bank Select Bit 0 | 3v3 |

| SDRAM_BA[1] | H2 | SDRAM Bank Select Bit 1 | 3v3 |

| SDRAM_D[0] | B2 | SDRAM Data Bit 0 | 3v3 |

| SDRAM_D[1] | B1 | SDRAM Data Bit 1 | 3v3 |

| SDRAM_D[2] | C2 | SDRAM Data Bit 2 | 3v3 |

| SDRAM_D[3] | C1 | SDRAM Data Bit 3 | 3v3 |

| SDRAM_D[4] | D2 | SDRAM Data Bit 4 | 3v3 |

| SDRAM_D[5] | E3 | SDRAM Data Bit 5 | 3v3 |

| SDRAM_D[6] | F2 | SDRAM Data Bit 6 | 3v3 |

| SDRAM_D[7] | F1 | SDRAM Data Bit 7 | 3v3 |

| SDRAM_D[8] | J2 | SDRAM Data Bit 8 | 3v3 |

| SDRAM_D[9] | H6 | SDRAM Data Bit 9 | 3v3 |

| SDRAM_D[10] | H5 | SDRAM Data Bit 10 | 3v3 |

| SDRAM_D[11] | J3 | SDRAM Data Bit 11 | 3v3 |

| SDRAM_D[12] | G3 | SDRAM Data Bit 12 | 3v3 |

| SDRAM_D[13] | G4 | SDRAM Data Bit 13 | 3v3 |

| SDRAM_D[14] | G5 | SDRAM Data Bit 14 | 3v3 |

| SDRAM_D[15] | E4 | SDRAM Data Bit 15 | 3v3 |

| SDRAM_DQM[0] | E1 | SDRAM Byte Enable 0 | 3v3 |

| SDRAM_DQM[1] | J5 | SDRAM Byte Enable 1 | 3v3 |

| SDRAM_CLK | E5 | SDRAM Clock In | 3v3 |

| SDRAM_CKE | M5 | SDRAM Clock Enable | 3v3 |

| SDRAM_CAS_N | M1 | SDRAM Column Address Strobe (N) | 3v3 |

| SDRAM_CS_N | H1 | SDRAM Chip Select (N) | 3v3 |

| SDRAM_RAS_N | N2 | SDRAM Row Address Strobe (N) | 3v3 |

| SDRAM_WE_N | J1 | SDRAM Write Enable (N) | 3v3 |

- Datasheet

ADC

DAC

Display de 7 segmentos

Na placa Mercurio IV existe um chip SDRAM de 512Mbits conectado à FPGA. O modelo do chip SDRAM é IS42S16320B (ISSI). Ele possui quatro bancos de memória, sendo que cada um possui 8 M x 16 bits. Cada banco é estruturado em 8192 linhas (13 bits para enumerar) e 1024 colunas (10 bits para enumerar).