Mudanças entre as edições de "ELD129003-Engtelecom (Diário) - Prof. Marcos Moecke"

(→ATUAL) |

(→ATUAL) |

||

| (4 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 448: | Linha 448: | ||

* 8 ENCONTROS | * 8 ENCONTROS | ||

{{collapse top | expand=true | Unidade 3 - Circuitos sequenciais (Implementação com HDL)}} | {{collapse top | expand=true | Unidade 3 - Circuitos sequenciais (Implementação com HDL)}} | ||

| − | |||

;Encontro 8 (12 mar): | ;Encontro 8 (12 mar): | ||

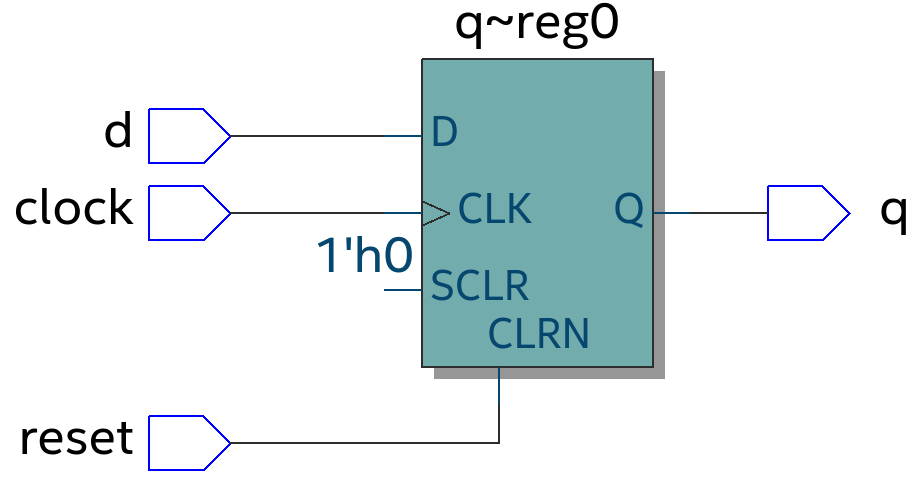

*Flip-Flop e circuitos sequenciais. | *Flip-Flop e circuitos sequenciais. | ||

| Linha 513: | Linha 512: | ||

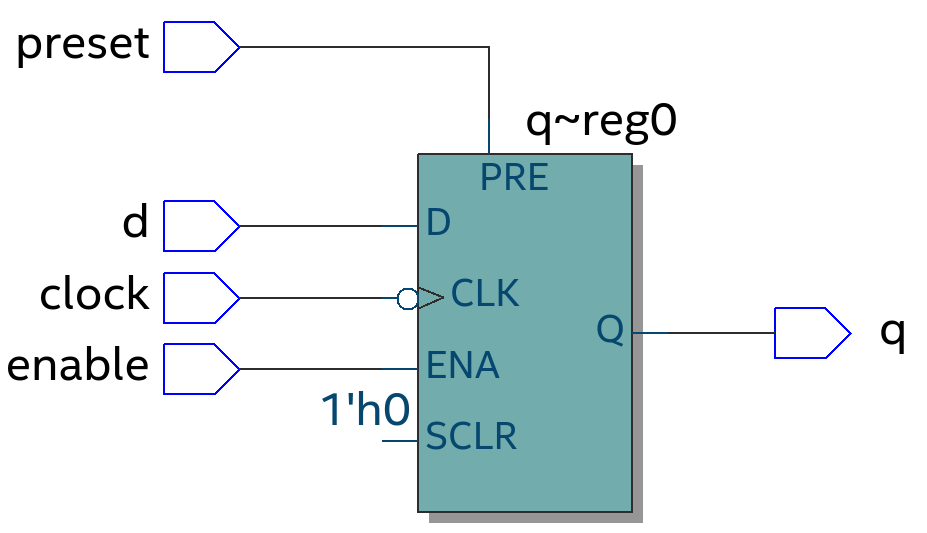

{{fig|5.2|RTL de Flip-flop D de borda de descida, com preset assíncrono e enable| FF_D_PRST.png| 400 px | }} | {{fig|5.2|RTL de Flip-flop D de borda de descida, com preset assíncrono e enable| FF_D_PRST.png| 400 px | }} | ||

| − | |||

;Encontro 9 (15 mar): | ;Encontro 9 (15 mar): | ||

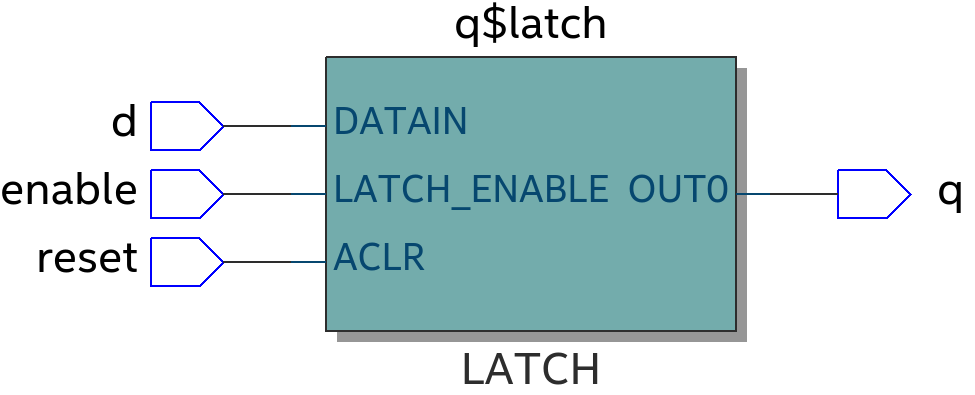

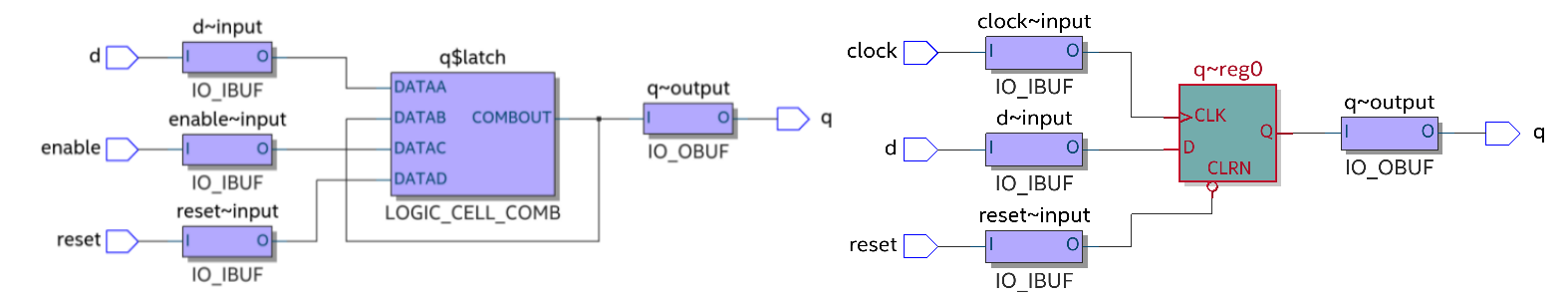

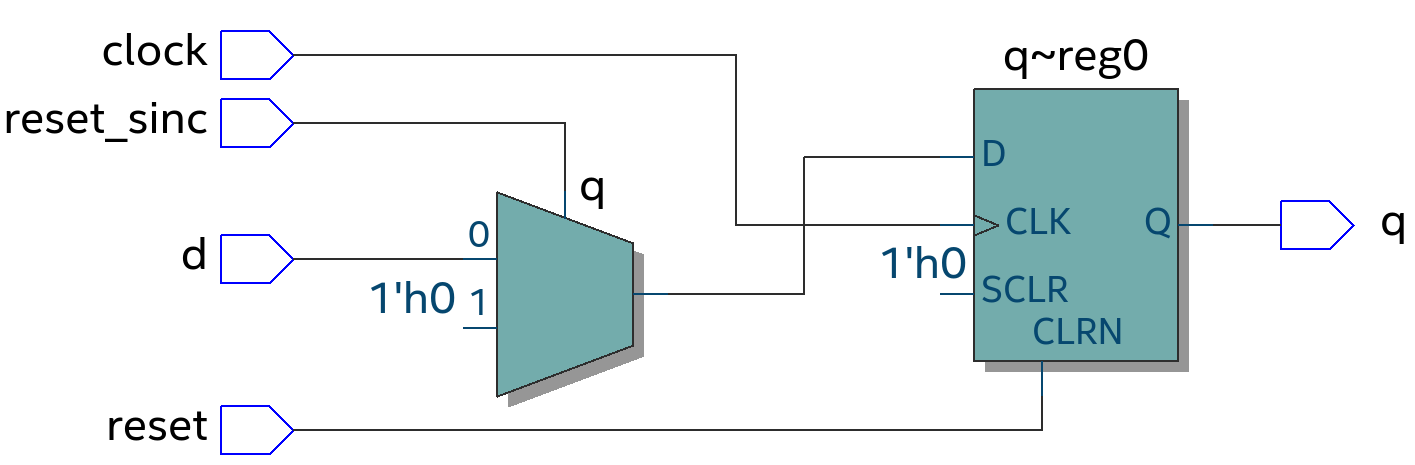

::* Comparar com Latch (sem clk'event). | ::* Comparar com Latch (sem clk'event). | ||

| Linha 557: | Linha 555: | ||

* Faça a simulação funcional do DFFs e do Latch | * Faça a simulação funcional do DFFs e do Latch | ||

| + | ====ATUAL==== | ||

| + | ;Encontro 10 (22 mar): | ||

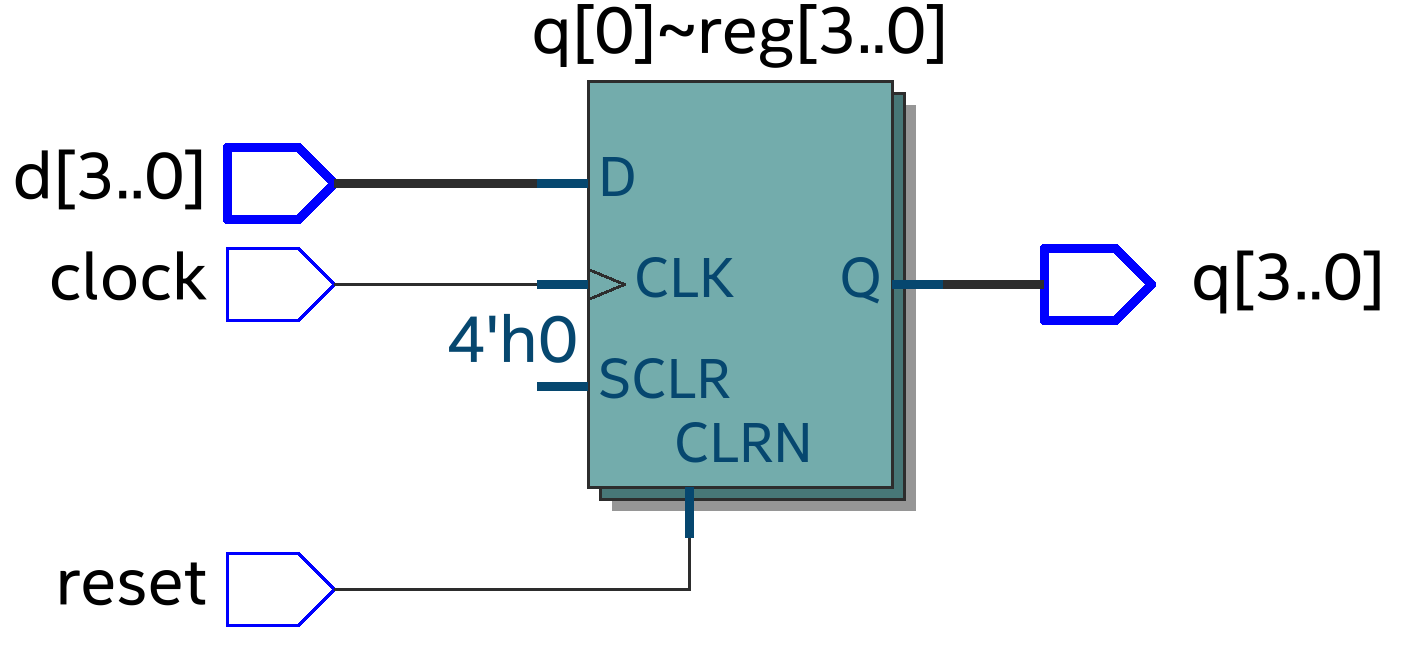

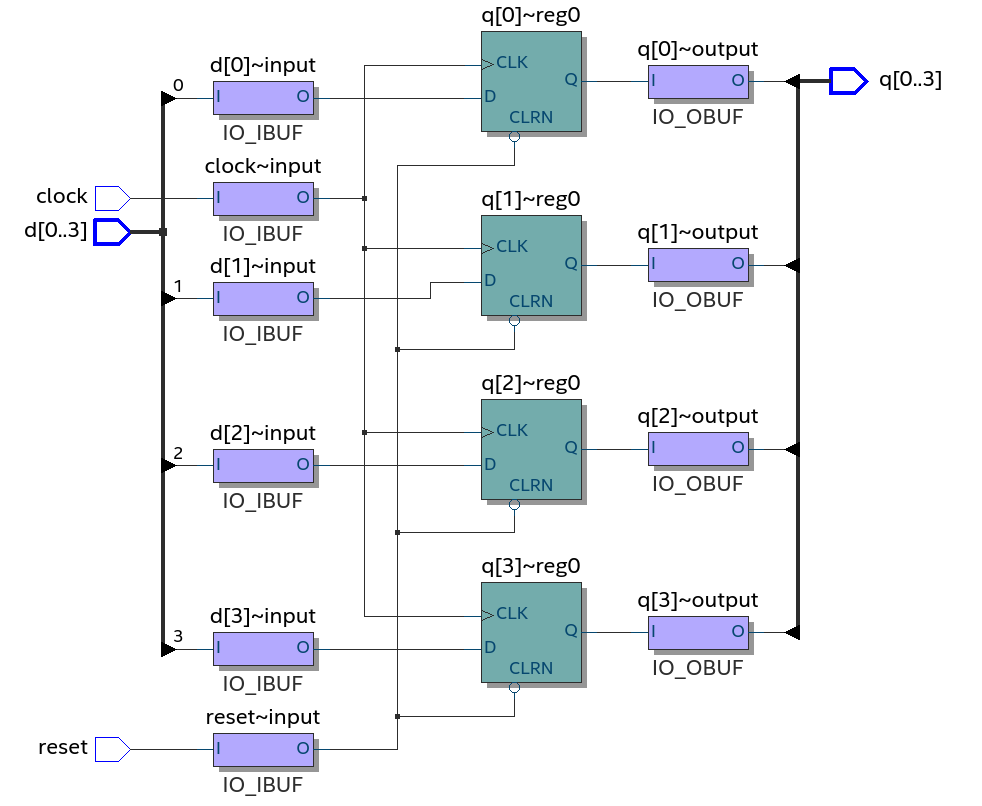

| + | *Implementar um registrador com N FF_D usando a instrução '''FOR GENERATE'''. | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Instrução concorrente FOR GENERATE. | ||

| + | -- Note que neste caso o '''label''' é obrigatório | ||

| + | |||

| + | label: FOR identificador IN faixa GENERATE | ||

| + | [Parte_Declarativa | ||

| + | BEGIN] | ||

| + | Instruções_concorrentes | ||

| + | ... | ||

| + | END GENERATE [label]; | ||

| + | </syntaxhighlight> | ||

| + | |||

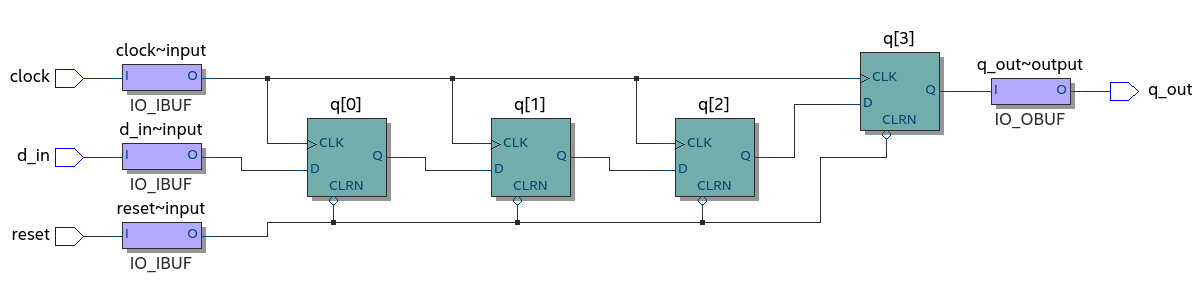

| + | *Implementar um registrador de deslocamento de N bits. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity shift_reg is | ||

| + | generic ( N : natural := 4); | ||

| + | port ( | ||

| + | clock, reset : in std_LOGIC ; | ||

| + | d_in: in std_LOGIC; | ||

| + | q_out : out std_LOGIC); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of shift_reg is | ||

| + | signal d: std_logic_vector(N-1 downto 0); | ||

| + | signal q: std_logic_vector(N-1 downto 0); | ||

| + | begin | ||

| + | ... | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | {{fig|5.8|Technology Map de Shift Register| shift_reg_TM.png| 800 px | }} | ||

| + | {{fig|5.9|Simulação de Shift Register| shift_reg_SIM.png| 800 px | }} | ||

| + | |||

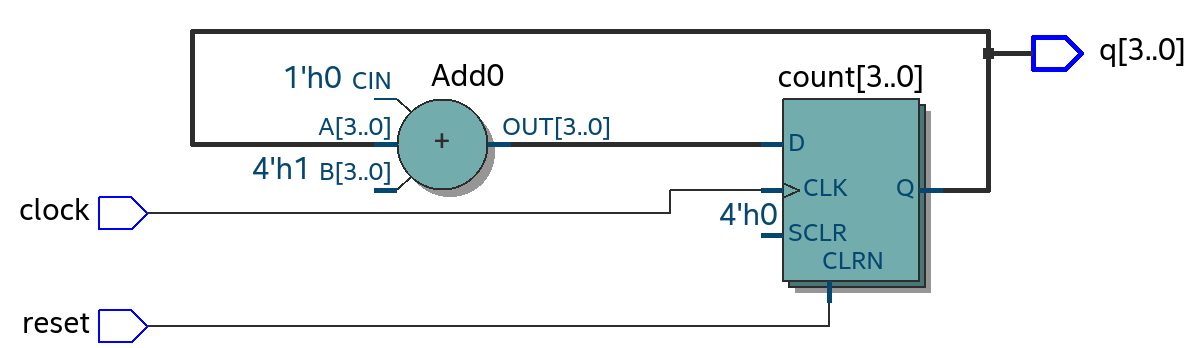

| + | *Implementar um contador crescente 0-N (baseado no Ex.6.2), com N = 2^Mbits-1 (1 3 7 15) | ||

| + | :*Com overflow no valor máximo | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity conta_0_N is | ||

| + | generic (MAX : natural := 15); | ||

| + | port (clock, reset: in std_logic; q : out integer range 0 to MAX); | ||

| + | end entity; | ||

| + | |||

| + | architecture ifsc_v1 of conta_0_N is | ||

| + | |||

| + | begin | ||

| + | process (clock,reset) | ||

| + | variable count : integer range 0 to MAX; | ||

| + | begin | ||

| + | if (reset = '1') then | ||

| + | count := 0; | ||

| + | elsif (rising_edge(clock)) then | ||

| + | count := count + 1; | ||

| + | end if; | ||

| + | q <= count; | ||

| + | end process; | ||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | {{fig|5.10|RTL de contador crescente| Counter_0_M_RTL.png| 600 px | }} | ||

| + | {{fig|5.11|Simulação de contador crescente| Counter_0_M_SIM.png| 600 px | }} | ||

| + | |||

| + | <!-- | ||

| + | *Implementar um contador crescente 0-N (baseado no Ex.6.2), com N =/= 2^Mbits (5, 10) | ||

| + | :*Com overflow no valor máximo | ||

| + | :*Com parada no valor máximo | ||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição das 11h48min de 22 de março de 2024

Registro on-line das aulas

Unidade 1 - Aula inicial, Introdução a disciplina

- 1 ENCONTRO

| Unidade 1 - Aula inicial, Introdução a disciplina |

|---|

|

Unidade REV - PRIMEIRO CONTATO COM VHDL

- 3 ENCONTROS

| Unidade REV - PRIMEIRO CONTATO COM VHDL | ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

Para ilustrar essas instruções utilizaremos o exemplo de um Mux4x1. Um multiplexador digital de N entradas e 1 saída, frequentemente abreviado como MUX N:1, é um circuito digital muito utilizado para rotear sinais digitais. Ele desempenha a função de selecionar uma das entradas para ser encaminhada para a saída com base em um sinal de seleção (ou controle).

Dada a função booleana do MUX4:1 é simples para descreve-lo em VHDL utilizando apenas operadores lógicos. entity mux4x1 is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

Sel : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity;

-- Implementação com lógica pura

architecture v_logica_pura of mux4x1 is

begin

Y <= (X(0) and (not Sel(1)) and (not Sel(0))) or

...

end architecture;

No entanto, o MUX4:1 também pode ser descrito utilizando a instrução WHEN-ELSE <optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

...

<value> else

<value>;

Warning (13012): Latch ... has unsafe behavior

No caso do MUX4:1 ele poderia ser descrito como: -- Implementação com WHEN ELSE

architecture v_WHEN_ELSE of mux4x1 is

begin

Y <= X(0) when Sel = "00" else

X(1) when Sel = "01" else

X(2) when Sel = "10" else

X(3);

end architecture;

Outra forma de descrever o MUX4:1 seria utilizando a instrução WITH-SELECT <optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

Error (10313): VHDL Case Statement error ...: Case Statement choices must cover all possible values of expression

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux4x1 is

begin

with Sel select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture;

CONFIGURATION <configuration_name> OF <entity_name> IS

FOR <architecture_name> END FOR;

END CONFIGURATION;

-- Design Unit que associa a architecture com a entity

CONFIGURATION cfg_ifsc OF mux4x1 IS

FOR v_logica_pura END FOR;

-- FOR v_WHEN_ELSE END FOR;

-- FOR v_WITH_SELECT END FOR;

END CONFIGURATION;

Figura 2.1 - Código RTL do mux4x1 v_logica_pura  Figura 2.2 - Código RTL do mux4x1 v_WHEN_ELSE  Figura 2.3 - Código RTL do mux4x1 v_WITH_SELECT

| ||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

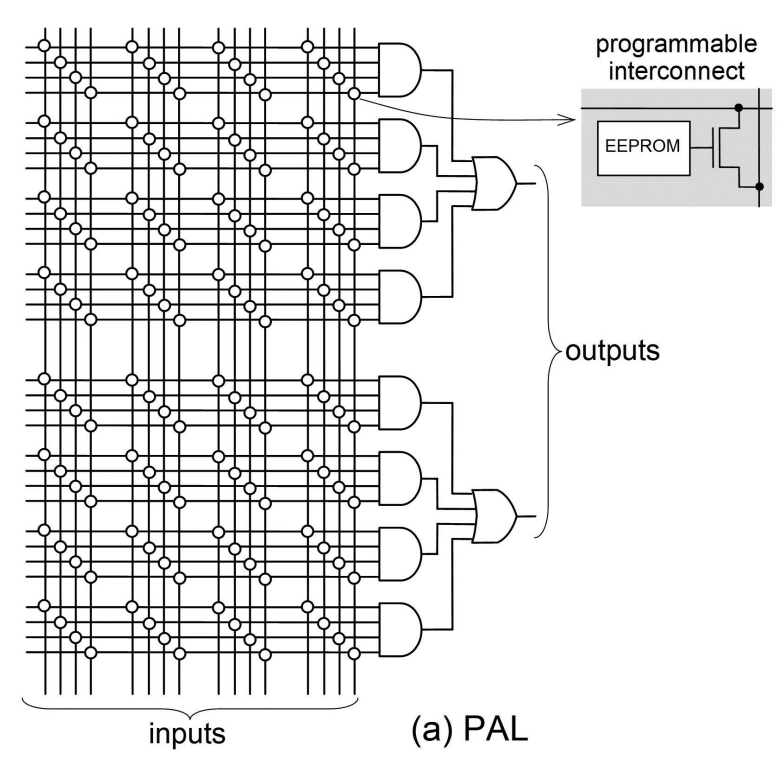

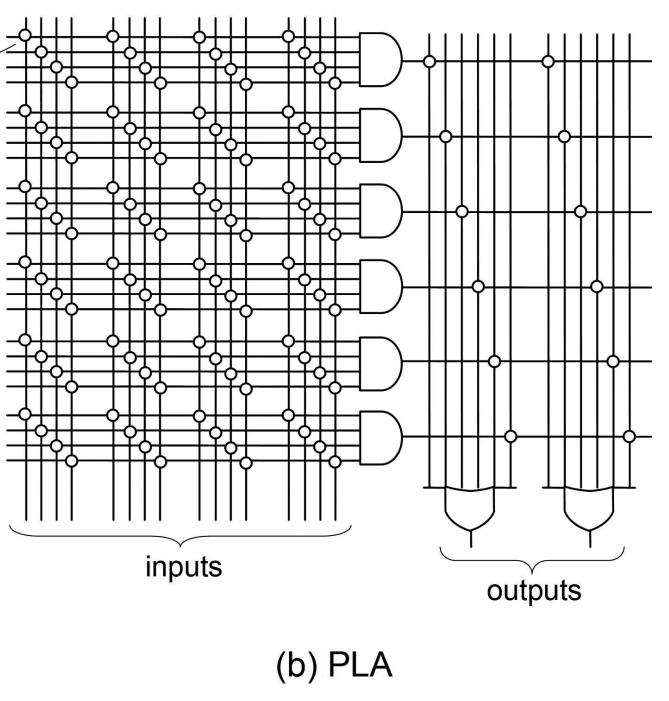

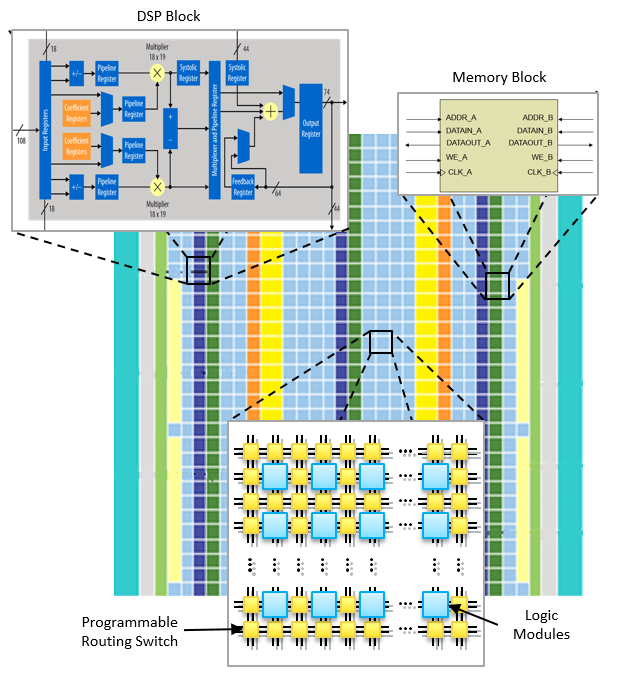

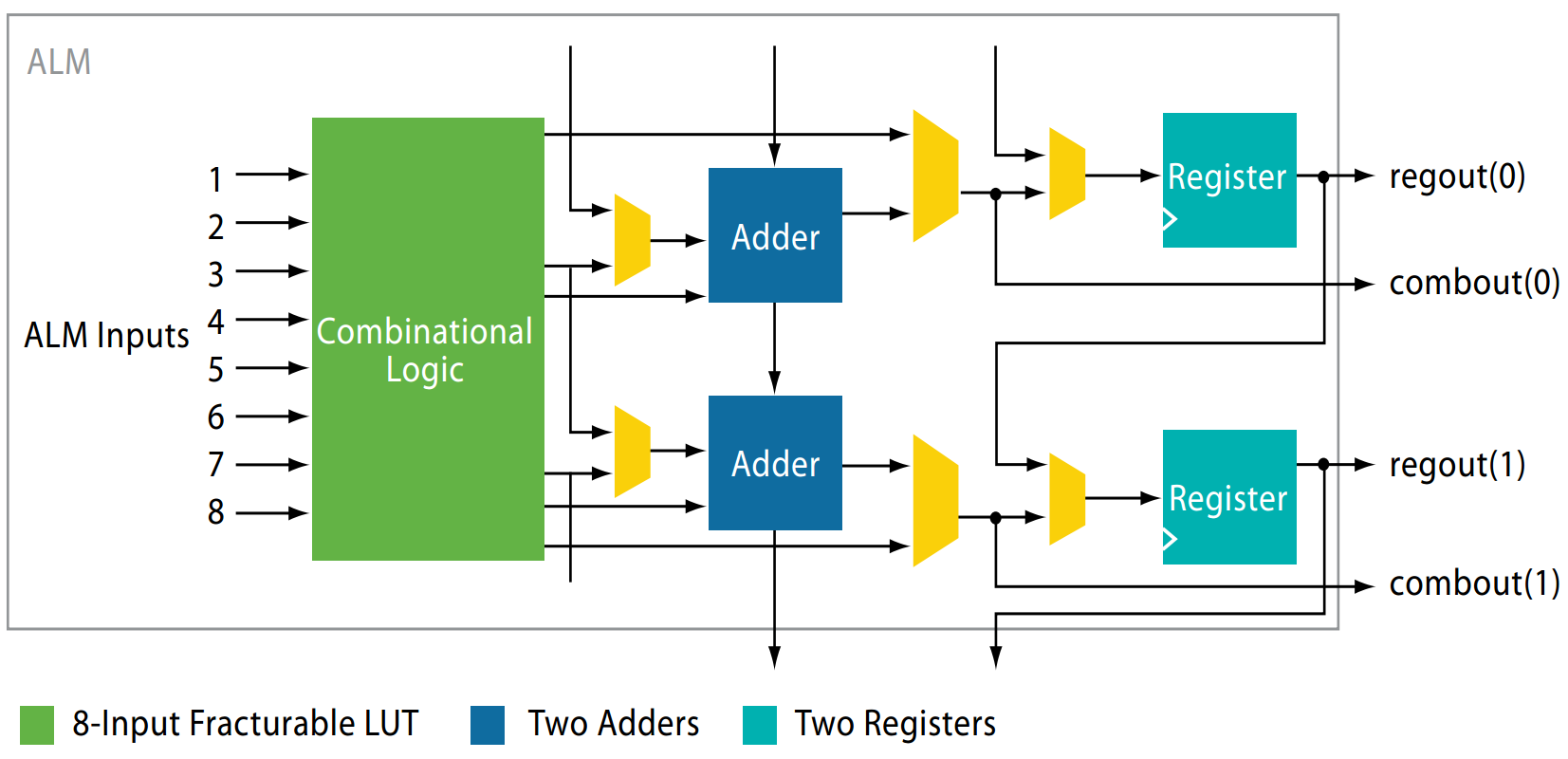

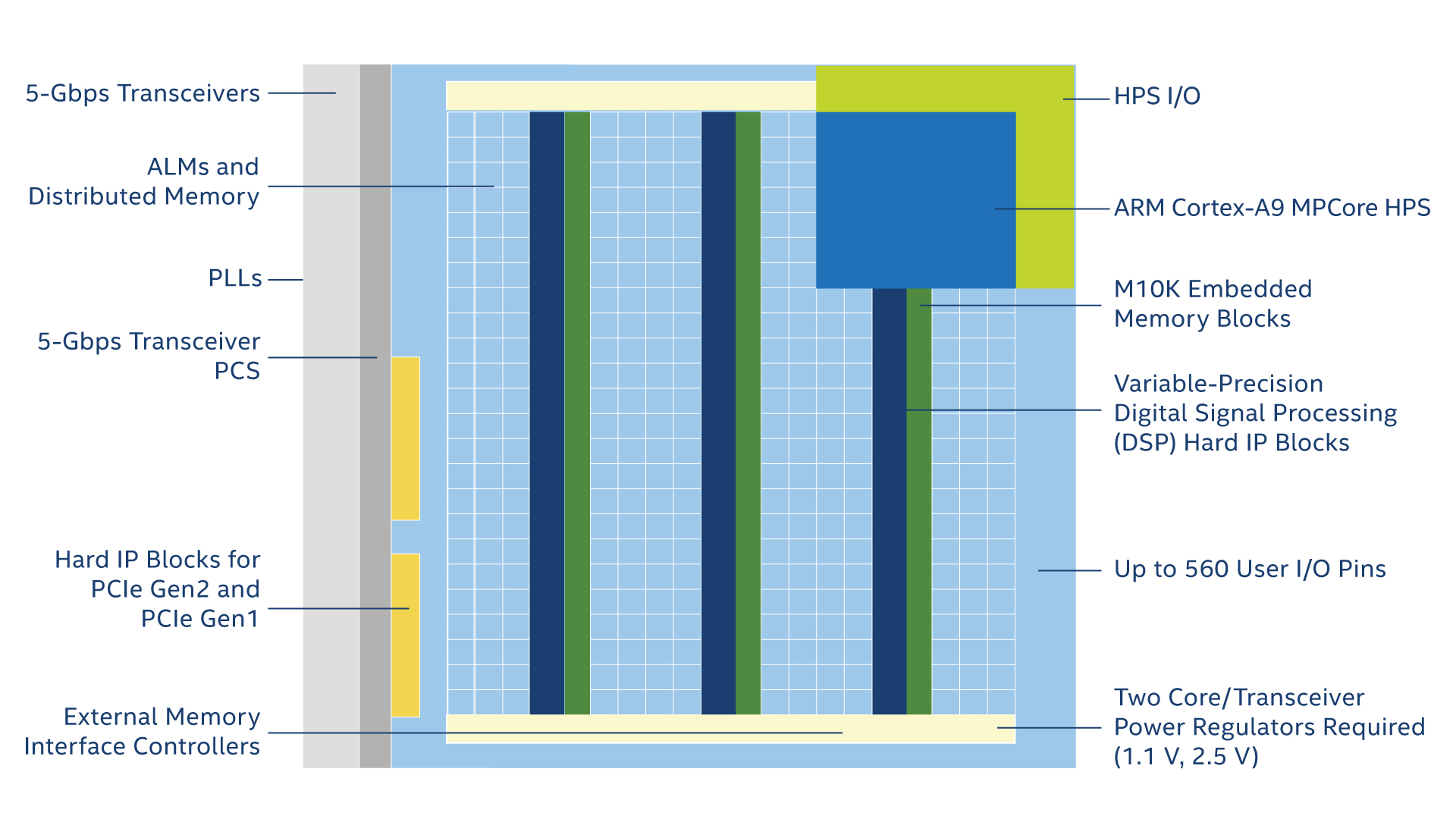

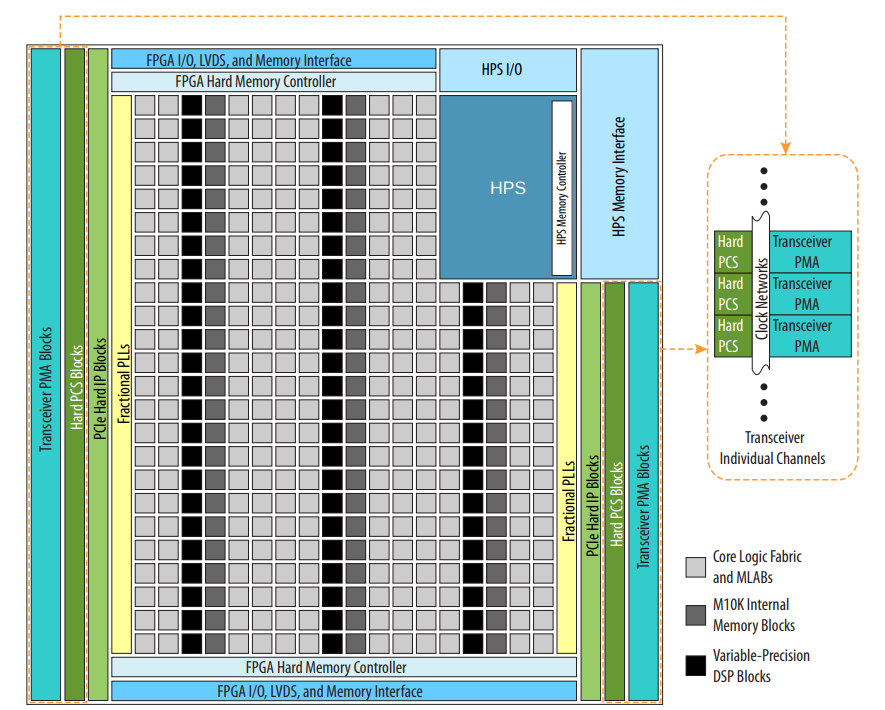

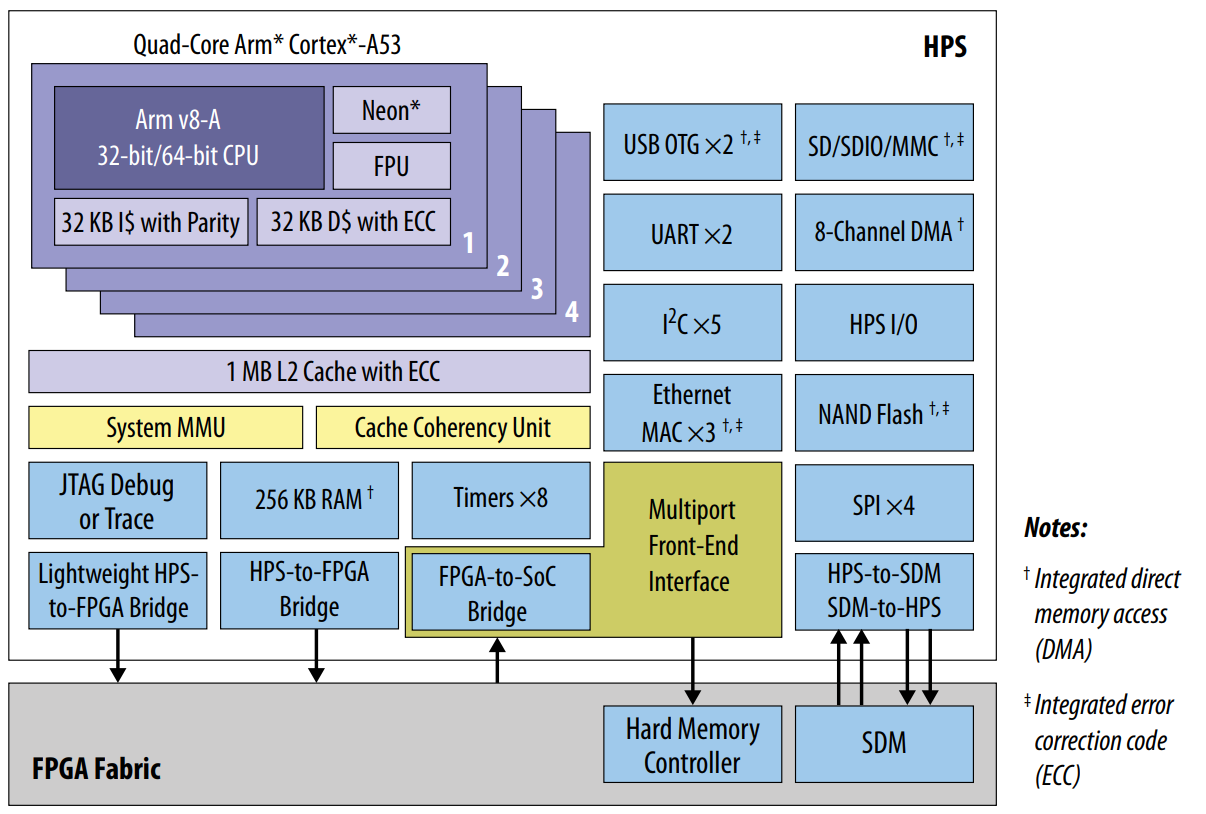

Unidade 2 - Dispositivos Lógicos Programáveis

- 3 ENCONTROS

| Unidade 2 - Dispositivos Lógicos Programáveis | ||

|---|---|---|

Unidade 3 - Circuitos sequenciais (Implementação com HDL)

|

- ↑ Erro de citação: Marca

<ref>inválida; não foi fornecido texto para as refs chamadasPEDRONI2010b