Mudanças entre as edições de "DLP29007-Engtelecom(2017-2) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| (3 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 284: | Linha 284: | ||

==Unidade 8== | ==Unidade 8== | ||

;Aula 24 (21 Nov): | ;Aula 24 (21 Nov): | ||

| − | *Projeto Hierárquico | + | *Projeto Hierárquico ([https://www.dropbox.com/s/wts1ai0ltlg27p9/DLP29007%20-%20Projeto%20Hierarquico%20Parametrizado%20v2.pdf?dl=0 Slides - Projeto Hierárquico e Parametrizado]) |

:* COMPONENTS (declaração e instanciação). Mapeamento dos nomes das portas por nome X posição | :* COMPONENTS (declaração e instanciação). Mapeamento dos nomes das portas por nome X posição | ||

:* GENERIC | :* GENERIC | ||

| Linha 290: | Linha 290: | ||

:* Subprogramas (FUNCTION e PROCEDURE) | :* Subprogramas (FUNCTION e PROCEDURE) | ||

:* LIBRARY e PACKAGE | :* LIBRARY e PACKAGE | ||

| − | :* PARTITION (fisica e lógica) | + | :* PARTITION (fisica e lógica) ver como usar em: |

::*[http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm Using the Design Partition Planner], | ::*[http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm Using the Design Partition Planner], | ||

| − | + | ||

| − | |||

| − | |||

| − | |||

| − | |||

<center> | <center> | ||

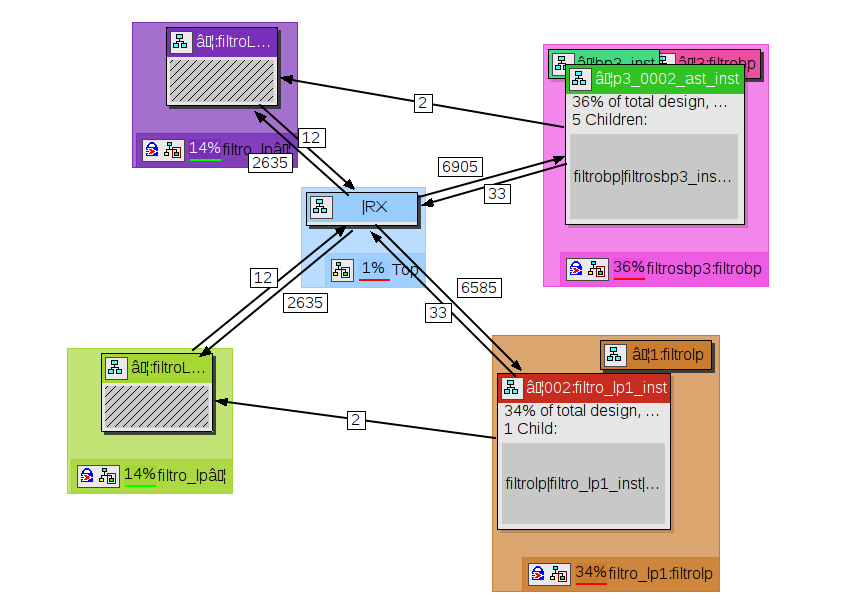

Exemplo de sistema particionado visto no Design Partition Planner | Exemplo de sistema particionado visto no Design Partition Planner | ||

| Linha 303: | Linha 299: | ||

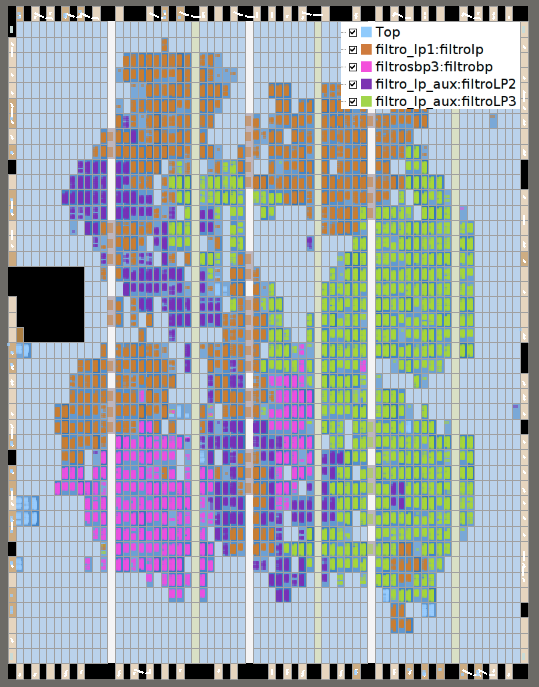

:[[Arquivo:ChipPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner - Chip Planner | 400 px]] | :[[Arquivo:ChipPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner - Chip Planner | 400 px]] | ||

</center> | </center> | ||

| − | *[https://www. | + | :* Adicionalmente consulte mais detalhes sobre compilação incremental e particionamento em: |

| − | + | ::*[http://quartushelp.altera.com/15.0/mergedProjects/comp/increment/comp_view_qid.htm About Incremental Compilation], | |

| − | ::Ver pag. 473 a 498 de <ref name="PONG2006a" /> | + | ::*[https://www.altera.com/en_US/pdfs/literature/an/an567.pdf AN 567: Quartus II Design Separation Flow], |

| + | ::*[https://www.altera.com/en_US/pdfs/literature/wp/wp-01062-quartus-ii-increasing-productivity-incremental-compilation.pdf Increasing Productivity With Quartus II Incremental Compilation], | ||

| + | ::*[https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/qts/qts_qii5v1.pdf Quartus II Handbook Volume 1: Design and Synthesis], | ||

| + | ::*[https://www.altera.com/en_US/pdfs/literature/hb/qts/qts_qii51015.pdf Quartus II Incremental Compilation for Hierarchical and Team-Based Design], | ||

| + | ::*[https://www.altera.co.jp/ja_JP/pdfs/literature/hb/qts/qts_qii51017.pdf Best Practices for Incremental Compilation Partitions and Floorplan Assignments]) | ||

| + | ::*Ver pag. 473 a 498 de <ref name="PONG2006a" /> | ||

| − | |||

;Aula 25 (27 Nov): | ;Aula 25 (27 Nov): | ||

*Projeto Parametrizado | *Projeto Parametrizado | ||

| Linha 328: | Linha 328: | ||

::*Exemplo L14.16 (up_or_down) X L14.17 (up_and_down) X L14.20 (up + down) | ::*Exemplo L14.16 (up_or_down) X L14.17 (up_and_down) X L14.20 (up + down) | ||

::Ver pag. 499 a 543 de <ref name="PONG2006a" /> | ::Ver pag. 499 a 543 de <ref name="PONG2006a" /> | ||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

Edição atual tal como às 12h13min de 27 de novembro de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

| Unidade 1 - Processo de Síntese do código VDHL |

|---|

Unidade 1

|

| Unidade 3 - Eficiência de Circuitos Combinacionais |

|---|

Unidade 3

|

| Unidade 4 - Eficiência de Circuitos Sequenciais | ||

|---|---|---|

Unidade 4

--Por exemplo em um contador de 0 a 9 use um CLEAR síncrono

r_next <= (others => '0') when r_reg = 9 else r_reg + 1;

--Em um contador

r_next <= r_reg + 1 when ena = '1' else r_reg;

-- Não use multiplos clocks

elsif (clk'event and clk='1') then

...

elsif (sclk'event and sclk='1') then

...

elsif (mclk'event and mclk='1') then

...

-- Use um único clock com vários enables.

elsif (clk'event and clk='1') then

...

s_next <= (others=>'0') when (s_reg=59 and s_en='1') else

s_reg + 1 when s_en='1' else

s_reg;

...

m_next <= (others=>'0') when (m_reg=59 and m_en='1') else

m_reg + 1 when m_en='1' else

m_reg;

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 0000 ...

0001 0010 0100 1000 0001 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000 ...

0001 1000 0100 0010 1001 1100 0110 1011 0101 1010 1101 1110 1111 0111 0011 0001 ...

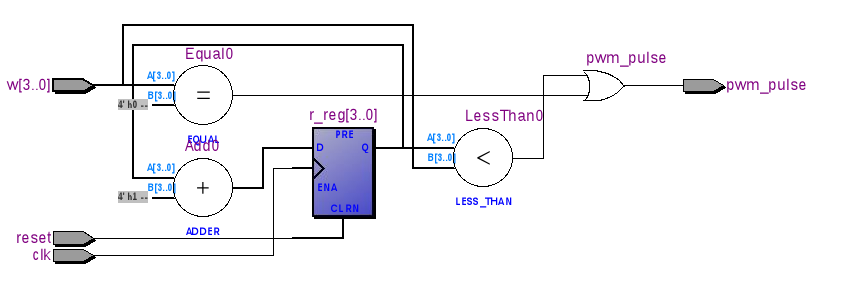

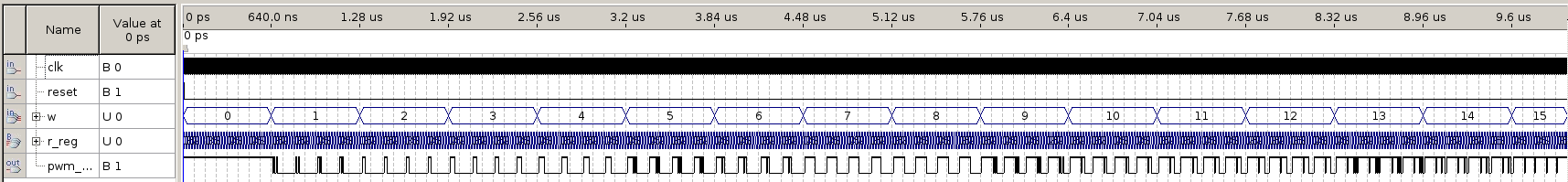

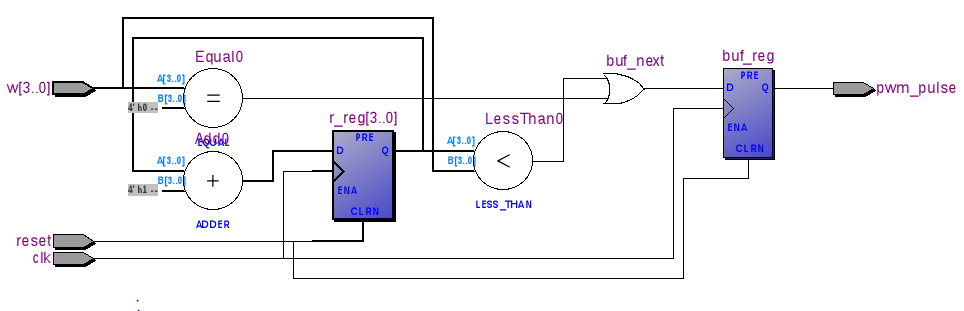

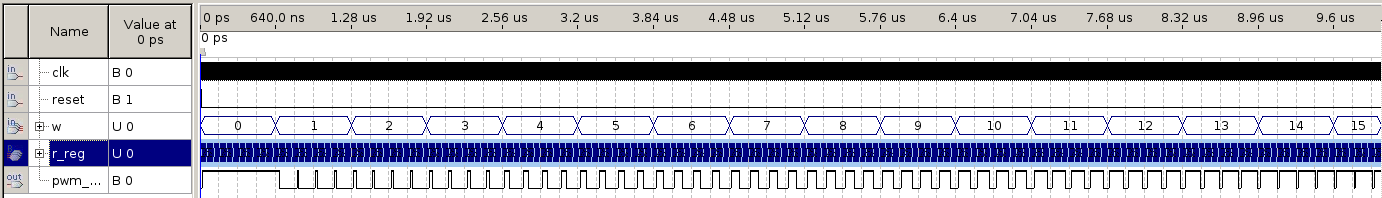

Figura 4.1 - PWM sem buffer de saída - tem gliches na saída. Figura 4.2 - PWM com buffer de saída - não tem gliches na saída.

|

| Unidade 8 - Projeto Hierarquico e Parametrizado |

|---|

Unidade 8

Exemplo de sistema particionado visto no Design Partition Planner Exemplo de sistema acima visto no Chip Planner (CICLONE IV E)

a = (a'range => '1')

gen_label: if <boolean_exp> generate

-- expressões concorrentes

end generate;

|

Referências Bibliográficas: