Mudanças entre as edições de "DLP29007-Engtelecom(2017-2) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 291: | Linha 291: | ||

:* LIBRARY e PACKAGE | :* LIBRARY e PACKAGE | ||

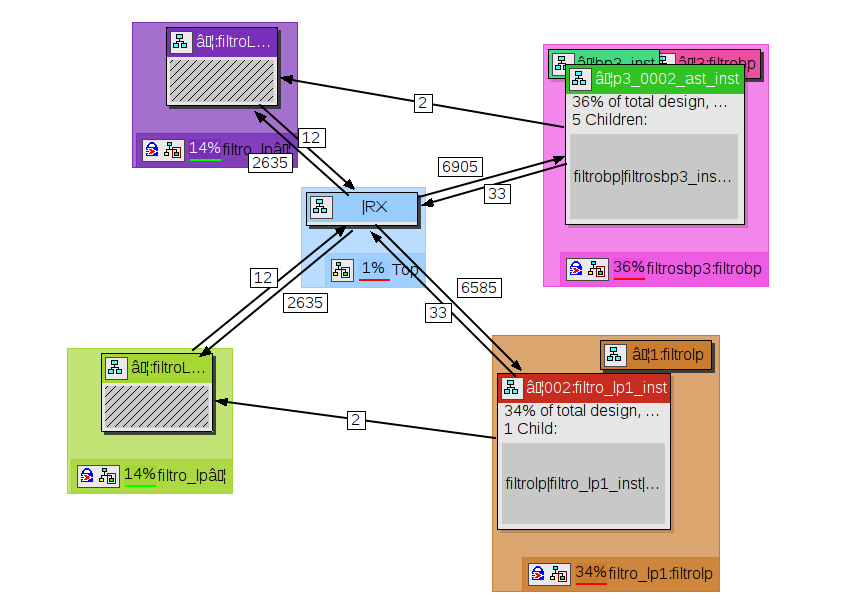

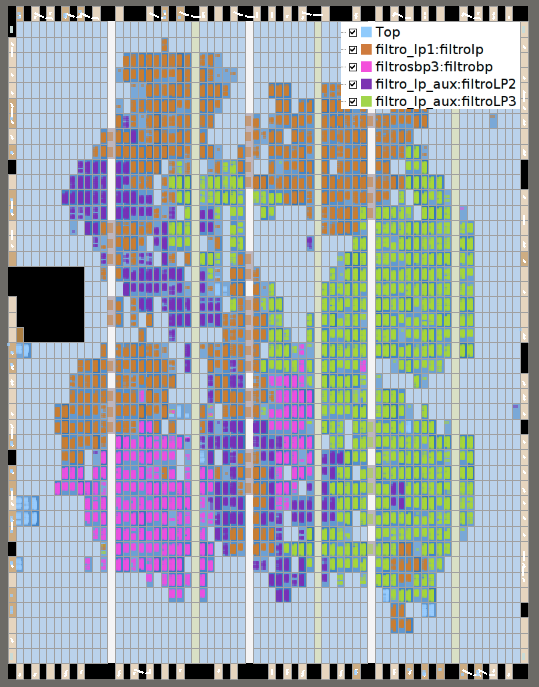

:* PARTITION (fisica e lógica) consultar ([http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm], [https://www.altera.com/en_US/pdfs/literature/an/an567.pdf], [https://www.altera.com/en_US/pdfs/literature/wp/wp-01062-quartus-ii-increasing-productivity-incremental-compilation.pdf], [https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/qts/qts_qii5v1.pdf]) | :* PARTITION (fisica e lógica) consultar ([http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm], [https://www.altera.com/en_US/pdfs/literature/an/an567.pdf], [https://www.altera.com/en_US/pdfs/literature/wp/wp-01062-quartus-ii-increasing-productivity-incremental-compilation.pdf], [https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/qts/qts_qii5v1.pdf]) | ||

| + | :[[Arquivo:DesignPartitionPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner]] | ||

| + | :[[Arquivo:ChipPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner - Chip Planner]] | ||

| + | |||

*[https://www.dropbox.com/s/wts1ai0ltlg27p9/DLP29007%20-%20Projeto%20Hierarquico%20Parametrizado%20v2.pdf?dl=0 Projeto Hierárquico e Parametrizado], | *[https://www.dropbox.com/s/wts1ai0ltlg27p9/DLP29007%20-%20Projeto%20Hierarquico%20Parametrizado%20v2.pdf?dl=0 Projeto Hierárquico e Parametrizado], | ||

| + | |||

::Ver pag. 473 a 498 de <ref name="PONG2006a" /> | ::Ver pag. 473 a 498 de <ref name="PONG2006a" /> | ||

Edição das 18h32min de 21 de novembro de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

| Unidade 1 - Processo de Síntese do código VDHL |

|---|

Unidade 1

|

| Unidade 3 - Eficiência de Circuitos Combinacionais |

|---|

Unidade 3

|

| Unidade 4 - Eficiência de Circuitos Sequenciais | ||

|---|---|---|

Unidade 4

--Por exemplo em um contador de 0 a 9 use um CLEAR síncrono

r_next <= (others => '0') when r_reg = 9 else r_reg + 1;

--Em um contador

r_next <= r_reg + 1 when ena = '1' else r_reg;

-- Não use multiplos clocks

elsif (clk'event and clk='1') then

...

elsif (sclk'event and sclk='1') then

...

elsif (mclk'event and mclk='1') then

...

-- Use um único clock com vários enables.

elsif (clk'event and clk='1') then

...

s_next <= (others=>'0') when (s_reg=59 and s_en='1') else

s_reg + 1 when s_en='1' else

s_reg;

...

m_next <= (others=>'0') when (m_reg=59 and m_en='1') else

m_reg + 1 when m_en='1' else

m_reg;

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 0000 ...

0001 0010 0100 1000 0001 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000 ...

0001 1000 0100 0010 1001 1100 0110 1011 0101 1010 1101 1110 1111 0111 0011 0001 ...

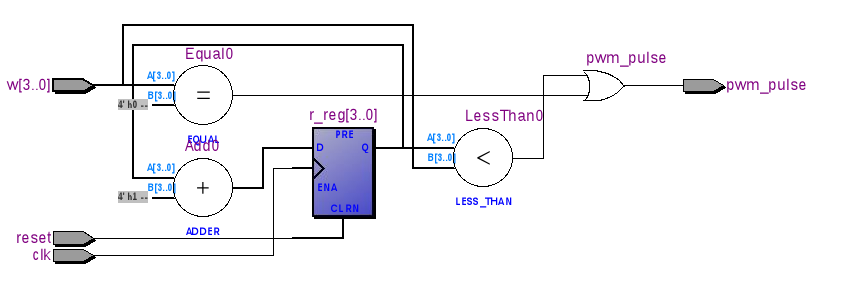

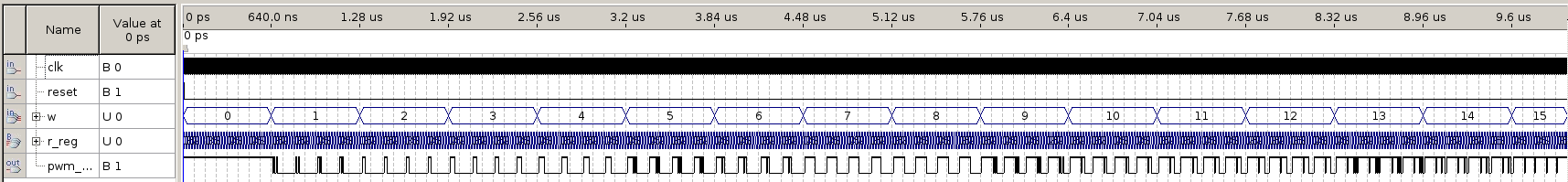

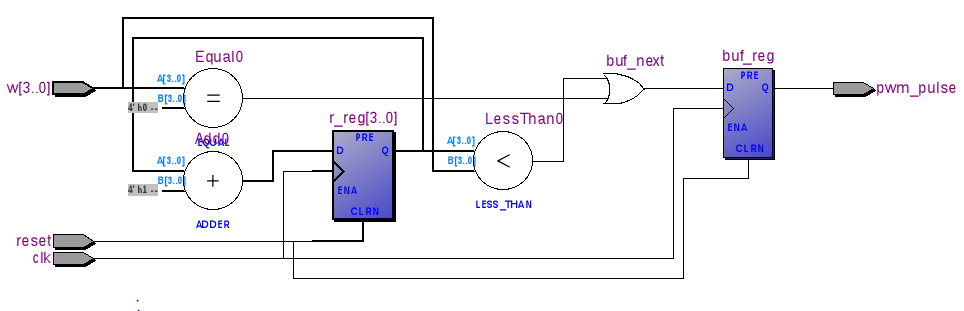

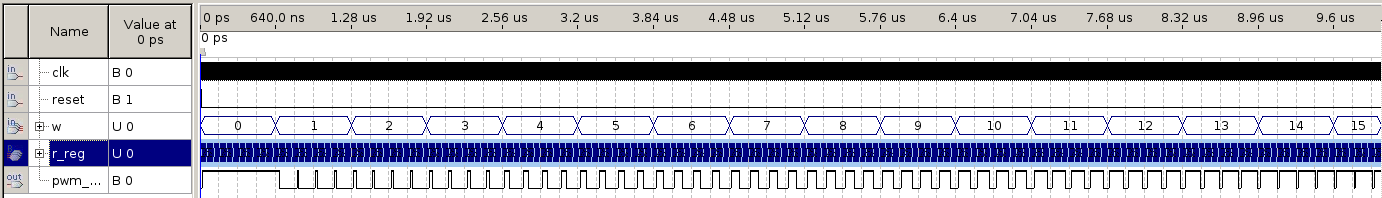

Figura 4.1 - PWM sem buffer de saída - tem gliches na saída. Figura 4.2 - PWM com buffer de saída - não tem gliches na saída.

|

| Unidade 8 - Projeto Hierarquico e Parametrizado |

|---|

Unidade 8

|

Referências Bibliográficas: