Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 454: | Linha 454: | ||

===AE2 - Conhecendo os dispositivos lógicos programáveis=== | ===AE2 - Conhecendo os dispositivos lógicos programáveis=== | ||

{{collapse top | bg=lightyellow | AE2 - Conhecendo os dispositivos lógicos programáveis}} | {{collapse top | bg=lightyellow | AE2 - Conhecendo os dispositivos lógicos programáveis}} | ||

| + | ;Objetivos: | ||

| + | *Conhecer o Quartus II e as caracteristicas dos dispositivos lógicos programáveis | ||

| + | *Analisar os tempos de propagação em um circuito combinacional | ||

| + | *Fazer a simulação funcional e temporal de um circuito combinacional. | ||

| + | |||

;Atividade: | ;Atividade: | ||

| − | *Realize a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis]] | + | *'''PASSO 1:''' Realize a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis]] |

| − | :*Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II. | + | :*Ao escolher a família de FPGAS, escolha inicialmente um dispositivo da família Cyclone II. Anote o código desse dispositivo. |

| − | :*Capture as telas solicitadas e depois utilize-as | + | :*Capture as telas solicitadas e depois utilize-as no relatório da atividade. |

:*Anote o tempo utilizado para cada uma das etapas do processo de compilação | :*Anote o tempo utilizado para cada uma das etapas do processo de compilação | ||

:*Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo. | :*Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo. | ||

:*Anote algum erro ('''Error''') ou alertas ('''Warnings''') que o Quartus II indicar no painel de mensagens '''[Messages]''' | :*Anote algum erro ('''Error''') ou alertas ('''Warnings''') que o Quartus II indicar no painel de mensagens '''[Messages]''' | ||

:*Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR) | :*Ao final salve o projeto em um arquivo QAR (sugestão PJ1.QAR) | ||

| − | * | + | |

| − | + | *'''PASSO 2''': Repita a atividade descrita em [[Conhecendo os dispositivos lógicos programáveis]], trocando a família e dispositivo a ser usado na implementação. Escolha nesta vez um dispositivos da família '''Cyclone IV E''' ou '''Stratix II GX'''. Anote o código desse dispositivo. | |

| − | + | :*Observe as mudanças que ocorrem tanto no tipo de Elemento Lógico disponível, no Chip Planner, no Pin Planner, e no circuito dos pinos de I/O. Note que estes FPGAs também apresenta novos componentes, tais como: Memória, Multiplicadores, DSP, PLL, DLL, etc. Verifique se consegue encontra-los no leiaute mostrado no Chip Planner, e documente aqueles que encontrar. | |

| − | * | + | :*Compare os resultados obtidos nos procedimentos do PASSO 1 e PASSO 2. |

| + | |||

| + | *'''PASSO 3''': Realize o procedimento descrito em [[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :*Ao escolher a família de FPGAS, escolha um dispositivo FPGA da família '''Cyclone IV E'''. Anote o código desse dispositivo. | ||

| + | :*Capture as telas mostradas no roteiro e depois utilize-as no relatório da atividade. | ||

| + | :*Anote o máximo tempo de propagação entre entrada e saída. | ||

| + | :*Anote o número de elementos lógicos utilizados e o número de pinos utilizados, bem com o percentual em relação ao número total do dispositivo. | ||

| + | :*Experimente modificar as configurações do compilador, conforme mostrado em '''Configurando o compilador'''. Se desejar mude a semente inicial trocando o valor de '''[Seed: 1]''' | ||

| + | :*Experimente Inserir diferentes restrições de atraso máximo para o compilador, e analise o resultado obtido. | ||

| + | :*Anote algum erro ('''Error''') ou alertas ('''Warnings''') que o Quartus II indicar no painel de mensagens '''[Messages]''' | ||

| + | :*Ao final salve o projeto em um arquivo QAR (sugestão PJ2.QAR) | ||

| + | |||

| + | *'''PASSO 4''': Realize a simulação funcional e também a temporal de um dos projetos '''CI74161''' ou do '''cálculo da distância de Hamming''' | ||

| + | :*Capture as telas que mostram o circuito funcionando e depois utilize-as no relatório da atividade. | ||

;Entregas: | ;Entregas: | ||

#Envie dois arquivos QAR contendo todos os arquivos necessário para compilar os dois projetos. | #Envie dois arquivos QAR contendo todos os arquivos necessário para compilar os dois projetos. | ||

| − | #Envie um relatório em PDF, incluindo as imagens capturadas (inclua legenda em cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório. | + | #Envie um relatório em PDF, incluindo as imagens capturadas (inclua legenda em cada figura) e escreva para cada imagem um texto comentando o que representa. O relatório também deve ter a identificação (autor, título, data) uma breve introdução e uma conclusão. A descrição dos procedimentos feita na página wiki não precisa incluída no relatório. |

#Use preferencialmente o [[Uso_do_Overleaf | Overleaf]] para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida. | #Use preferencialmente o [[Uso_do_Overleaf | Overleaf]] para gerar o relatório. Mas o uso de MS-Word, Libreoffice e Google Docs também é permitida. | ||

#A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega. | #A entrega será feita através do Moodle da disciplina. Observe o prazo de entrega. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | |||

<!-- | <!-- | ||

===AE4 - Programação do kit Mercurio IV=== | ===AE4 - Programação do kit Mercurio IV=== | ||

Edição das 20h01min de 22 de abril de 2022

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 4 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 5 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Exemplo de descrição de um multiplexador de 4 entradas entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

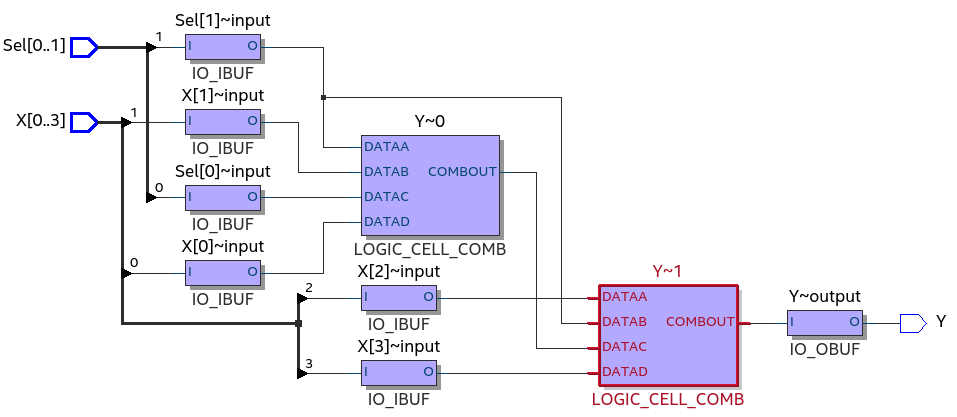

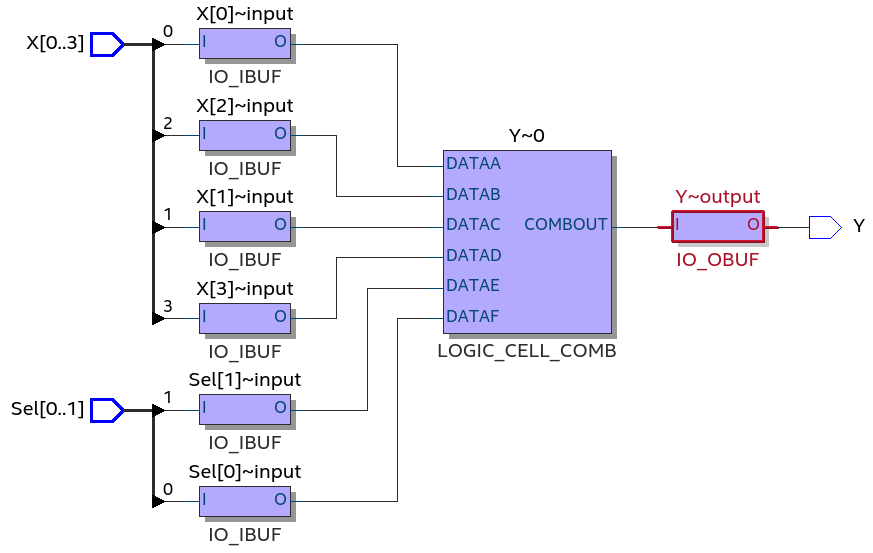

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

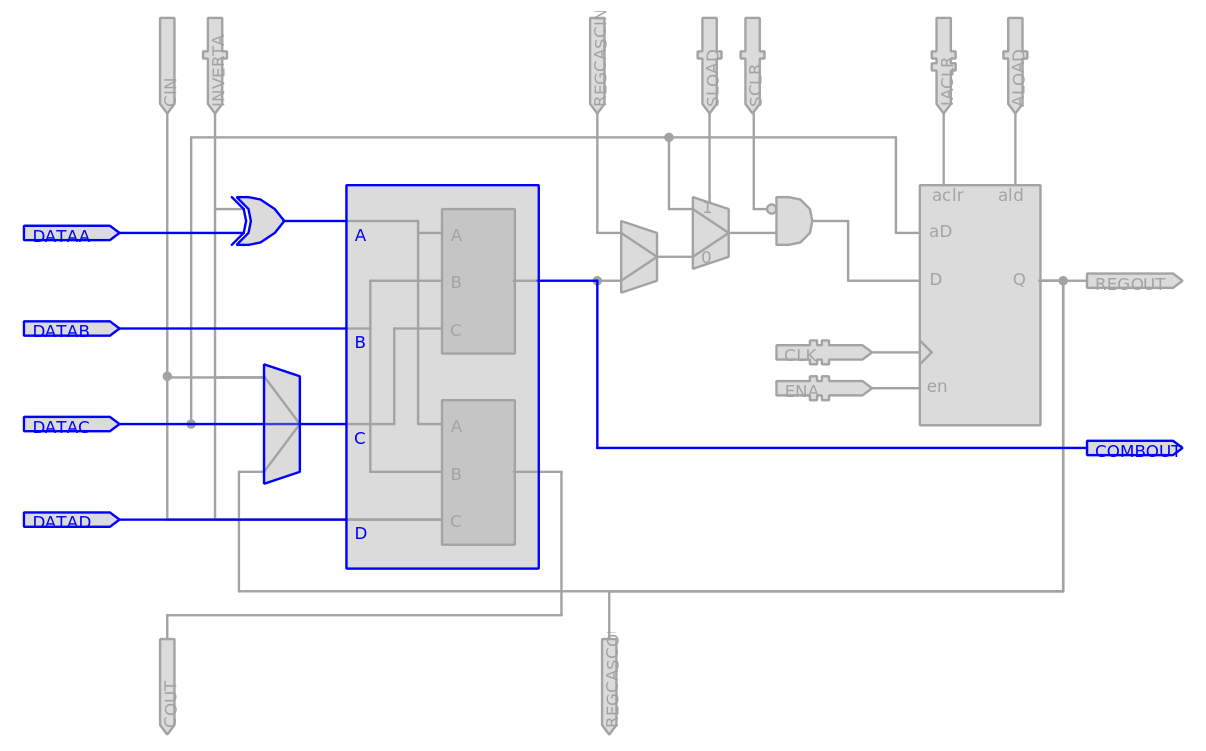

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF  ATUAL

|

ATIVIDADE EXTRA-CLASSE (AE)

A soma das atividades Extra-classe será correspondente a 20% do conceito final na disciplina. A entrega das mesmas será feita pelo Moodle da disciplinas, e cada dia de atraso irá descontar 0,2 na nota da atividade. Muitas dessas atividades também possuem BÔNUS que são adicionados aos conceitos das avaliações A1 e A2. Para os BÔNUS só serão considerados projetos entregues no prazo.

AE1 - Palavras-cruzadas INTRODUÇÃO

| AE1 - Palavras-cruzadas INTRODUÇÃO |

|---|

AE2 - Conhecendo os dispositivos lógicos programáveis

| AE2 - Conhecendo os dispositivos lógicos programáveis |

|---|

|