DLP29006-Engtelecom(2018-1) - Prof. Marcos Moecke

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ver pag. 60 a 73 de [2]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY operadores IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

div: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

);

END ENTITY;

ARCHITECTURE type_conv_arch OF operadores IS

BEGIN

-- Inserir o código e definir o tamanho das saidas.

END ARCHITECTURE;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

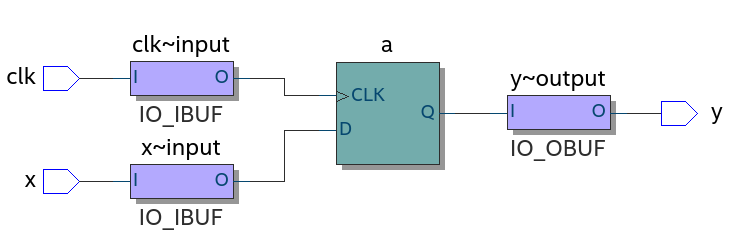

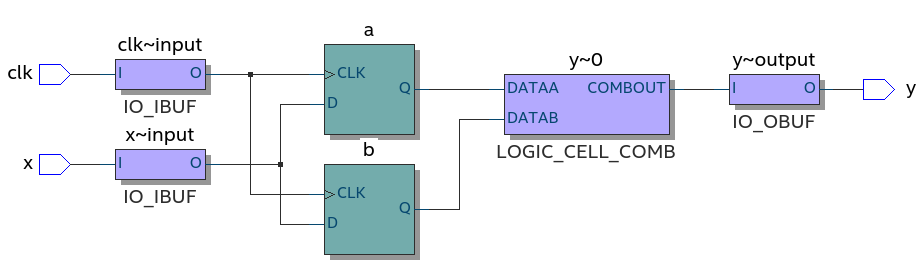

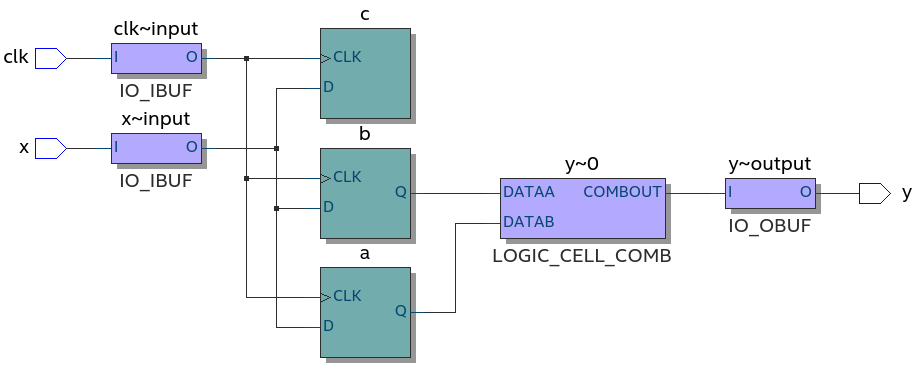

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

Uso da instrução ALIAS.

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

ATUAL |

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 6 - Projeto a nível de Sistema

entity counter60seg is

generic (fclk: integer := 2); -- valor usado para simulação.

-- generic (fclk: integer := 50_000_000); -- valor usado para implementação com clk de 50 MHz.

port (

clk, rst : in std_logic;

ssd_un, ssd_dz: out std_logic_vector(6 downto 0));

end entity ;

architecture version1 of counter60seg is

-- Versão proposta por Gabriel Cantu (processo único)

...

begin

...

end architecture ;

architecture version2 of counter60seg is

-- Versão proposta por Gustavo Constante (5 processos)

...

begin

...

end architecture ;

configuration counter60seg_cfg of counter60seg is

for version1 end for;

-- for version2 end for;

end configuration;

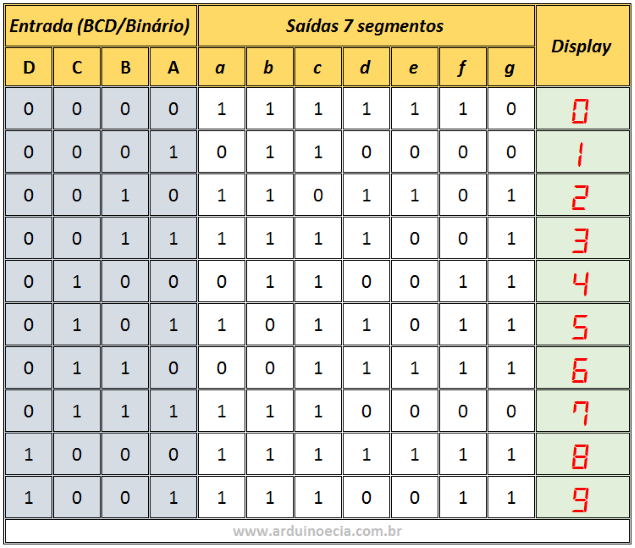

entity bin2ssd is

port (

bin: in std_logic_vector(3 downto 0);

ssd: out std_logic_vector(6 downto 0));

end entity ;

architecture with_case of bin2ssd is

...

begin

...

end architecture ;

FUNCTION e PROCEDURE (são chamados de subprogramas), e podem ser construídos em um PACKAGE, ENTITY, ARCHITECTURE, ou PROCESS. A instrução ASSERT é útil para verificar as entradas de um subprograma. Seu propósito não é criar circuito, mas assegurar que certos requisitos são atendidos durante a sintese e/ou simulação. Pode ser condicional ou incondicional (condição_booleana = FALSE). A sintaxe da instrução é: [rótulo:] assert condição_booleana

[report mensagem]

[severity nivel_severidade];

A mensagem pode ser criada usando STRINGs que podem ser concatenadas. O nível de severidade pode ser NOTE (para passar informação para o compilador/simulator), WARNING (para informar que algo não usual ocorreu), ERROR (para informar que alguma condição não usual "sério" ocorreu), ou FAILURE (para informar que uma condição não aceitável ocorreu). Normalmente o compilador para quando ocorre um ERROR ou FAILURE. NOTE é o valor "default".

function nome_funçao (lista_parametros_entrada) return tipo_saida is

declarações

begin

afirmações sequenciais

end function;

Abaixo segue um exemplo de cálculo do log2 de um número inteiro. Pode ser usado para determinar o número de bits necessário para um número natural. function log2c (n : integer) return integer is

variable m , p : integer;

begin

m := 0;

p : = 1;

while p < n loop

m : = m + 1;

p := p * 2;

end loop;

return m;

end log2c;

procedure nome_procedimento (lista_parâmetros_entrada, lista_parâmetros_saída) is

declarações

begin

afirmações sequenciais

end procedure;

|

Unidade 7

- Aula 33 (29 Mai)

- Simulação de sistemas digitais com Modelsim e testbench em VHDL

- Tipos de simulação:

- 1) simulação funcional (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003

- 2) simulação temporal (usando o QSIM) com entrada gráfica e análise gráfica da saída - OK já visto desde CIL29003

- 3) simulação funcional (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - OK já visto

- 4) simulação temporal (usando o ModelSim) com entrada gráfica (gerado com comandos force) e análise gráfica da saída - Não será visto

- 5) simulação funcional (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade

- 6) simulação temporal (usando o ModelSim) com entrada VHDL e análise gráfica da saída - Será visto nesta Unidade

- 7) simulação funcional (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída.

- 8) simulação temporal (usando o ModelSim e Matlab) com entrada VHDL e análise em VHDL da saída.

- Exemplo de Conversor Binário para Gray (Exercício 9.7)

- Para usar o ModelSim 10.1d na CLOUD-IFSC(191.36.8.33) abra um terminal e digite:

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

- ou

vsim

- Para usar o ModelSim 10.1d nos Laboratórios do IFSC campus São José abra um terminal e digite:

/opt/altera/13.0/quartus/modelsim_ae/linux/vsim

- Aula 36 (30 Mai)

- Simulação de sistemas digitais com Modelsim e testbench em VHDL

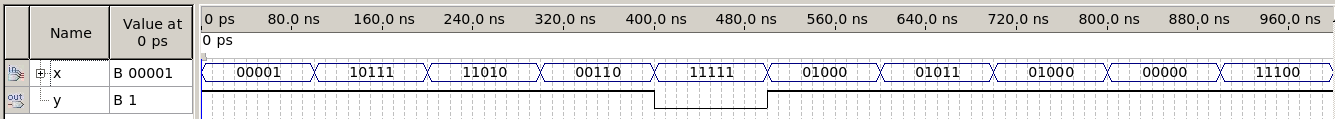

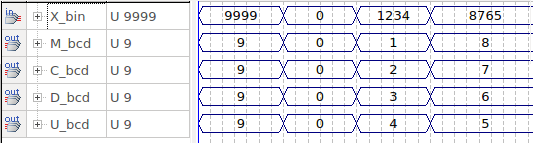

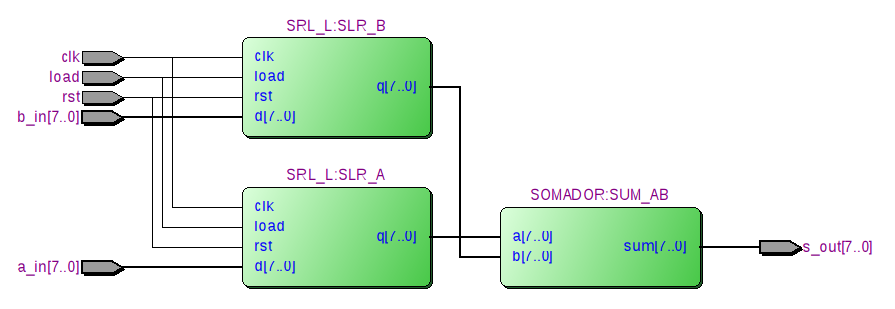

- Implementar um sistema constituído de dois circuitos de SHIFT RIGHT LOGICAL - SRL_L com entradas de DADOS, LOAD e RESET, e saída paralela. Crie um componente SOMADOR constituido de um somado do tipo UNSIGNED. Conecte as saídas dos SRL_L ao SOMADOR.

- Criar um testbench em VHDL para testar cada componente (SOMADOR, o SRL_L) e o sistema final. (faça com o test bench teste no minimo o funcionamento da entrada LOAD para 2 entradas diferentes de DADOS, o RESET, o SOMADOR e o funcionamento do SRL_L para uma sequencia de pelo menos N clocks, onde N é o número de bits das entradas.

- Note que no final deste projeto, deverão existir pelo menos os arquivos de projeto srl_l.vhd, somador.vhd, sistema.vhd e os arquivos de teste bench correspondentes srl_l_tb.vht, somador_tb.vht, sistema_tb.vht. Para facilitar a simulação no Modelsim recomenda-se criar também os arquivos de script srl_l.do, somador.do, sistema.do.

- DICA: Use o comando do Quartus II para gerar um template para o testbench. Selecione cada componente como TOP LEVEL e faça a ANÁLISE E SÍNTESE em seguida (Processing > Start > Start Test Bench Template Writer).

- Criação de sinais para Test Bench em VHDL

| Geração de sinal de clock |

|---|

-- DECLARAR

constant tclk: time := 1 ns;

signal clk : std_logic := '0';

-- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO CONCORRENTE)

clk <= not clk after tclk;

-- CLOCK COM PERIODO DE 2*tclk (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

clk <= '1';

wait for tclk;

clk <= '0';

wait for tclk;

END PROCESS;

|

| Geração de sinal de reset |

|---|

-- DECLARAR

constant treset: time := 100 ps;

signal reset : std_logic;

-- RESET COM DURAÇÃO DE treset (COM CÓDIGO CONCORRENTE)

reset <= '1', '0' after treset;

-- RESET COM DURAÇÃO DE treset (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

reset <= '1';

wait for treset;

reset <= '0';

wait;

END PROCESS;

|

| Geração de uma sequencia binária |

|---|

-- DECLARAR

constant t_a: time := 100 ps;

constant Nbits: natural := 8;

signal a : std_logic_vector(Nbits-1 downto 0);

-- GERAÇÂO DO SINAL a = [0 1 2 3 4 ...] COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL)

PROCESS

BEGIN

for i in 0 to 2**Nbits-1 loop

a <= std_logic_vector(to_unsigned(i,Nbits));

wait for t_a;

end loop;

END PROCESS;

|

| Geração de uma sequencia pseudoaleatória |

|---|

-- DECLARAR

constant t_a: time := 100 ps;

constant Nbits: natural := 8;

signal a : std_logic_vector(Nbits-1 downto 0) := (0 => '1', 3 => '1', others => '0');

-- GERAÇÂO DO SINAL a COM DURAÇÃO DE t_a em cada valor (COM CÓDIGO SEQUENCIAL)

-- USANDO UM CONTADOR LFSR

PROCESS

BEGIN

for i in 0 to 2**Nbits-1 loop

a <= (a(0) xor a(2) xor a(3) xor a(4)) & a(Nbits-1 downto 1); -- para 8 bits

wait for t_a;

end loop;

END PROCESS;

|

- Aula 37 (2 Jun)

- Simulação de sistemas digitais com Modelsim e testbench em VHDL

- Tempo livre para a resolução do Exercicio proposto.

Unidade 8

- Aula 38 (6 Jun)

- Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL

- O que é uma FSM - Finite State Machine

- Modelo de FSM

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END < entity_name > ;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF (clk'EVENT AND clk = '1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

CASE pr_state IS

WHEN A =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= C;

...

ELSE

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END < architecture_name > ;

- Usando o template acima descreva em VHDL a FSM indicada na Figura 11.1.

- Faça a simulação da FSM com Modelsim utilizando um testbench em VHDL que faça a FSM seguir os estados

- rst -> A -(x=0)-> A -(x=1)-> A -(x=2)-> B -(x=2)-> B -(x=0)-> C -(x=0)-> C -(x=2)-> C -(x=1)-> A -(x=2)-> B -(x=1)-> A.

- Ver pag. 277 a 35 de [2]

- Aula 39 (9 Jun)

- Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL

- Exemplo 11.1 Controlador de uma máquina de Venda

- Compile o código mostrado no Exemplo 11.1.

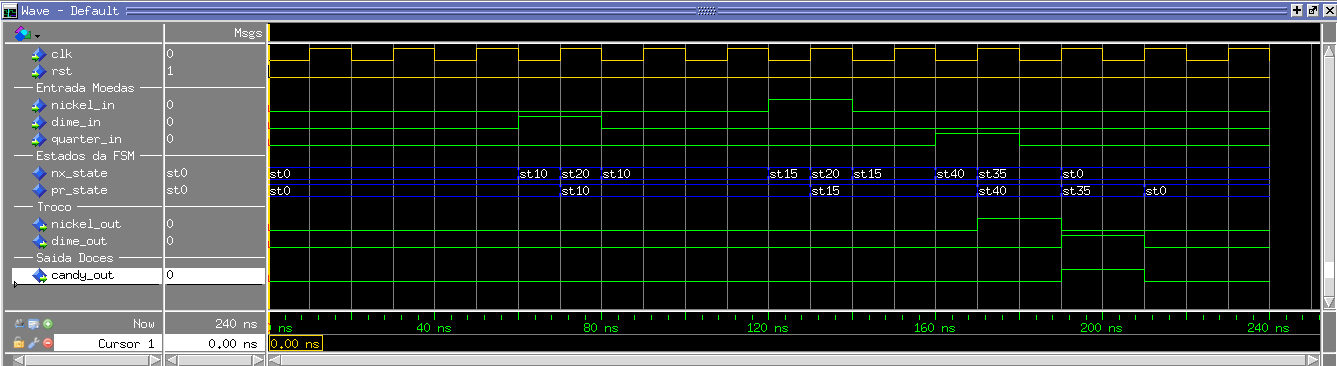

- Simule a FSM com Modelsim utilizando um testbench em VHDL para gerar o teste mostrado na figura abaixo.

- Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação.

- Aula 40 (12 Jun)

- Avaliação A2

- Aula 41 (13 Jun)

- Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL

- Exemplo 11.4 e 11.5 Alarme de carro.

- Projeto de um semáforo temporizado de 3 vias.

PROJETO FINAL

- Aula 42 a 46 (20 Jun a 30 Jun)

- Projeto Final - Sistema de controle de tráfego

- trabalho desenvolvido em equipes (ou individual)

- durante as aulas o professor esclarece dúvidas e orienta o trabalho

- Aula 47 (4 Jul)

- Avaliação de Recuperação de A1 e A2.

-->

Avaliações

- Avaliação A1 - Unidade 2 a 4 (27/04/2018) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2018) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD, e as tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2018) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

| EL0 - Resolução dos exercícios do Cap 2 |

|---|

especificado.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

|

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL4 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL5 - Resolução dos exercícios do Cap 5 |

|---|

|

Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 2,15 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335