DLP2-EngTel (Plano de Ensino)

Ir para navegação

Ir para pesquisar

|

MINISTÉRIO DA EDUCAÇÃO |

Plano de Ensino de 2015-1 - atual

DLP2 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS II

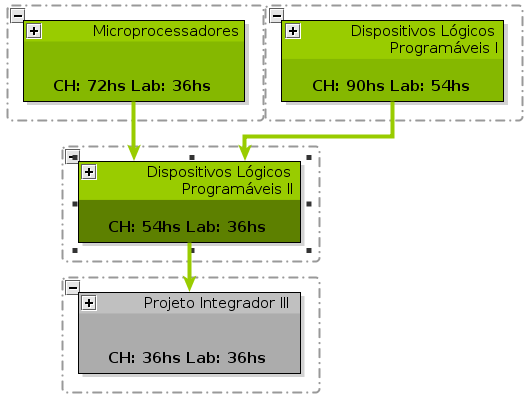

- CARGA HORÁRIA: 3 HORAS/SEMANA 54 HORAS. TEÓRICA = 18 HORAS. LABORATÓRIO = 36 HORAS

- PRÉ REQUISITOS: DLP1, MIC

- DISCIPLINAS SUCESSORAS: PJI3

- MÓDULO ESPECIALIZANTE

- Ementa

- Implementação de módulos de hardware em FPGA, reconfiguração de FPGA, processadores embarcados em FPGA, projetos avançados de sistemas utilizando FPGA

- Bibliografia Básica

- James W. Bignell e Robert Donovan Eletrônica Digital; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452

- D'amore, Roberto VHDL - Descrição e Síntese de Circuitos Digitais; 2ª ed. [S.l]:LTC, 2012. 259p. ISBN 9788521620549

- Pong P. Chu RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability; 1ª ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928

- Bibliografia Complementar

- NAVABI, Zainalabedin Embedded Core Design with FPGAs; 1ª ed. [S.l]:McGraw-Hill, 2006. 433p. ISBN 9780071474818

- SASS, Ronald; SCHMIDT,Andrew G. Embedded Systems Design with Platform FPGAs: Principles and Practices.; 1ª ed. [S.l]:Morgan Kaufmann, 2010. 464p. ISBN 9780123743336

- KILTS, Steve Advanced FPGA Design: Architecture, Implementation, and Optimization; 1ª ed. [S.l]:Wiley-IEEE, 2007. 352p. ISBN 9780470054376

- Volnei A. Pedroni Finite State Machines in Hardware; 1ª ed. [S.l]:The MIT Press, 2013. p. ISBN 9780262019668

ANEXOS