Mudanças entre as edições de "DLP2-EngTel (Plano de Ensino)"

Ir para navegação

Ir para pesquisar

(→ANEXOS) |

|||

| Linha 49: | Linha 49: | ||

=ANEXOS= | =ANEXOS= | ||

| − | ;[[Cronograma de atividades ( | + | ;[[Cronograma de atividades (DLP2-EngTel) | Cronograma de atividades]] |

;[http://tele.sj.ifsc.edu.br/arquivos/publicos/Horario/ Horário de Aula e Atendimento Paralelo] | ;[http://tele.sj.ifsc.edu.br/arquivos/publicos/Horario/ Horário de Aula e Atendimento Paralelo] | ||

{{ENGTELECO}} | {{ENGTELECO}} | ||

Edição das 16h38min de 25 de fevereiro de 2015

|

MINISTÉRIO DA EDUCAÇÃO |

Plano de Ensino de 2015-1 - atual

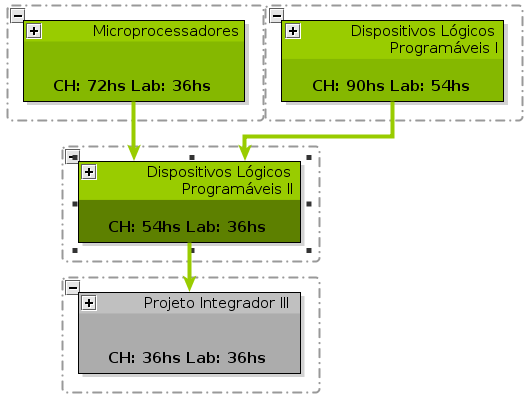

DLP2 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS II

- CARGA HORÁRIA: 3 HORAS/SEMANA 54 HORAS. TEÓRICA = 18 HORAS. LABORATÓRIO = 36 HORAS

- PRÉ REQUISITOS: DLP1, MIC

- DISCIPLINAS SUCESSORAS: PJI3

- MÓDULO ESPECIALIZANTE

- Ementa

- Implementação de módulos de hardware em FPGA, reconfiguração de FPGA, processadores embarcados em FPGA, projetos avançados de sistemas utilizando FPGA

- Objetivos

- Ao final do curso os alunos deverão ser capazes de projetar e desenvolver, de modo sistemático, sistemas digitais complexos com as seguintes características:

- Projetos desenvolvidos para geração de RTL eficiente;

- Projetos integráveis a grandes sistemas;

- Projetos portáveis, independentes de dispositivos, dependente de software, e reusáveis;

- Conteúdo Programático

- 1.Introdução, gerenciamento de complexidade e visão geral do projeto de sistemas digitais complexos (2h).

2.Projeto de circuitos combinacionais eficientes (6h).

3.Projeto de circuitos sequenciais eficientes (6h).

4.Projeto de circuitos baseados em máquina de estados eficientes (4h).

5.Register Transfer Methodology (10h).

6.Projeto hierárquico e parametrizado (8h).

7.Clock e sincronização (6h)

8.Desenvolvimento de projetos integrados com processador (10h)

Avaliações (2h).

- Estratégias de ensino utilizadas

- Aulas expositivas e dialogadas com o uso de lousa e projetor multimídia; roteiros de atividades em laboratório para aquisição de habilidades básicas; projetos baseados no conteúdo programático para verificar aplicação dos conceitos abordados; projeto final integrando conhecimentos adquiridos durante o curso.

- Critérios e instrumentos de avaliação

- Avaliação 1: prova teórica envolvendo os tópicos 1 a 4 do conteúdo programático;

- Avaliação 2: conjunto de 3 trabalhos práticos de implementação desenvolvidos ao longo dos conteúdos programáticos 5, 6 e 7;

- Avaliação 3: projeto final envolvendo o uso de um processador embarcado em FPGA e a aplicação dos conhecimentos adquiridos durante o curso.

- Critério de aprovação: o aluno deverá obter ao menos C em cada uma das avaliações.

- Conceito final: média aritmética dos três conceitos, obedecendo a seguinte correlação: A=4, B=3, C=2, com arredondamento dependente do desempenho do aluno constatado pelo professor observando critérios de assiduidade, participação nas discussões e pontualidade na entrega dos trabalhos.

- Mecanismo de recuperação

- Prova: será oferecida uma prova de recuperação da avaliação 1 ao final do semestre. O novo conceito substitui o anterior.

- A recuperação dos conceitos dos trabalhos se dará pela prorrogação do prazo de entrega. Alunos apresentando projetos no prazo terão conceito máximo A. Entregas com uma semana de atraso ou uma segunda tentativa de defesa do aluno terão conceito máximo B. Entregas com duas semanas de atraso ou uma terceira tentativa de defesa do aluno terão conceito máximo C. Projetos com mais de duas semanas de atraso não serão aceitos, implicando em conceito D e a consequente reprovação do aluno.

- Bibliografia Básica

- James W. Bignell e Robert Donovan Eletrônica Digital; 5ª ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452

- D'amore, Roberto VHDL - Descrição e Síntese de Circuitos Digitais; 2ª ed. [S.l]:LTC, 2012. 259p. ISBN 9788521620549

- Pong P. Chu RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability; 1ª ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928

- Bibliografia Complementar

- NAVABI, Zainalabedin Embedded Core Design with FPGAs; 1ª ed. [S.l]:McGraw-Hill, 2006. 433p. ISBN 9780071474818

- SASS, Ronald; SCHMIDT,Andrew G. Embedded Systems Design with Platform FPGAs: Principles and Practices.; 1ª ed. [S.l]:Morgan Kaufmann, 2010. 464p. ISBN 9780123743336

- KILTS, Steve Advanced FPGA Design: Architecture, Implementation, and Optimization; 1ª ed. [S.l]:Wiley-IEEE, 2007. 352p. ISBN 9780470054376

- Volnei A. Pedroni Finite State Machines in Hardware; 1ª ed. [S.l]:The MIT Press, 2013. p. ISBN 9780262019668

ANEXOS