Mudanças entre as edições de "DLP2-EngTel (Plano de Ensino)"

Ir para navegação

Ir para pesquisar

(→ANEXOS) |

|||

| (17 revisões intermediárias por 4 usuários não estão sendo mostradas) | |||

| Linha 1: | Linha 1: | ||

| − | {{Cab1-IF-SC-Engtelecom}} | + | {{Cab1-IF-SC-Engtelecom}} |

<BIG><center> | <BIG><center> | ||

| − | '''Plano de Ensino | + | '''Plano de Ensino 2020-2''' |

</center></BIG> | </center></BIG> | ||

| − | + | ;Dados gerais | |

| − | + | :COMPONENTE CURRICULAR: '''[[DLP2-EngTel|DLP2]]''' - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS II | |

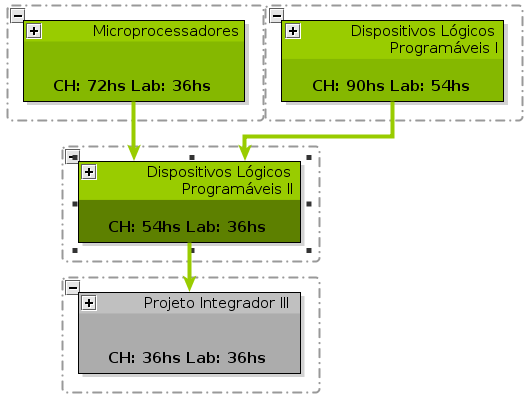

{{SUC |DLP2.png | 2}} | {{SUC |DLP2.png | 2}} | ||

:<SMALL>CARGA HORÁRIA: 3 HORAS/SEMANA 54 HORAS. TEÓRICA = 18 HORAS. LABORATÓRIO = 36 HORAS</SMALL><BR> | :<SMALL>CARGA HORÁRIA: 3 HORAS/SEMANA 54 HORAS. TEÓRICA = 18 HORAS. LABORATÓRIO = 36 HORAS</SMALL><BR> | ||

| Linha 11: | Linha 11: | ||

:<SMALL>DISCIPLINAS SUCESSORAS: [[PJI3-EngTel|PJI3]] </SMALL><BR> | :<SMALL>DISCIPLINAS SUCESSORAS: [[PJI3-EngTel|PJI3]] </SMALL><BR> | ||

:<SMALL> MÓDULO ESPECIALIZANTE </SMALL><BR> | :<SMALL> MÓDULO ESPECIALIZANTE </SMALL><BR> | ||

| + | |||

| + | ;Objetivos | ||

| + | :Ao concluir a disciplina os alunos deverão ser capazes de projetar e desenvolver, de modo sistemático, sistemas digitais complexos com as seguintes características: | ||

| + | :* Projetos desenvolvidos para geração de RTL eficiente; | ||

| + | :* Projetos integráveis a grandes sistemas; | ||

| + | :* Projetos portáveis, independentes de dispositivos, dependente de software, e reusáveis; | ||

| + | :* Projetos configuráveis e parametrizáveis; | ||

;Ementa | ;Ementa | ||

:Implementação de módulos de hardware em FPGA, reconfiguração de FPGA, processadores embarcados em FPGA, projetos avançados de sistemas utilizando FPGA | :Implementação de módulos de hardware em FPGA, reconfiguração de FPGA, processadores embarcados em FPGA, projetos avançados de sistemas utilizando FPGA | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

;Conteúdo Programático | ;Conteúdo Programático | ||

| − | : | + | # Introdução a Sistemas digitais avançados (6h): Gerenciamento de complexidade; Visão geral do projeto de sistemas digitais complexos; Processo de síntese de código VHDL. |

| + | # Projeto de circuitos combinacionais eficientes (6h): Compartilhamento de operadores e funcionalidades; Otimização de leiaute. | ||

| + | # Projeto de circuitos sequenciais eficientes (8h): Tipos de sincronismo de circuitos; Circuitos sequenciais síncronos; Projetos síncronos; Boas práticas em projetos sequenciais; Contadores; Registradores; | ||

| + | # Máquinas de estados finitos - MEF (6h): Representação; Análise temporal e desempenho; Tipos Moore vs Mealy; Descrição em VHDL; Otimizações. | ||

| + | # Register Transfer Methodology (8h): Visão geral da metodologia; Máquinas de estados finitos com fluxo de dados (MEFD); Análise temporal, desempenho, e síntese de MEFD. | ||

| + | # Projeto hierárquico e parametrizado (8h): Uso de declaração e especificação de configuração; Forma de especificação de parâmetros; uso de IF GENERATE; Particionamento; | ||

| + | # Processadores embarcados e depuração em FPGA (12h): Configuração e geração de processadores; Desenvolvimento de software embarcado; Integração de processadores com lógica externa; Depuração via analisador lógico embarcado. | ||

;Estratégias de ensino utilizadas | ;Estratégias de ensino utilizadas | ||

| − | :Aulas expositivas e dialogadas com | + | :* Aulas expositivas e dialogadas síncronas via a internet; |

| + | :* Videoaulas assíncronas com atividades para fixação do conteúdo; | ||

| + | :* Roteiros de atividades de simulação e análise com tutoria assíncrona; | ||

| + | :* Projetos baseados no conteúdo programático para verificar aplicação dos conceitos abordados. | ||

| + | |||

| + | ; Instrumentos e Critérios de avaliação | ||

| + | |||

| + | Instrumentos: | ||

| + | # AA: Atividades de acompanhamento | ||

| + | # AG: Atividades de grupo | ||

| + | # PJ: Projeto final | ||

| − | + | Critérios: | |

| − | * | + | *O Resultado Final (RF) será calculado da seguinte forma: RF = AA*2 + AG*4 + PJ*4 |

| − | * | + | * Para cada avaliação será atribuído um valor entre 0 e 10 e para o RF entre 1 e 10. |

| − | * | + | <!-- |

| − | * | + | * Valores não inteiros obtidos na média do RF serão arredondados: |

| − | + | :a) para baixo se a parte fracionária for menor que 0,4. | |

| − | + | :b) para cima se a parte fracionária for maior que 0,6. | |

| − | * | + | :c) de acordo com a avaliação subjetiva e frequência do aluno se a parte fracionária estiver entre 0,4 e 0,6. |

| − | * | + | * O resultado final mínimo para aprovação é 6 (seis), devendo o aluno ter os conceitos superiores ou iguais a 6 na AG e PJ. |

| + | --> | ||

| + | * A frequência será avaliada pelos encontros síncronos e pelas entregas das atividades no prazo. Mais de um mês sem presença ou entregas (sem justificativa prévia) será considerado abandono da disciplina. | ||

| + | <!-- :* Ao aluno que tiver frequência inferior a 75% na disciplina será atribuído nota 0 no conceito final. --> | ||

| + | * As AG são realizadas ao longo do semestre. Para cada atividade o aluno/equipe que não entregá-la no prazo preestabelecido, poderá entregar a atividade com desconto de 1 ponto por dia de atraso. Sendo permitido 7 dias de atraso no máximo. | ||

| + | * Não há tempo hábil para realizar recuperação do PJ. | ||

| + | =Bibliografia= | ||

;Bibliografia Básica: | ;Bibliografia Básica: | ||

| − | + | #D'amore, Roberto '''VHDL - Descrição e Síntese de Circuitos Digitais'''; 2a ed. [S.l]:LTC, 2012. 259p. ISBN 9788521620549. | |

| − | # D'amore, Roberto '''VHDL - Descrição e Síntese de Circuitos Digitais'''; | + | #James W. Bignell e Robert Donovan '''Eletrônica Digital'''; 5a ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452. |

| − | # Pong P. Chu '''RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability'''; | + | #Pong P. Chu '''RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability'''; 1a ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928. |

;Bibliografia Complementar: | ;Bibliografia Complementar: | ||

| + | #DESCHAMPS, Jean-Pierre; BIOUL, Gery J.A.; SUTTER, Gustavo D. '''Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems'''; ed. [S.l]:Wiley-Interscience, 2006. 808p. ISBN 9780471687832. | ||

| + | #IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel '''Elementos de eletrônica digital'''; 35a ed. São Paulo:Érica, 2003. 524p. ISBN 8571940193. | ||

| + | #KILTS, Steve '''Advanced FPGA Design: Architecture, Implementation, and Optimization'''; 1a ed. [S.l]:Wiley-IEEE, 2007. 352p. ISBN 9780470054376. | ||

| + | #PEDRONI, Volnei A '''Finite State Machines in Hardware'''; 1a ed. [S.l]:The MIT Press, 2013. p. ISBN 9780262019668. | ||

| + | #SASS, Ronald; SCHMIDT,Andrew G. '''Embedded Systems Design with Platform FPGAs: Principles and Practices.'''; 1a ed. [S.l]:Morgan Kaufmann, 2010. 464p. ISBN 9780123743336. | ||

| + | |||

| + | ;Bibliografia Adicional: | ||

# NAVABI, Zainalabedin '''Embedded Core Design with FPGAs'''; 1ª ed. [S.l]:McGraw-Hill, 2006. 433p. ISBN 9780071474818 | # NAVABI, Zainalabedin '''Embedded Core Design with FPGAs'''; 1ª ed. [S.l]:McGraw-Hill, 2006. 433p. ISBN 9780071474818 | ||

| − | + | ||

| − | |||

| − | |||

=ANEXOS= | =ANEXOS= | ||

Edição atual tal como às 00h17min de 6 de novembro de 2020

|

MINISTÉRIO DA EDUCAÇÃO |

Plano de Ensino 2020-2

- Dados gerais

- COMPONENTE CURRICULAR: DLP2 - DISPOSITIVOS LÓGICOS PROGRAMÁVEIS II

- CARGA HORÁRIA: 3 HORAS/SEMANA 54 HORAS. TEÓRICA = 18 HORAS. LABORATÓRIO = 36 HORAS

- PRÉ REQUISITOS: DLP1, MIC

- DISCIPLINAS SUCESSORAS: PJI3

- MÓDULO ESPECIALIZANTE

- Objetivos

- Ao concluir a disciplina os alunos deverão ser capazes de projetar e desenvolver, de modo sistemático, sistemas digitais complexos com as seguintes características:

- Projetos desenvolvidos para geração de RTL eficiente;

- Projetos integráveis a grandes sistemas;

- Projetos portáveis, independentes de dispositivos, dependente de software, e reusáveis;

- Projetos configuráveis e parametrizáveis;

- Ementa

- Implementação de módulos de hardware em FPGA, reconfiguração de FPGA, processadores embarcados em FPGA, projetos avançados de sistemas utilizando FPGA

- Conteúdo Programático

- Introdução a Sistemas digitais avançados (6h): Gerenciamento de complexidade; Visão geral do projeto de sistemas digitais complexos; Processo de síntese de código VHDL.

- Projeto de circuitos combinacionais eficientes (6h): Compartilhamento de operadores e funcionalidades; Otimização de leiaute.

- Projeto de circuitos sequenciais eficientes (8h): Tipos de sincronismo de circuitos; Circuitos sequenciais síncronos; Projetos síncronos; Boas práticas em projetos sequenciais; Contadores; Registradores;

- Máquinas de estados finitos - MEF (6h): Representação; Análise temporal e desempenho; Tipos Moore vs Mealy; Descrição em VHDL; Otimizações.

- Register Transfer Methodology (8h): Visão geral da metodologia; Máquinas de estados finitos com fluxo de dados (MEFD); Análise temporal, desempenho, e síntese de MEFD.

- Projeto hierárquico e parametrizado (8h): Uso de declaração e especificação de configuração; Forma de especificação de parâmetros; uso de IF GENERATE; Particionamento;

- Processadores embarcados e depuração em FPGA (12h): Configuração e geração de processadores; Desenvolvimento de software embarcado; Integração de processadores com lógica externa; Depuração via analisador lógico embarcado.

- Estratégias de ensino utilizadas

-

- Aulas expositivas e dialogadas síncronas via a internet;

- Videoaulas assíncronas com atividades para fixação do conteúdo;

- Roteiros de atividades de simulação e análise com tutoria assíncrona;

- Projetos baseados no conteúdo programático para verificar aplicação dos conceitos abordados.

- Instrumentos e Critérios de avaliação

Instrumentos:

- AA: Atividades de acompanhamento

- AG: Atividades de grupo

- PJ: Projeto final

Critérios:

- O Resultado Final (RF) será calculado da seguinte forma: RF = AA*2 + AG*4 + PJ*4

- Para cada avaliação será atribuído um valor entre 0 e 10 e para o RF entre 1 e 10.

- A frequência será avaliada pelos encontros síncronos e pelas entregas das atividades no prazo. Mais de um mês sem presença ou entregas (sem justificativa prévia) será considerado abandono da disciplina.

- As AG são realizadas ao longo do semestre. Para cada atividade o aluno/equipe que não entregá-la no prazo preestabelecido, poderá entregar a atividade com desconto de 1 ponto por dia de atraso. Sendo permitido 7 dias de atraso no máximo.

- Não há tempo hábil para realizar recuperação do PJ.

Bibliografia

- Bibliografia Básica

- D'amore, Roberto VHDL - Descrição e Síntese de Circuitos Digitais; 2a ed. [S.l]:LTC, 2012. 259p. ISBN 9788521620549.

- James W. Bignell e Robert Donovan Eletrônica Digital; 5a ed. São Paulo:Cengage Learning, 2010. 672p. ISBN 9788522107452.

- Pong P. Chu RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability; 1a ed. [S.l]:Wiley-IEEE Press, 2006. 694p. ISBN 9780471720928.

- Bibliografia Complementar

- DESCHAMPS, Jean-Pierre; BIOUL, Gery J.A.; SUTTER, Gustavo D. Synthesis of Arithmetic Circuits: FPGA, ASIC and Embedded Systems; ed. [S.l]:Wiley-Interscience, 2006. 808p. ISBN 9780471687832.

- IDOETA, Ivan Valeije; CAPUANO, Francisco Gabriel Elementos de eletrônica digital; 35a ed. São Paulo:Érica, 2003. 524p. ISBN 8571940193.

- KILTS, Steve Advanced FPGA Design: Architecture, Implementation, and Optimization; 1a ed. [S.l]:Wiley-IEEE, 2007. 352p. ISBN 9780470054376.

- PEDRONI, Volnei A Finite State Machines in Hardware; 1a ed. [S.l]:The MIT Press, 2013. p. ISBN 9780262019668.

- SASS, Ronald; SCHMIDT,Andrew G. Embedded Systems Design with Platform FPGAs: Principles and Practices.; 1a ed. [S.l]:Morgan Kaufmann, 2010. 464p. ISBN 9780123743336.

- Bibliografia Adicional

- NAVABI, Zainalabedin Embedded Core Design with FPGAs; 1ª ed. [S.l]:McGraw-Hill, 2006. 433p. ISBN 9780071474818

ANEXOS