DLP1-EngTel (página)

Revisão de 18h24min de 19 de fevereiro de 2015 por Moecke (discussão | contribs) (→Registro on-line das aulas)

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Informações Gerais

Registro on-line das aulas

- Aula 1 (5 fev)

- Dispositivos lógicos programáveis.

- Bases da linguagem VHDL.

- Tipos de dados, libraries, conversão de tipos, operadores, atributos.

- Código VHDL concorrente e sequencial.

- Projeto hierárquico.

- Simulação e Testbench

- Maquina de estado finita (FSM).

- Projeto Final de circuitos lógicos.

- Avaliações.

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- Ver pag. 413 a 418 de [1]

- Aula 2 (6 fev)

- Introdução aos dispositivos lógicos programáveis:

- CPLDs e FPGAs

- Fabricantes de DLPs

- Vizualização no Chip Planner de um projeto.

- Ver pag. 419 a 424 de [1]

- Aula 3 (11 fev)

- Introdução aos dispositivos lógicos programáveis:

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Vizualização no Chip Planner de um projeto.

- Ver pag. 424 a 431 de [1]

- Aula 4 (12 fev)

- Introdução ao VHDL.

- Exemplo de programação de um full adder. Utilize os arquivos .qar enviados (V1 - estrutural. V2 - comportamental) para analisar os circuitos obtidos e realizar as simulações funcional e temporal.

- Ver pag. 3 a 8 de [2]

- Aula 5 (13 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Libraries, Entity, Architecture

- Aula 6 (19 fev)

- Introdução ao VHDL.

- Estrutura do código VHDL

- Exercicios 2.2 (VHDL e QSIM)

- Exemplo de programação de um flip-flop

- Exercicios 2.3 (VHDL e QSIM)

- Ver pag. 3 a 8 de [2]

- Aula 7 (20 fev)

- Introdução ao VHDL.

Listas de Exercícios

- Unidade 1

- Fazer uma pesquisa sobre as formas como os PLDs são programados. Fusíveis, antifusíseis, memória PROM, EPROM, EEPROM, Flash, SRAM, etc. Formar equipes de até 2 alunos e apresentar um resumo em 2 a 3 páginas A4. PRAZO 20/02. Recomendo usar o modelo de artigo do Sharelatex do IFSC-CLOUD.

- Unidade 2

- Utilize no Quartus II o arquivo adders.qar para realizar os seguintes procedimentos:

- P0 - Selecione a família de FPGA Cyclone e selecione o dispositivo EP1C3T100A8

- P1 - Selecione como Top-Level Entity o arquivo adder_4bits.vhd e compile esse código [Processing > Start Compilation].

- Anote o número de elementos lógicos utilizados [Compilation Report > Flow Summary].

- Verifique qual é o maior tempo de propagação entre as entradas a,b e saida sum [Compilation Report > TimeQuest ... > Datasheet Report > Propagation Delay].

- Verifique o código RTL gerado [Tools > Netlist Viewers > RTL Viewer]

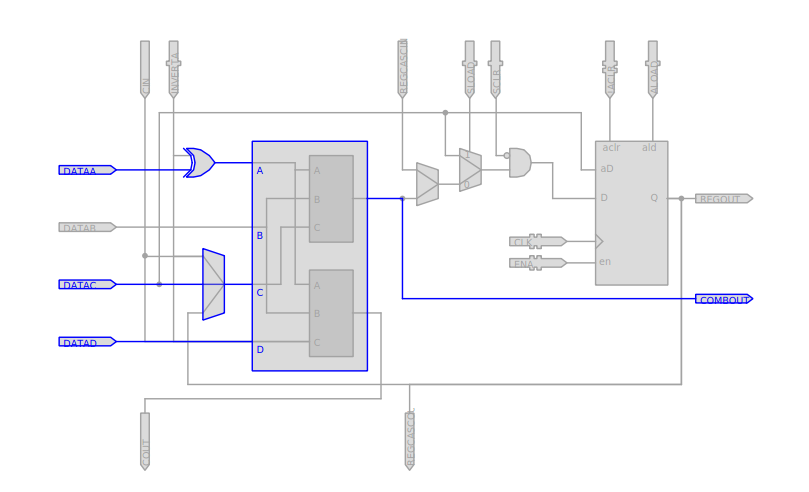

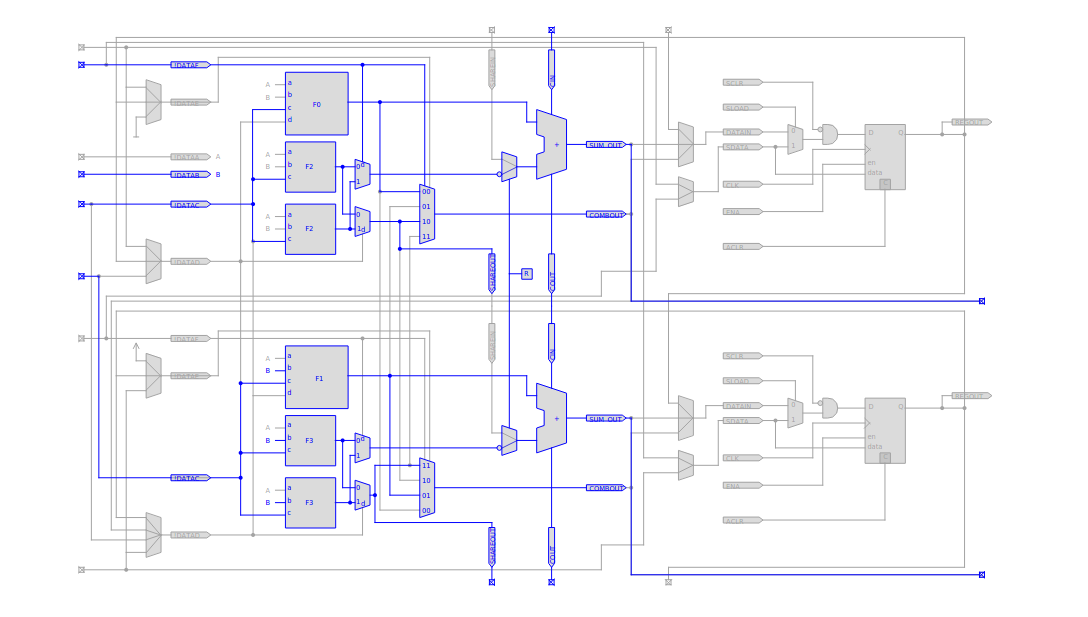

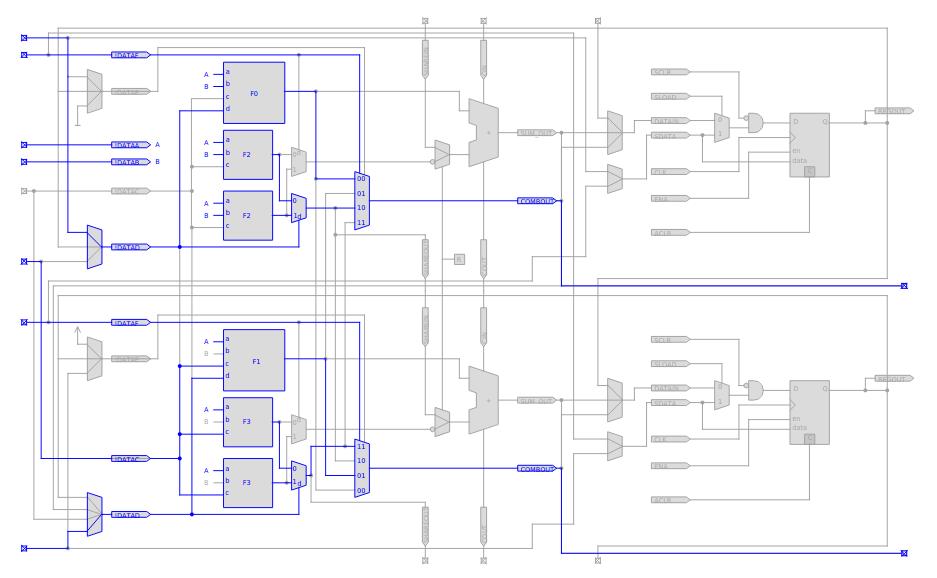

- Verifique como o circuito foi sintetizado abrindo o [Chip Planner], e após dar um zoom no elemento lógico/ALUT utilizado verifique o harware que foi utilizado com o [Resource Property Editor]

- Faça a simulação funcional utilizando o arquivo tb_adder_4bits.vwf no QSIM, e verifique se as somas estão corretas.

- P2 - Selecione como Top-Level Entity o arquivo adder_ripple_4bits.bdf e compile esse código [Processing > Start Compilation].

- Repita os passos do procedimento P1.

- P3 - Troque a familia do FPGA para Stratix III e selecione o dispositivo EP3SE50F484C2 e repita os procedimento P1 e P2 acima.

- P4 - Análise os resultados obtidos e chegue as suas conclusões. Escreva os resultados em um artigo resumido de 1 a 2 páginas. PRAZO 27/02. Recomendo usar o modelo de artigo do Sharelatex do IFSC-CLOUD.

| Exemplos de utilização do elemento lógico/ALUT |

|---|

|

Links auxiliares

Fabricantes de DLPs

Referências Bibliográficas: