DIG222802 AULA02

Flip-Flops

Os flip-flops são elementos de circuito que podem apresentar em seu funcionamento apenas dois estados estáveis. Não existem estados intermediários entre estes dois estados. A aplicação de um sinal de entrada pode mudar o dispositivo de um estado para outro e como a qualquer momento podemos saber qual é o estado em que ele se encontra, é possível considerar este circuito como uma memória capaz de armazenar um bit.

O flip-flop é o elemento básico das chamadas memórias estáticas. Existem diversos tipos de flip-flops encontrados nos circuitos digitais comerciais.

RS

O Flip-Flop R-S (Reset e Set) funciona da seguinte maneira:

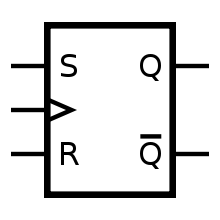

O flip-flop R-S tem duas saídas representadas por Q e Q\, assim, na condição inicial estável Q estará no nível baixo (0) e Q\ estará no nível alto (1). O processo que leva o flip-flop a este estado inicial pronto para funcionar é muito rápido, não demorando mais do que alguns microssegundos. Quando o flip-flop se encontra na situação indicada, com Q=0 e Q\=1, dizemos que ele se encontra "setado". A Figura 1 mostra o símbolo utilizado pelo Flip-Flop RS com clock.

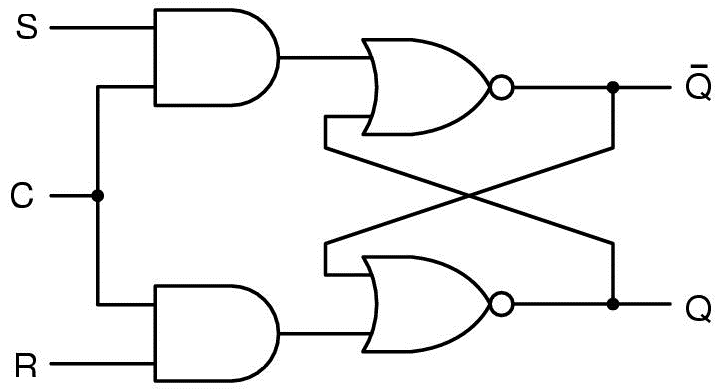

Figura 1 - Flip-Flop RS com clock.

Assim, estando o flip-flop na condição indicada, se desejarmos mudar

o estado, aplicamos o pulso na entrada SET, ficando Q=1 e Q\=0. Assim, estando o flip-flop na condição

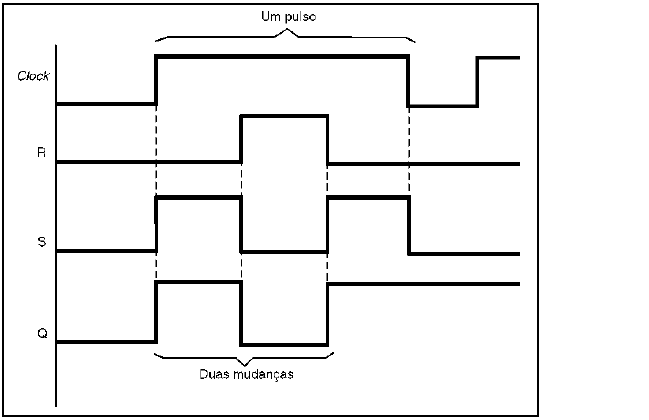

indicada, se desejarmos mudar o estado, aplicamos o pulso na entrada RESET, logo as saídas mudam para Q=0 e Q\=1. A Figura 2 mostra os diagramas de tempo para um FF R-S com clock.

Figura 2 - Diagrama de tempos para o Flip-Flop RS com entrada de clock.

Se a mudança de estado ou disparo (gatilho) ocorre quando o sinal de clock passa de 0 para 1, os

flip-flops são denominados "positive edge-triggered", enquanto que, se o disparo ocorre quando o clock vai do

nível 1 para 0, ou seja, na queda do nível lógico, os flip-flops são chamados de "negative edge-triggered".

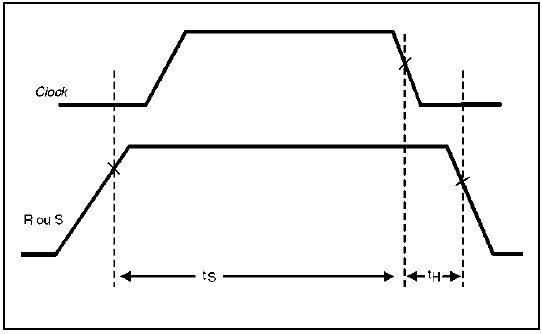

Neste tipo de circuito é muito importante levar em conta, num projeto de maior velocidade, os tempos em

que todo o processo ocorre. Assim, partindo do diagrama de tempos da Figura 3, vemos que a saída

do flip-flop só completa sua mudança de estado depois de um certo tempo, do pulso de clock ter sido aplicado.

Figura 3 - Tempos do flip-flop R-S.

Dois tempos são importantes neste tipo de circuito.

- tH: Hold Time ou Tempo de Manutenção é o tempo em que a entrada

deve permanecer ainda no circuito para que seu nível lógico seja reconhecido pelo flip-flop.

- tS: Setup Time ou tempo em que a entrada do flip-flop deve permanecer

no estado desejado antes da transição do clock que vai provocar a mudança de estado do circuito.

Tipo D

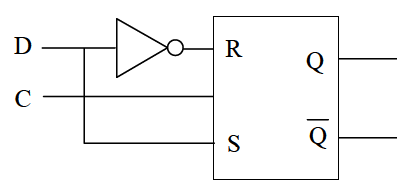

O Flip-Flop tipo D funciona da seguinte maneira: Quando houver variação do clock, o valor guardado na saída do flip-flop será igual ao valor da entrada D naquele momento.

O circuito do flip-flop do tipo D pode ser construído a partir do circuito do flip-flop RS controlado, basta adicionar uma porta inversora entre R e S fazendo com que as entradas sempre sejam invertidas uma da outra. Desse modo não vamos ter R=0 e S=0 ou R=1 e S=1 o que evita o chamado "estado proibido". A Figura 4 mostra essa configuração.

Figura 4 - Circuito do flip-flop tipo D utilizando o RS controlado.

| D | Q |

|---|---|

| 0 | 0 |

| 1 | 1 |

Tipo JK

Tipo T

Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabELETRO entre 16h às 17h45min. Está dividido em duas etapas: A primeira trata-se de testar o funcionamento de um latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. A segunda etapa é a de testar o funcionamento dos flip-flops D na configuração mestre-escravo também comprovando a tabela verdade.

Parte I

- Objetivo

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

Tabela Verdade

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

- Qa: saída do estado anterior.

Procedimento

- Formar as 8 equipes com 2 ou 3 integrantes;

- Desenhar as ligações já utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação de PR\ (preset) e CLR\ (clear) em VCC ou numa chave. Lembrando que são ativos baixos;

- Fazer a ligação entre as portas lógicas dos circuitos integrados;

- Fazer a ligação de R, S e C com chaves seletoras;

- Fazer a ligação das Saídas Q e Q\ aos LEDs;

- Testar a tabela verdade.

Parte II

- Objetivo

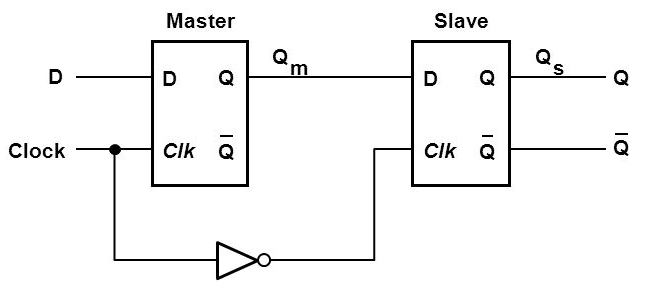

- Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 2.

Figura 2 - Flip-flop tipo D na configuração mestre–escravo.

Tabela Verdade FF tipo D

| D | Q | Q\ |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

Procedimento

- Mesmas equipes;

- Desenhar as ligações já utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação entre as FF passando pela inversora

- Fazer a ligação de D e Clock com chaves seletoras

- Fazer a ligação das Saídas Qm e Qs aos LEDs

- Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave).

- Ligar o clock a uma frequência de 1Hz e ver o que acontece.

Material Utilizado

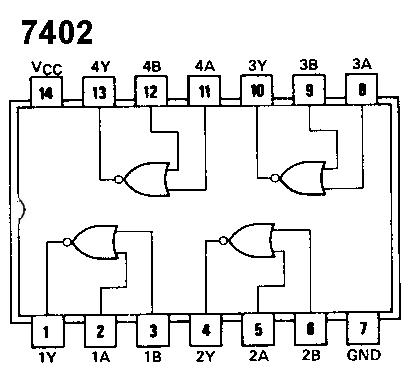

- CI 7402 (NOR)

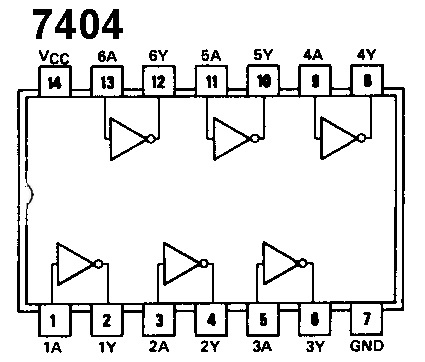

- CI 7404 (INV)

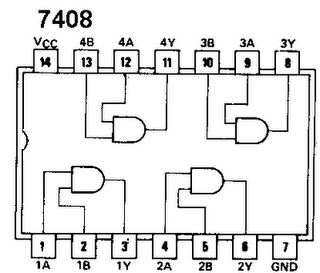

- CI 7408 (AND)

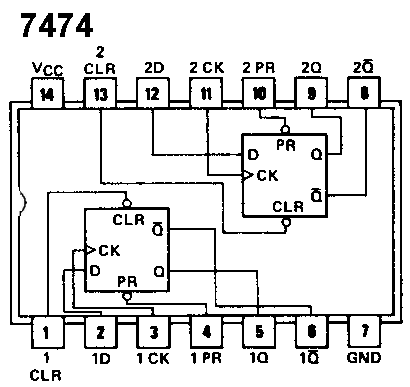

- CI 7474 (FF tipo D)

- fios diversos

- bancada digital

Circuitos

Figura 3 - Esquemático do CI 7402 - Portas NOR.

Figura 4 - Esquemático do CI 7404 - Portas Inversoras.

Figura 5 - Esquemático do CI 7408 - Portas AND.

Figura 6 - Esquemático do CI 7474 - Dois FF tipo D.

Referências

[1] http://www.inf.ufsc.br/~guntzel/isd/isd4.pdf

[2] TOCCI, Ronald J.; WIDMER N. S.; GREGOGRY L. M. Sistemas digitais: princípios e aplicações. São Paulo: Prentice Hall, 2003.

[3] http://www.cburch.com/logisim/docs/2.7/pt/html/libs/mem/flipflops.html

| << | <> | >> |

|---|