Como as portas lógicas são implementadas com transistores CMOS

Utilizando o simulador FALSTAD, verifique o funcionamento das portas lógicas básicas construídas com transistores MOS-FET, e uma carga resistiva.

Notem que as portas NAND e NOR são mais simples, e as AND e OR são construidas colocando um NOT na saída das NAND e NOR.

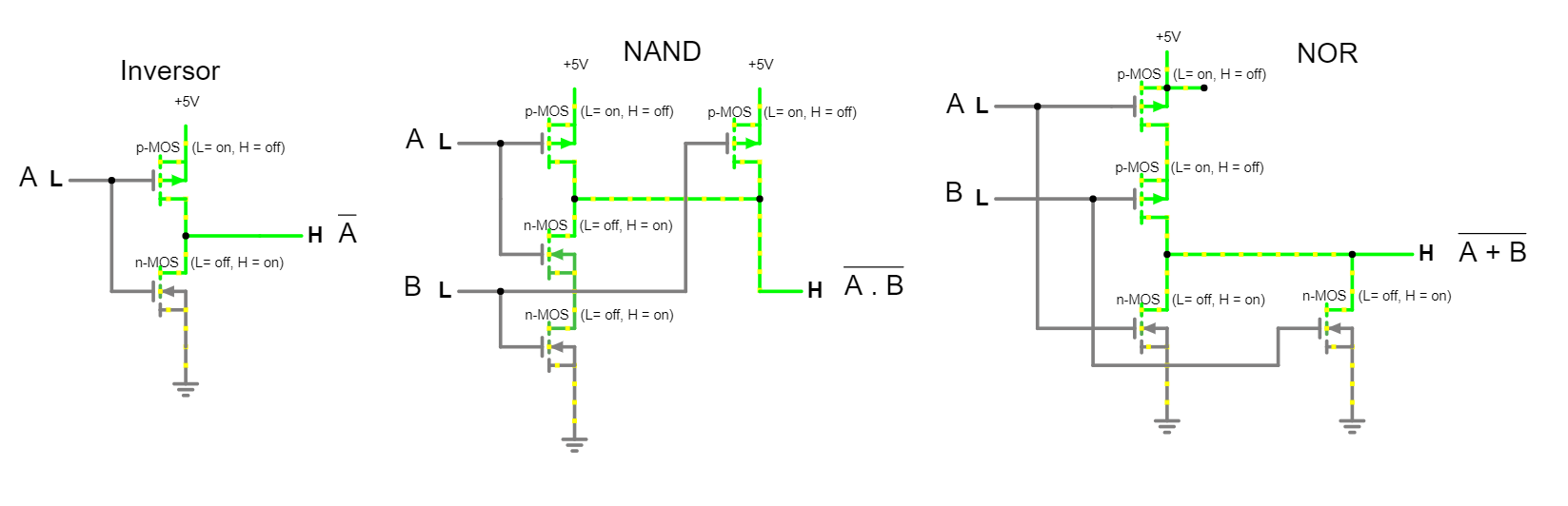

A tecnologia utilizada nos exemplos abaixo é CMOS (Complementary Metal-Oxide-Semiconductor), na qual cada transitor n-MOS tem um par p-MOS que funciona em oposição (complementaridade). Quando um está conduzindo (ON) o outro está em aberto (OFF).

- 4 transistores - porta NAND [3]

- 6 transistores - porta AND [4] - NAND + Inversor

- 4 transistores - porta NOR [5]

- 6 transistores - porta OR [6] - NOR + Inversor

- 12 transistores - porta XOR [7]

- 12 transistores - porta XNOR [8]

Figura 1 - Porta NOT, NAND e NOR CMOS

FONTE: [9]

Verifique como cada porta funciona. As tensões e correntes em cada transistor e da carga estão indicadas para observar o chaveamento dos transistores em cada estado. Lembre-se que L indica LOW (nível baixo, ou "0")e que H indica HIGH (nível alto, ou "1")

1 Inversor 3-state

Um outro componente muito importante para a criação de circuitos digitais é o BUFFER 3-state e o NOT (inversor) 3-state.

Neste circuito note que se a entrada OE estiver em L (baixo), os dois transistores Q2 e Q3 estão cortados (I ≈ 0), e consequentemente não há corrente na saída, independente do estado da entrada A. Este estado é conhecido de alta impedância ("Z"), ou terceiro estado (3-state), no qual nenhuma corrente entra no circuito nem sai, tendo o comportamento de um circuito aberto, desconectado. Por outro lado, quando OE estiver em H (alto), o circuito funciona normalmente como um Inversor, pois os dois transistores Q2 e Q3 estão saturados (V ≈ 0).