MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 1 - Introdução

|

Unidade 1 - Inicialização

- Aula 1 (16 fev)

- Ler In the beginning - ALTERA

- Ler ALTERA history

-

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

|

Avaliações

- Avaliação A1 - Unidade 2 a 4 (XX/XX/2017) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2017) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD, e as tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2017) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

| AE0 - Resumo estendido de Artigo (Entrega e Prazo ver Moodle)

|

|

|

| AE1 - Uso de código concorrente - ALU modificada (Entrega e Prazo ver Moodle)

|

- Implemente em VHDL uma Unidade de Lógica e Aritmética que tem como entrada os sinais A e B e que execute as seguintes instruções lógicas e aritméticas conforme o opcode de entrada:

- Unidade Lógica

| Instrução

|

Operação

|

opcode

|

GRUPOS

|

| Complemento de A |

Y = not A |

0000 |

1, 2, 3

|

| Complemento de B |

Y = not B |

0001 |

4, 5, 6

|

| And |

Y = A nand B |

0010 |

1, 3

|

| Nand |

Y = A and B |

0011 |

2, 4

|

| Or |

Y = A nor B |

0100 |

5, 6

|

| Nor |

Y = A or B |

0101 |

1, 4

|

| Xor |

Y = A xor B |

0110 |

2, 5

|

| Xnor |

Y = A xnor B |

0111 |

3, 6

|

- Unidade Aritmética

- (onde os valores de A e B podem ser positivos ou negativos)

| Instrução

|

Operação

|

opcode

|

GRUPOS

|

| Transfere A |

Y = A |

1000 |

1, 2, 3, 4, 5, 6

|

| Transfere B |

Y = B |

1001 |

1, 2, 3, 4, 5, 6

|

| complemento-2 de A |

Y = -A |

1010 |

1, 2, 3

|

| complemento-2 de B |

Y = -B |

1010 |

4, 5, 6

|

| Incrementa A |

Y = A + 1 |

1011 |

1, 4

|

| Decrementa A |

Y = A - 1 |

1011 |

2, 5

|

| Incrementa B |

Y = B + 1 |

1100 |

3, 6

|

| Soma A e B |

Y = A + B |

1101 |

1, 2

|

| Subtrai B de A |

Y = A - B |

1110 |

3, 4

|

| Subtrai A de B |

Y = B - A |

1110 |

5, 6

|

| Dobra o valor A |

Y = A * 2 |

1111 |

1, 2, 3

|

| Dobra o valor B |

Y = B * 2 |

1111 |

4, 5, 6

|

- A ENTITY deverá ter a seguinte interface:

ENTITY alu IS

GENERIC (N: INTEGER := 4); --word bits

PORT (

A, B: IN STD_LOGIC_VECTOR (N-1 DOWNTO 0);

OPCODE: IN STD_LOGIC_VECTOR (3 DOWNTO 0);

ERRO: OUT STD_LOGIC;

Y: OUT STD_LOGIC_VECTOR (N-1 DOWNTO 0));

END ENTITY;

- Verifique qual é o seu grupo, você apenas precisa implementar e simular as funções indicadas para o ele.

- Proponha uma ARCHITECTURE que implemente a ALU (Dica: utilize internamente o tipo de dado tipo integer ou do tipo "SIGNED").

- Se na operação realizada o resultado em Y não estiver correto, a saída ERRO deve ser setada.

- Anote o número de Elementos Lógicos (ou ALUTs) utilizados [Compilation Report > Flow Summary].

- Verifique o código RTL gerado [Tools > Netlist Viewers > RTL Viewer]

- Faça a simulação funcional no QSIM usando os valores mínimos e máximos e outros pares de valores representáveis e verifique se o resultado das operações está correto. Teste cada instrução (opcode) em separado. Analise os resultados obtidos para entradas com 4 bits e verifique os casos em que há ERRO.

- Escreva um relatório de no máximo 15 páginas contendo: título, identificação, introdução, o desenvolvimento da atividade e resultados, conclusão. O relatório deve conter as simulações funcionais feitas e a análise dos resultados obtidos. Também é fundamental relate o número de elementos lógicos necessários, o tipo de FPGA utilizado, e o máximo tempo de propagação deste circuito.

- Salve a imagem do circuito RTL e envie com arquivo .PNG.

- A entrega do relatório em .PDF e do arquivo .QAR e .PNG deverá ser feita na Plataforma Moodle de DLP29006, dentro do prazo indicado.

|

ATUAL

| APF - Projeto Final - Sistema de transmissão serial assíncrono (Entrega e prazos ver Moodle)

|

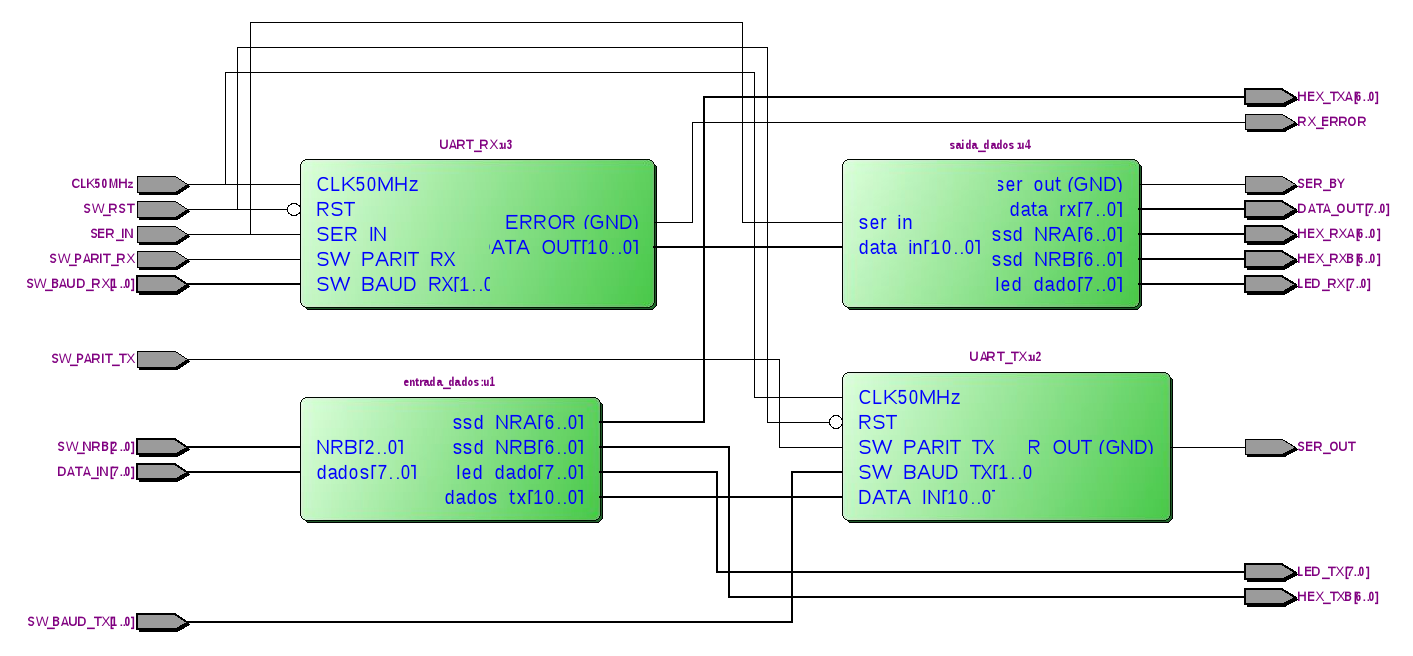

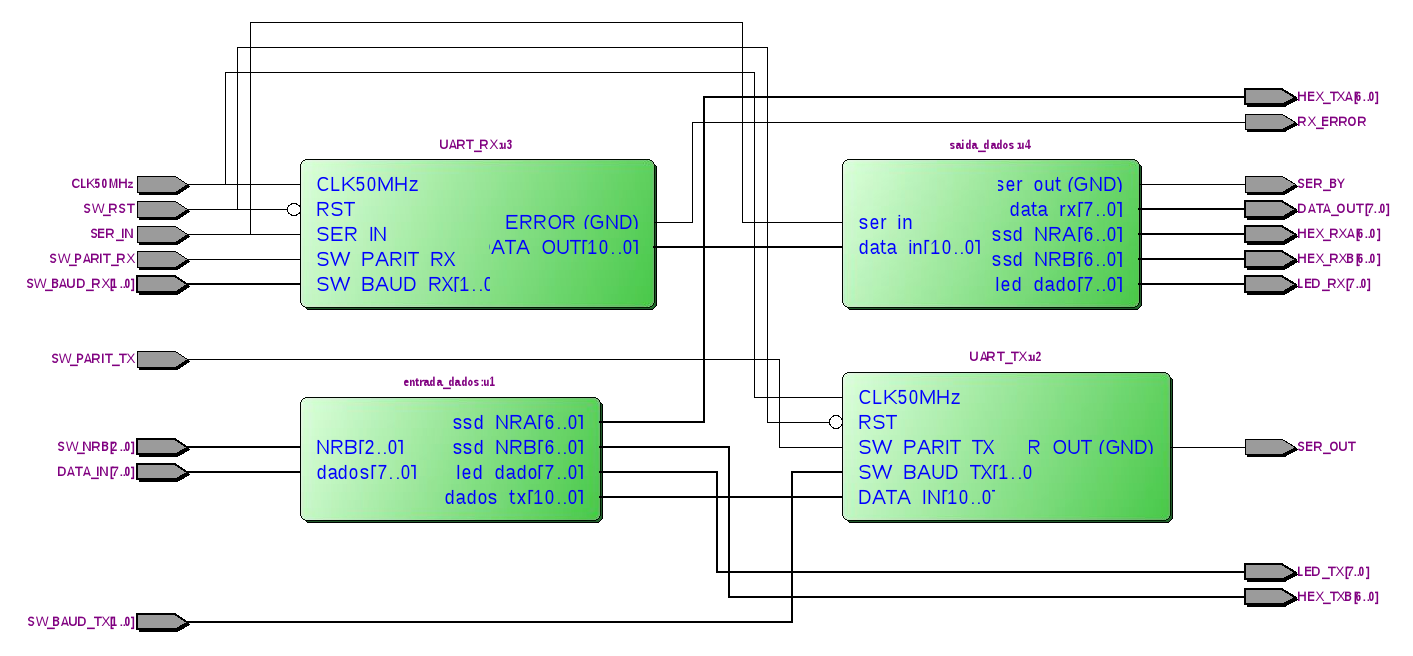

- Cada aluno (ou equipe de 2 alunos) deverá desenvolver um sistema de de transmissão serial assíncrono mostrado na figura abaixo:

Figura 1. Sistema de Comunicação Serial Assíncrono com Endereçamento de A para B

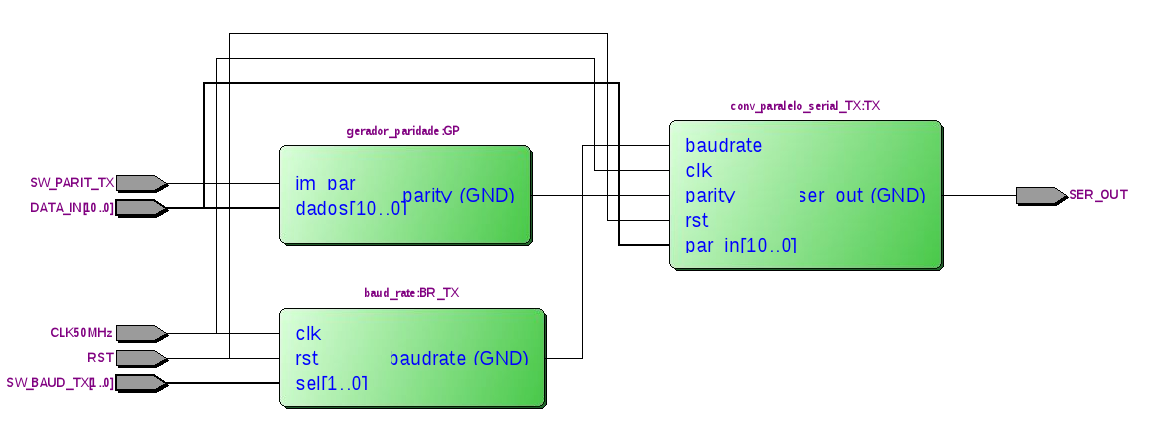

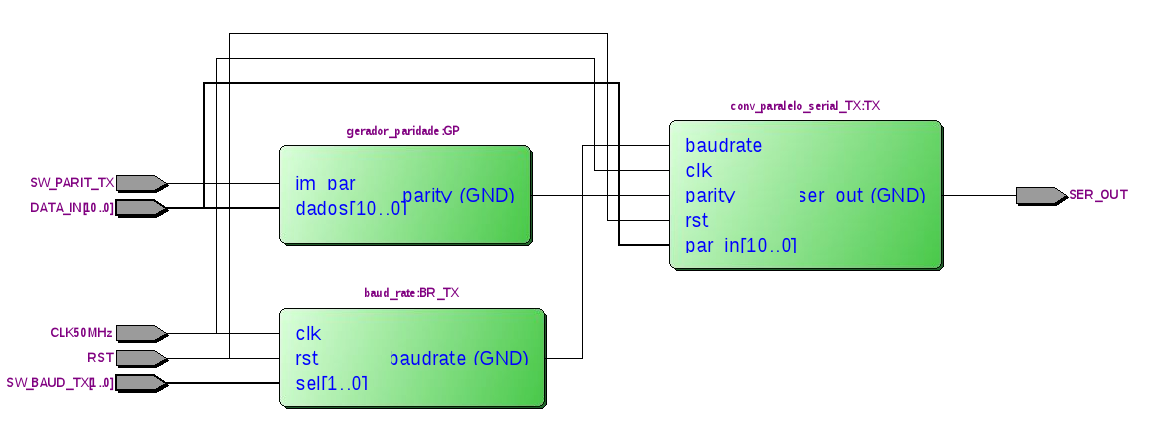

Figura 2. Interface transmissora serial

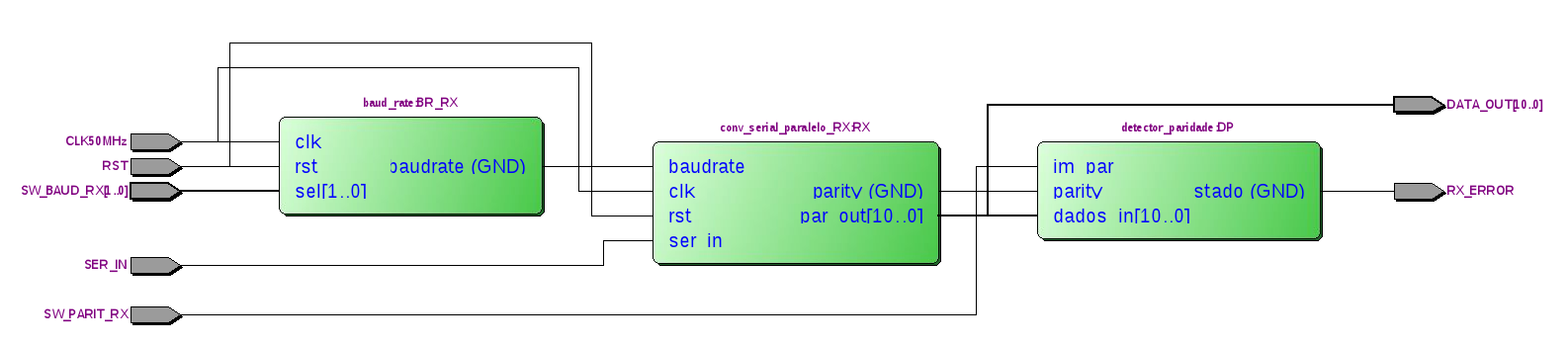

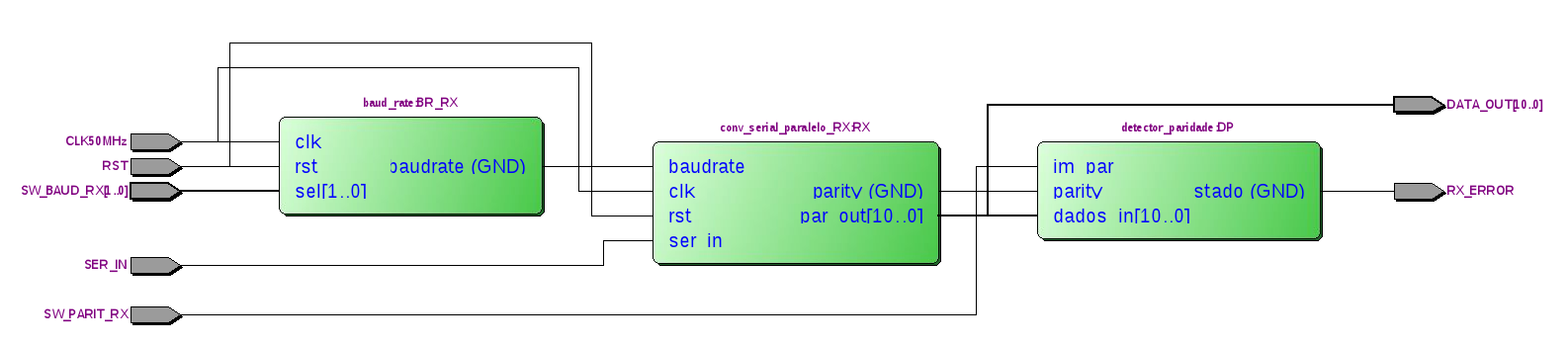

Figura 3. Interface receptora serial

- As Taxa de Transmissão deverão ser geradas a partir do clock principal CLK50MHz do kit a ser utilizado.

- A seleção da Taxa de Transmissão será feita através das chaves SW_BAUD_TX[1..0] para o transmissor e das SW_BAUD_RX[1..0] para o receptor.

- 00 => 0.1 bps, 01 => 10 bps, 10 => 1 kbps, 11 => 100 kbps.

- Na transmissão deverá ser enviado um bit paridade (par ou impar) de acordo com a chave seletora SW_PARITY.

- 0 => paridade par, 1 => paridade impar.

- No receptor a saída RX_ERROR deve ser usada para indicar que houve erro na recepção do dado.

900 px

- O sistema no seu TOP LEVEL deverá ser constituído de um Conversor Paralelo Serial, um Conversor Serial Paralelo, dois Geradores de Baud Rate, um Gerador de Paridade, um Detector de Paridade, um Detector de Número de Destino, um Circuito de Entrada de Dados, e um Circuito de Saída de Dados.

- O projeto deve ser desenvolvido integrando estes componentes no TOP LEVEL, de modo que neste nível existam apenas conexões entre estes componentes. Recomenda-se utilizar também componentes para a criação dos circuitos no segundo nível. O reuso de componentes já desenvolvidos nas aulas é fortemente encorajado.

- Durante a fase das simulações recomenda-se alterar o valor da frequência do CLK50MHz para 100kHz de modo a viabilizar uma simulação mais rápida. As simulações de cada componente do TOP LEVEL e da integração de todos componentes no TOP LEVEL devem ser feitas no MODELSIM, sendo a última obrigatoriamente feita usando testbench em VHDL.

- O sistema deverá ser implementado, testado e demonstrado no kit de hardware FPGA DE2-115 (ou Mercúrio IV) usando as chaves e leds disponíveis (ou pinos da GPIO para acionar circuitos externos).

- O arquivo QAR do projeto, e os arquivos .do e o testbench .vht para o MODELSIM devem ser enviados antecipadamente para o professor para conferencia antes da implementação no kit de hardware.

- Escreva um relatório técnico contendo os resultados em no máximo 10 paginas A4. O relatório além das tabelas com os dados de frequência máxima, número de componente, número de pinos, deverá conter a figura dos circuitos RTL da ENTITY top level com uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. A descrição da função dos pinos no Kit DE2-115 também deve ser feita.

|

-->

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

Referências Bibliográficas:

Curso de Engenharia de Telecomunicações