Conhecendo os dispositivos lógicos programáveis - QUARTUS II

Este experimento visa conhecer a estrutura interna dos dispositivos lógicos programáveis. Será utilizado como base o software Quartus II e os dispositivos da ALTERA.

1 Inserindo um circuito para programação

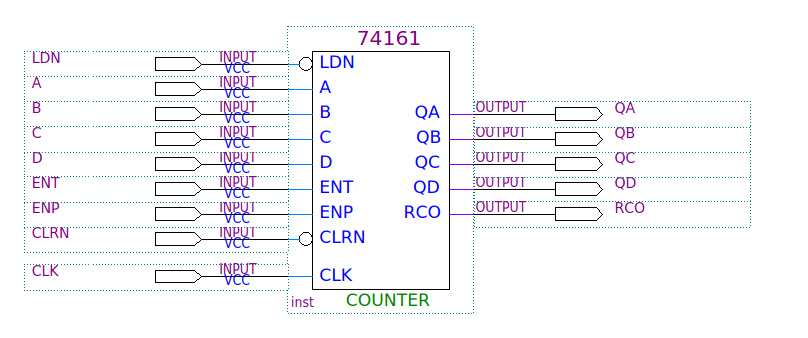

Abra um diagrama esquemático no Quartus II (File > Design Files > Block Diagram. Clique em ![]() para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em

para selecionar os símbolos e insira um contador "74161" (name: 74161). Em seguida clique em ![]() para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando Generate Pins for Symbol Ports.

para inserir os pinos de entrada e saídas. Opcionalmente você pode usar o botão direito do mouse e inserir todos os pinos de entrada e saída selecionando Generate Pins for Symbol Ports.

Após salvar o arquivo como "Ckt74161.bdf" em uma pasta vazia com nome AULA1, crie um projeto Ckt74161 utilizando a família MAX II com o dispositivo device=EPM240F100C4.

- Após salvar o arquivo "Ckt74161.bdf", o software oferece a opção de criar um projeto para o arquivo. Clique [Yes]. Em seguida clique [Next]. Selecione a pasta AULA1, e mantenha o nome do projeto e a top-level entity como Ckt74161, clicando [Next]. Clique novamente [Next] na tela de inclusão dos arquivos, pois o seu arquivo Ckt74161.bdf já foi incluído. No próxima tela de seleção da familia de DLPs e do número do dispositivo selecione Device Family: MAX II e Available device: EPM240F100C4, e clique em [Next], [Next] e [Finish] pois não há nenhum dado para ser alterado nestas telas de configuração.

- ATENÇÃO!!!: O Quartus não aceita caminhos de pastas com espaços, acentos ou outros caracteres exceto letras, números e "_"

Após isso compile o projeto (Processing > Start Compilation).