Registrador de Deslocamento - BDF e QSIM

Revisão de 08h42min de 3 de julho de 2019 por Odilson (discussão | contribs) (→Diagrama Esquemático)

Objetivos

- Inserir diagrama esquemático de um circuito lógico com o Quartus II

- Fazer a simulação funcional de um circuito com o QSIM

- Gerar formas de onda para entrada de simulação

- Fazer a simulação temporal de um circuito com o QSIM

- Preparar o circuito lógico para gravação no kit DE0-Nano

Diagrama Esquemático

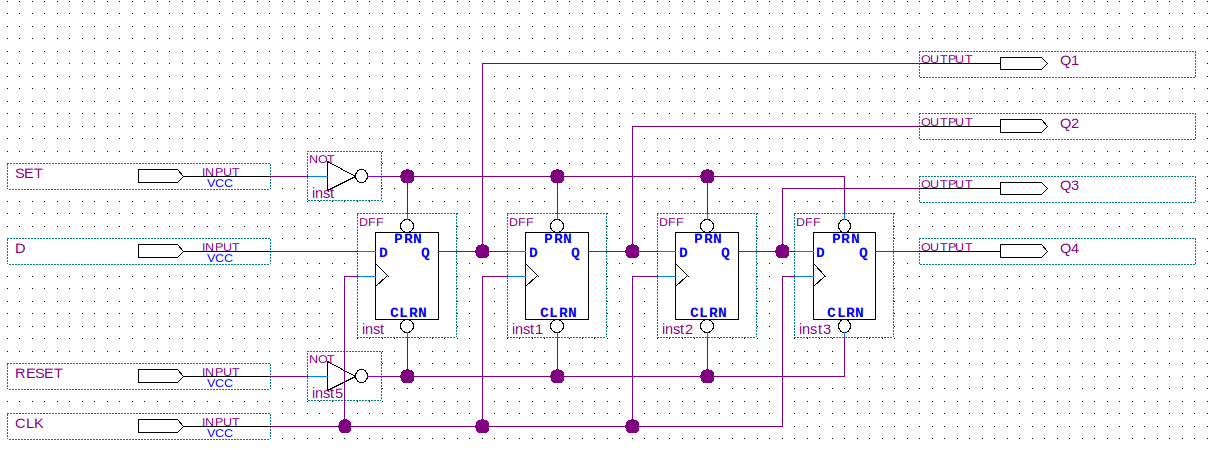

- Abra o Quartus II (versão 12.1) e insera o diagrama esquemático de um registrador de deslocamento com 4 DFF, conforme a figura abaixo.

- Dica use symbol name: dff e not, para inserir os componentes.

Após salvar o arquivo como RegDeslocamento.bdf em uma pasta vazia com nome EX_1, e crie um projeto RegDeslocamento.qpf utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7. Após isso compile o projeto.

Simulação funcional com o QSIM

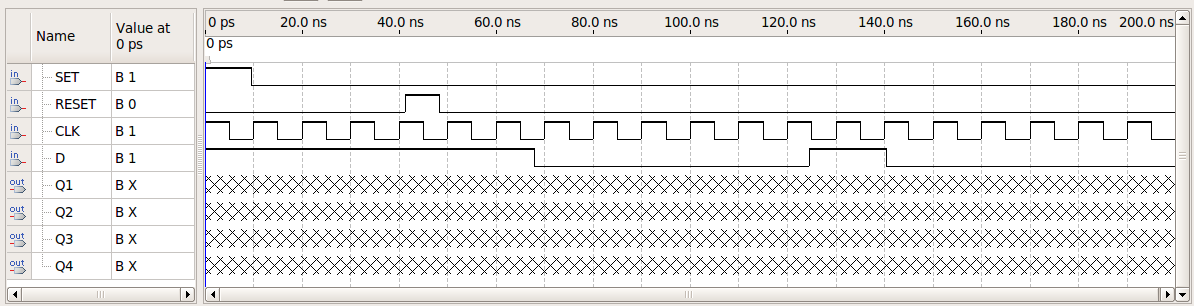

- Crie as formas de onda para entrada da simulação (File > New University VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome teste1.vwf.

- Indique como a simulação será feita (Simulation > Run Functional Simulation). Salve o arquivo de forma de onda - teste1.vwf.

- Faça a simulação do circuito lógico usando o sinal criado (Processing > Start Simulation)

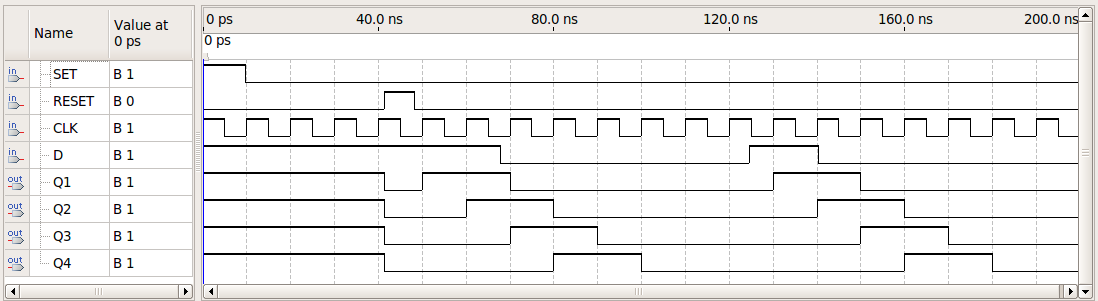

- Verifique se o resultado obtido corresponde a um Registrador de Deslocamento.

- Note que a entrada de SET e RESET não estão sincronizadas com o relógio (CLK). Os sinais de saída dos DFF são todos sincronizados com a borda de subida do CLK.

- Meça a duração dos pulsos ALTOS após o tempo de 120 ns do sinal D, Q1, Q2, Q3 e Q4. Explique o motivo da diferença de duração.

- Inverta o CLK (Clique no sinal CLK, clique na opção do menu C e ajuste Start Value = <inverta o valor, por exemplo, se o campo se encontrava em 1 ajuste para 0) e repita a simulação. Salve a entrada como teste2.vwf e o sinal de saída como resultadoF2.vwf.

- Entre 120ns e 150ns mude o sinal de SET para '1' e repita a simulação. Salve a entrada como teste3.vwf.

Simulação temporal com o QSIM

- Para alterar para simulação temporal utilize, no Simulador, Simulation >> Run Timing Simulation.

- Obs: O simulador somente consegue fazer simulação temporal para as famílias Ciclone III ou mais simples. Tenha certeza que você escolheu um device compatível.

- Faça a simulação do circuito lógico. Abra o arquivo resultado da simulação. Verifique as mudanças que ocorreram nos sinais de saída Q1, Q2, Q3 e Q4. Salve o sinal de saída como resultadoT1.vwf.

- Meça os atrasos dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal RESET.

- Meça os atrasos dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal CLK.

- Qual é a conclusão que você pode chegar em relação ao tempo de propagação e ?

- Como você poderia medir o tempo de atraso dos sinais Q1, Q2, Q3 e Q4 em relação ao sinal SET?

- Meça a duração dos pulsos ALTOS após o tempo de 120 ns do sinal D, Q1, Q2, Q3 e Q4. Explique o motivo da diferença de duração.

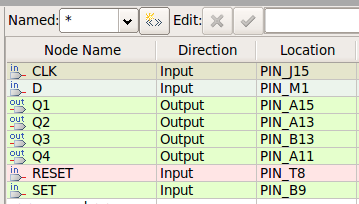

Preparando para gravar o circuito lógico no FPGA

Para gravar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE0-Nano.

- Mude a família e dispositivo a ser usado (Assignments > Devices), para família family=Cyclone com o dispositivo device=EP1C3T100A8 ou Family = Cyclone IV E com dispositivo device = EP4CE30F23C7.

- Atribua os pinos conforme o Kit DE2-115 - Cyclone: EP1C3T100A8 ou Mercurio IV - Cyclone IV: EP4CE30F23C7, utilizando como entradas as chaves. Como saída utilizaremos os leds.

- Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático.