Circuito de Multiplicação Binária: mudanças entre as edições

Ir para navegação

Ir para pesquisar

| Linha 17: | Linha 17: | ||

</center> | </center> | ||

*Salve o arquivo como '''FullAdder.bdf''' em uma pasta vazia com nome '''Exp7''', e crie um projeto '''Multiplicador | *Salve o arquivo como '''FullAdder.bdf''' em uma pasta vazia com nome '''Exp7''', e crie um projeto de nome '''Multiplicador''' utilizando a família family='''Cyclone''' com o dispositivo device='''EP1C3T100A8''' ou Family='''Cyclone IV E''' com o dispositivo device='''EP4CE30F23C7'''. | ||

*Faça a Análise e Síntese do projeto. | *Faça a Análise e Síntese do projeto. | ||

*Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e ['''File''' > '''Create/Update''' > '''Create Symbol Files for Current File'''] > ['''Save'''] > ['''OK''']. | *Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e ['''File''' > '''Create/Update''' > '''Create Symbol Files for Current File'''] > ['''Save'''] > ['''OK''']. | ||

Edição das 08h10min de 27 de maio de 2015

- Objetivos

- Compreender o funcionamento Multiplicador discreto;

- Construção de um projeto hierárquico;

- Obter o sinal de saída simulado usando o QSIM - diagrama funcional e temporal;

- Verificar os resultados obtidos;

- Materiais necessários

- 74X86 XOR (disponível na biblioteca da ALTERA)

- 74X00 NAND(disponível na biblioteca da ALTERA)

- 74X32 OR(disponível na biblioteca da ALTERA)

- Computador com software Quartus II da Altera.

1 Diagrama Esquemático

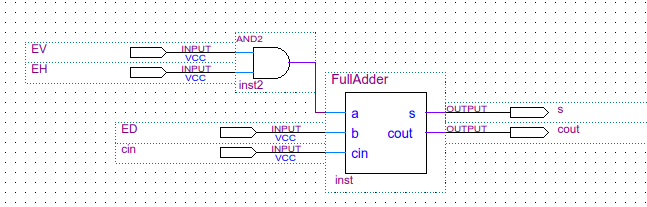

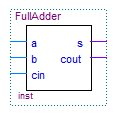

- Abra o Quartus II (versão 13.0.1 SE) e insira o diagrama esquemático do somador completo, conforme a figura abaixo.

- Salve o arquivo como FullAdder.bdf em uma pasta vazia com nome Exp7, e crie um projeto de nome Multiplicador utilizando a família family=Cyclone com o dispositivo device=EP1C3T100A8 ou Family=Cyclone IV E com o dispositivo device=EP4CE30F23C7.

- Faça a Análise e Síntese do projeto.

- Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

- Crie um novo diagrama [File > New > Block diagram/Squematic file > OK].

- Insira o diagrama esquemático do módulo básico do multiplicador, utilizando o componente FullAdder anteriormente criado e monte o circuito apresentado abaixo.

- Salve o arquivo como ModuloBMultiplicador.bdf na mesma pasta do Exp7.

- Mude o Top Level para este circuito [Project > Set as Top-Level Entity]. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático do ModuloBMultiplicador > [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

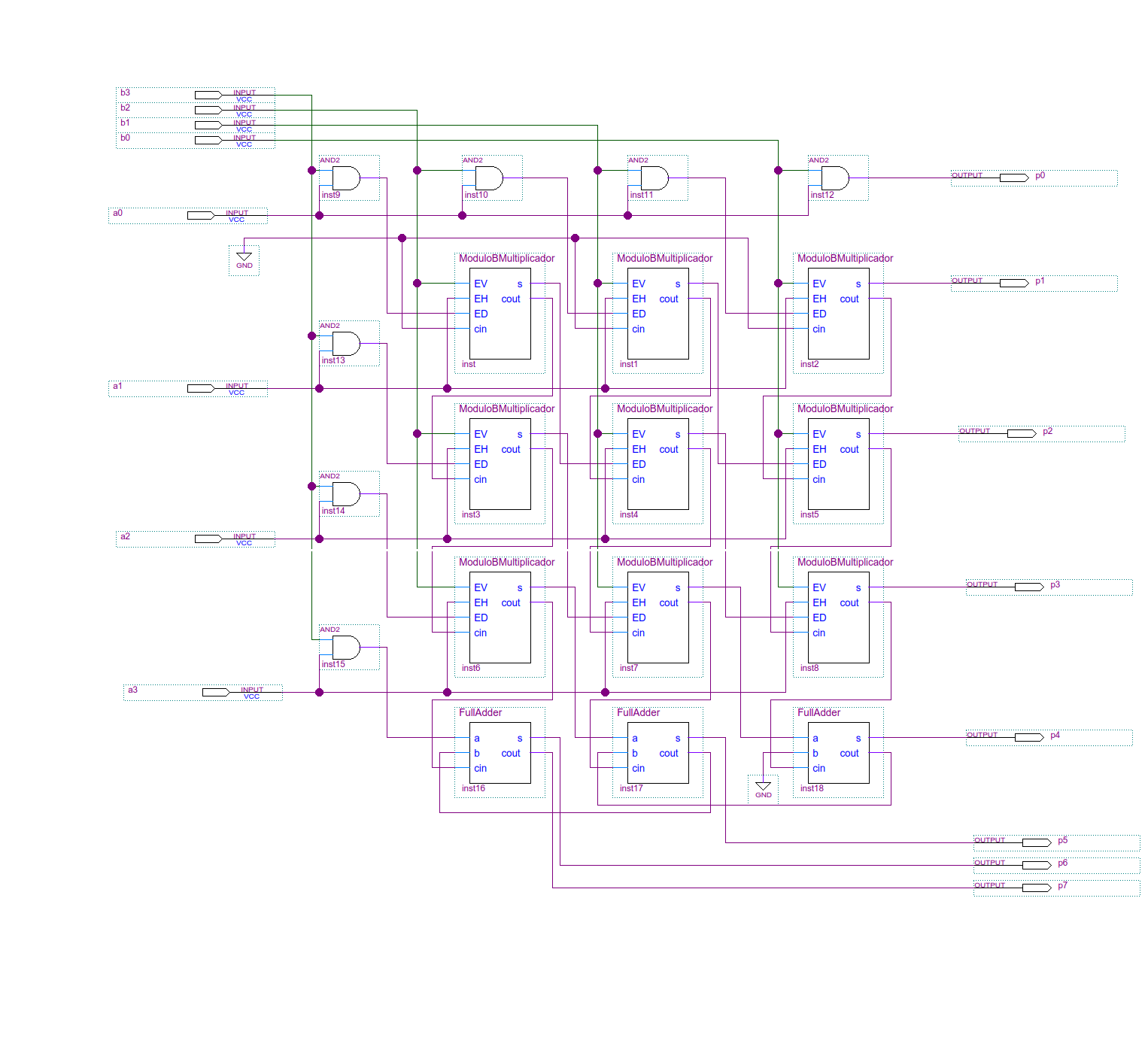

Abra um novo diagrama esquematico no Quartus II [File > New > Block diagram/Squematic file > OK] e insira o circuito digital abaixo utilizando os componentes FullAdder e ModuloBMultiplicador criados anteriormente.

- Salve o arquivo como Multiplicador4bits.bdf na mesma pasta do Exp7.

- Mude o Top Level para este circuito [Project > Set as Top-Level Entity]. Após isso faça a Análise e Síntese do projeto.

2 Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM [File > New > University Programa VWF].

- Defina o tempo de simulação [Edit > Set End Time ... = 1000 ns].

- Importe todos os nós de lista do projeto [Edit > Insert > Insert Node or Bus > Node Finder > List > >> > OK > OK].

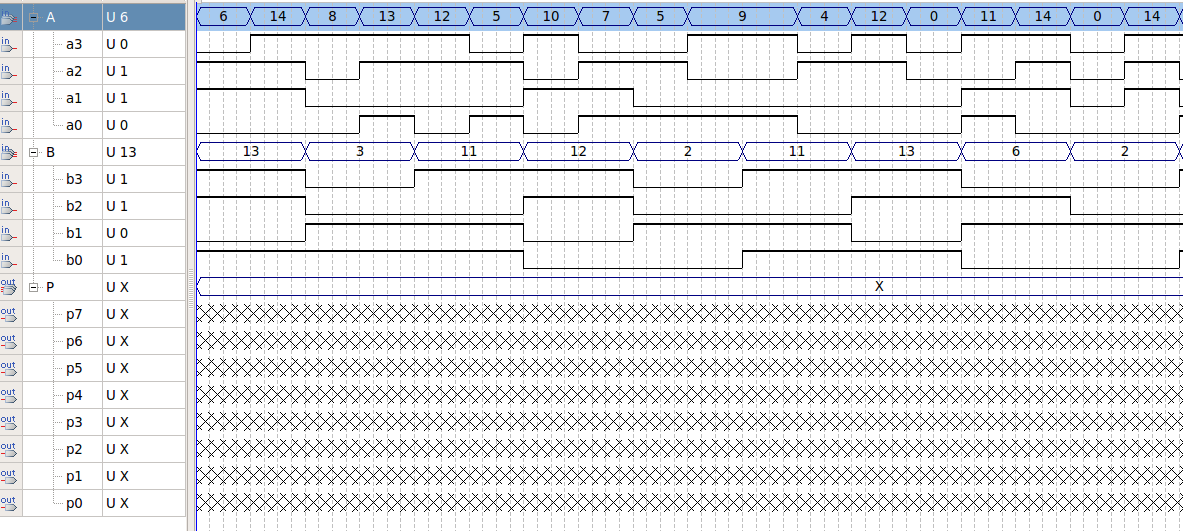

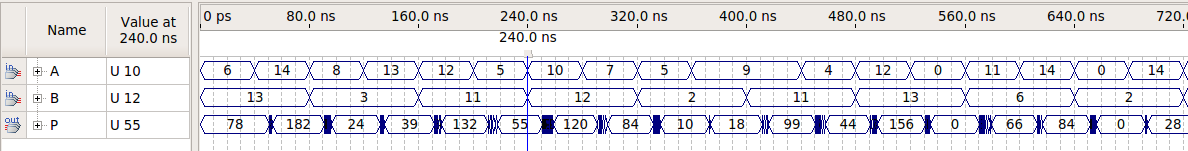

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo. Use a função Randon Value em A e B, e salve com o nome TesteMultiplicador4bits.vwf.

- Note que os bits das entradas e saídas estão agrupados em ordem reversa e definidos como RADIX = "Decimal sem sinal"

- Indique que o QSIM será usado na simulação [Simulation > Options > (x) Quartus II Simulator > OK > OK]

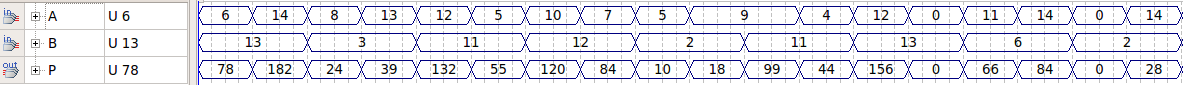

- Faça a simulação funcional do circuito lógico usando o sinal criado [Simulation > Run Functional Simulation]

- O resultado da simulação deve corresponder a um somador completo.

3 Análise dos resultados

- Analise os resultados preenchendo a tabela abaixo, e conferindo em uma calculadora:

| Entradas | Saídas | x | Entradas | Saídas | ||

|---|---|---|---|---|---|---|

| A | B | P | x | A | B | P |

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

4 Simulação Temporal com o QSIM

- Compile o circuito [Processing > Start Compilation] > após alguns minutos [OK]. Confira o [Compilation Report], verificando que o circuito correto foi compilado e anote o número de elementos lógicos e o total de pinos (16 -> 4 entradas A, 4 entradas B, 8 saídas P).

- Abra o arquivo TesteMultiplicador4bits.vwf e faça a simulação temporal do circuito lógico usando o sinal anteriormente já criado [Simulation > Run Timing Simulation]

- O resultado da simulação deve corresponder a um multiplicador de 4 bits com gliches e um atraso no sinal de saída.

- QUESTIONÁRIO

- Identifique as diferenças entre os sinais gerados na simulação funcional e na simulação temporal.

- Como este tipo de multiplicador deveria ser utilizado? Existe algum restrição quanto ao tipo de número a ser utilizado? Considere inteiros com sinal e sem sinal.

- Meça o atraso do resultado em relação a entrada? Considere a resposta após o término dos gliches e tempos de propagação nas portas e conexões.

- Determine o atraso para 4 valores diferentes de multiplicação. Existem diferença nos atrasos dessas operações? Por que esse atraso acontece?

- Quantas multiplicações por segundo o circuito pode realizar? Considere que uma nova multiplicação só poderá ser feita após obtido o resultado no pior caso.

- De que outra forma a mesma multiplicação poderia ser feita?