EDI018702 2019 2 AULA04: mudanças entre as edições

Criou página com ' ----- link=EDI018702_2019_2_AULA03 link=EDI018702_2019_2#Aulas link=EDI018702_2019_2_AULA05' |

Sem resumo de edição |

||

| Linha 1: | Linha 1: | ||

=Laboratório 1= | |||

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabMIC (sala 104) pela tarde entre '''13h30min e 15h20min''' com a Turma 1 e entre 15h40min às 17h30min com a Turma 2'''. O experimento está dividido em duas etapas, sendo que na primeira parte você vai testar o funcionamento de um Latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. Na segunda etapa você vai testar o funcionamento dos flip-flops tipo D na configuração mestre-escravo, comprovando a teoria envolvida. | |||

==Parte I - Latch RS== | |||

;Objetivo: | |||

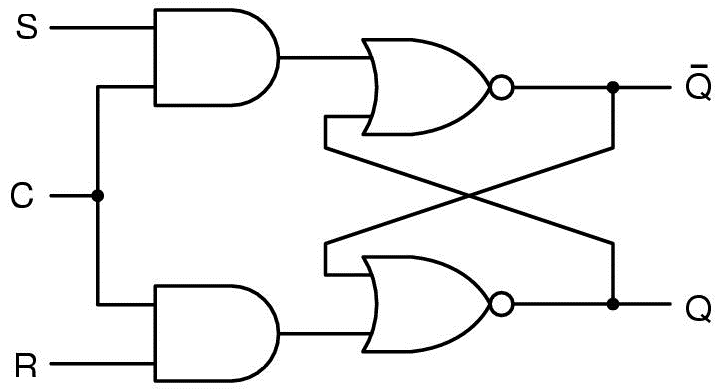

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1. | |||

[[Imagem:fig4_DIG222802.png|center|300px]] | |||

<center> | |||

Figura 1 - Latch RS controlado. | |||

{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | |||

|+'''Tabela Verdade''' | |||

|- | |||

! style="background:#F7D358; color:#151515; width: 20px;" | C | |||

! style="background:#F7D358; color:#151515; width: 20px;" | R | |||

! style="background:#F7D358; color:#151515; width: 20px;" | S | |||

! style="background:#F7D358; color:#151515; width: 20px;" | Q | |||

|- | |||

| 0 | |||

| X | |||

| X | |||

| Qa | |||

|- | |||

| 1 | |||

| 0 | |||

| 0 | |||

| Qa | |||

|- | |||

| 1 | |||

| 0 | |||

| 1 | |||

| 1 | |||

|- | |||

| 1 | |||

| 1 | |||

| 0 | |||

| 0 | |||

|- | |||

| 1 | |||

| 1 | |||

| 1 | |||

|proibido | |||

|} | |||

[*]Qa: saída do estado anterior. | |||

</center> | |||

==Procedimento== | |||

#Formar até 10 equipes com 2 alunos; | |||

#Desenhar as ligações utilizando o esquemático dos CIs; | |||

#Montar o circuito na banca digital, os CIs devem ficar com o chanfro voltado para cima; | |||

## Fazer a ligação de VCC e GND; | |||

## Fazer a ligação entre as portas lógicas dos circuitos integrados; | |||

## Fazer a ligação de R, S e C com chaves seletoras; | |||

## Fazer a ligação das Saídas Q e Q\ aos LEDs; | |||

#Testar a tabela verdade. | |||

==Parte II - Mestre-escravo== | |||

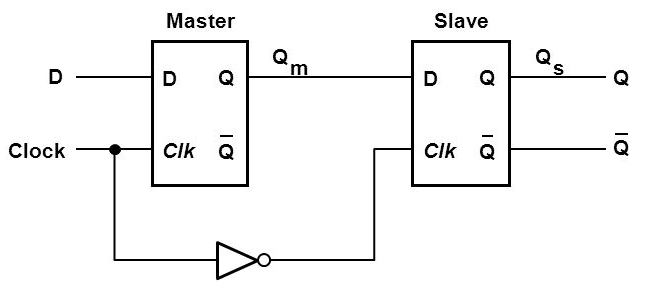

;Objetivo: Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 2. | |||

[[Imagem:fig6_DIG222802.png|center|400px]] | |||

<center> | |||

Figura 2 - Flip-flop tipo D na configuração mestre–escravo. | |||

{| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | |||

|+'''FF tipo D''' | |||

|- | |||

! style="background:#F7D358; color:#151515; width: 20px;" | D | |||

! style="background:#F7D358; color:#151515; width: 20px;" | Q | |||

! style="background:#F7D358; color:#151515; width: 20px;" | Q\ | |||

|- | |||

| 0 | |||

| 0 | |||

| 1 | |||

|- | |||

| 1 | |||

| 1 | |||

| 0 | |||

|} | |||

</center> | |||

==Procedimento== | |||

#Mesmas equipes; | |||

#Desenhar as ligações utilizando o esquemático dos CIs; | |||

#Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima; | |||

## Fazer a ligação de VCC e GND | |||

## Fazer a ligação de PRE e CLR nas chaves seletoras. | |||

## Fazer a ligação entre as FF passando pela inversora | |||

## Fazer a ligação de D e Clock com chaves seletoras | |||

## Fazer a ligação das Saídas Qm e Qs aos LEDs | |||

#Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave). | |||

#Ligar o '''clock''' a uma frequência de 1Hz (se estiver disponível) e ver o que acontece. | |||

=Material Utilizado= | |||

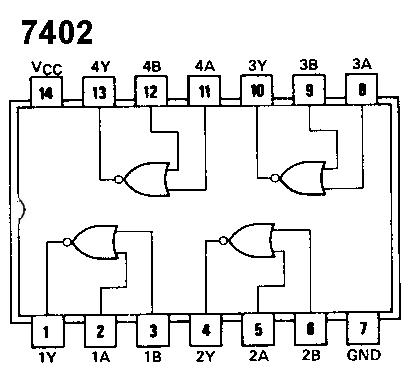

#CI 7402 (NOR) (Figura 3) | |||

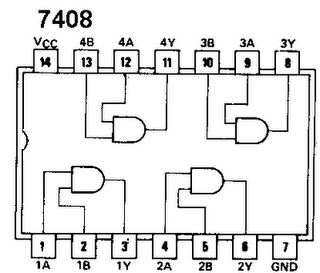

#CI 7408 (AND) (Figura 4) | |||

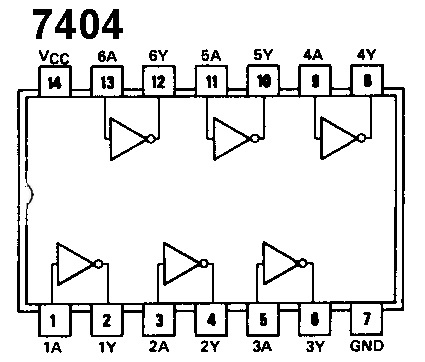

#CI 7404 (INV) (Figura 5) | |||

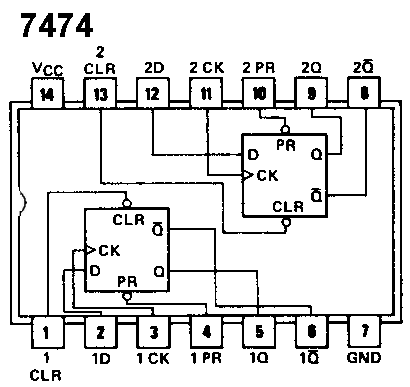

#CI 7474 (FF tipo D) (Figura 6) | |||

#fios diversos | |||

#bancada digital | |||

#alicates | |||

=Esquemáticos dos CIs= | |||

[[Imagem:CI_7402.png|center|250px]] | |||

<center> | |||

Figura 3 - Esquemático do CI 7402 - Portas NOR. | |||

</center> | |||

[[Imagem:CI_7408.png|center|250px]] | |||

<center> | |||

Figura 4 - Esquemático do CI 7408 - Portas AND. | |||

</center> | |||

[[Imagem:CI_7404.png|center|250px]] | |||

<center> | |||

Figura 5 - Esquemático do CI 7404 - Portas Inversoras. | |||

</center> | |||

[[Imagem:CI_7474.png|center|250px]] | |||

<center> | |||

Figura 6 - Esquemático do CI 7474 - Dois FF tipo D. | |||

</center> | |||

=Relatório= | |||

O relatório deverá ser entregue até o dia da primeira avaliação (AP1). O relatório deve ser enviado por meio digital no formato PDF para o endereço '''douglasars@gmail.com'''. | |||

<blockquote style="background: #FFEEFF; border: 1px solid red; margin-left: 0px; margin-right: 0px; padding: 1em;"> | |||

Nota 1: Entende-se por ser entregue até o dia da primeira avaliação às 23h59min. | |||

</blockquote> | |||

<blockquote style="background: #FFEEFF; border: 1px solid red; margin-left: 0px; margin-right: 0px; padding: 1em;"> | |||

Nota 2: Arquivos não entregues no prazo, ou que não estejam em formato PDF, ou ainda que não forem enviados para o referido email ''douglasars@gmail.com'', não serão corrigidos e terão nota 0 (zero). | |||

</blockquote> | |||

==Normas para elaboração do relatório== | |||

http://wiki.sj.ifsc.edu.br/images/9/9d/Modelo_Relat%C3%B3rio_aula_pratica_DouglasARS.pdf | |||

<blockquote style="background: #FFEEFF; border: 1px solid red; margin-left: 0px; margin-right: 0px; padding: 1em;"> | |||

Nota 3: Utilizem preferencialmente o LibreOffice Writer e exportem o arquivo PDF ao final (Arquivo >> Exportar como PDF). | |||

</blockquote> | |||

==Resultado da Correção REL1== | |||

(30 dias) | |||

Edição das 14h02min de 31 de julho de 2019

1 Laboratório 1

O primeiro experimento da turma de Digital 2 da Engenharia vai ser realizado na LabMIC (sala 104) pela tarde entre 13h30min e 15h20min com a Turma 1 e entre 15h40min às 17h30min com a Turma 2. O experimento está dividido em duas etapas, sendo que na primeira parte você vai testar o funcionamento de um Latch RS controlado feito a partir das portas lógicas AND (E) e NOR (NOU) comprovando a tabela verdade. Na segunda etapa você vai testar o funcionamento dos flip-flops tipo D na configuração mestre-escravo, comprovando a teoria envolvida.

1.1 Parte I - Latch RS

- Objetivo

Testar o funcionamento de um circuito latch RS controlado, feito a partir das portas lógicas AND (E) e NOR (NOU) como mostra a Figura 1.

Figura 1 - Latch RS controlado.

| C | R | S | Q |

|---|---|---|---|

| 0 | X | X | Qa |

| 1 | 0 | 0 | Qa |

| 1 | 0 | 1 | 1 |

| 1 | 1 | 0 | 0 |

| 1 | 1 | 1 | proibido |

[*]Qa: saída do estado anterior.

1.2 Procedimento

- Formar até 10 equipes com 2 alunos;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com o chanfro voltado para cima;

- Fazer a ligação de VCC e GND;

- Fazer a ligação entre as portas lógicas dos circuitos integrados;

- Fazer a ligação de R, S e C com chaves seletoras;

- Fazer a ligação das Saídas Q e Q\ aos LEDs;

- Testar a tabela verdade.

1.3 Parte II - Mestre-escravo

- Objetivo

- Testar o funcionamento de um Flip-flop D na configuração mestre–escravo a partir do CI 7474 e uma porta inversora. O circuito a ser montado pode ser visto na Figura 2.

Figura 2 - Flip-flop tipo D na configuração mestre–escravo.

| D | Q | Q\ |

|---|---|---|

| 0 | 0 | 1 |

| 1 | 1 | 0 |

1.4 Procedimento

- Mesmas equipes;

- Desenhar as ligações utilizando o esquemático dos CIs;

- Montar o circuito na banca digital, os CIs devem ficar com chanfro voltado para cima;

- Fazer a ligação de VCC e GND

- Fazer a ligação de PRE e CLR nas chaves seletoras.

- Fazer a ligação entre as FF passando pela inversora

- Fazer a ligação de D e Clock com chaves seletoras

- Fazer a ligação das Saídas Qm e Qs aos LEDs

- Construir a tabela verdade para Qm e Qs a partir da simulação dos pulsos de clock (ligar e desligar a chave).

- Ligar o clock a uma frequência de 1Hz (se estiver disponível) e ver o que acontece.

2 Material Utilizado

- CI 7402 (NOR) (Figura 3)

- CI 7408 (AND) (Figura 4)

- CI 7404 (INV) (Figura 5)

- CI 7474 (FF tipo D) (Figura 6)

- fios diversos

- bancada digital

- alicates

3 Esquemáticos dos CIs

Figura 3 - Esquemático do CI 7402 - Portas NOR.

Figura 4 - Esquemático do CI 7408 - Portas AND.

Figura 5 - Esquemático do CI 7404 - Portas Inversoras.

Figura 6 - Esquemático do CI 7474 - Dois FF tipo D.

4 Relatório

O relatório deverá ser entregue até o dia da primeira avaliação (AP1). O relatório deve ser enviado por meio digital no formato PDF para o endereço douglasars@gmail.com.

Nota 1: Entende-se por ser entregue até o dia da primeira avaliação às 23h59min.

Nota 2: Arquivos não entregues no prazo, ou que não estejam em formato PDF, ou ainda que não forem enviados para o referido email douglasars@gmail.com, não serão corrigidos e terão nota 0 (zero).

4.1 Normas para elaboração do relatório

http://wiki.sj.ifsc.edu.br/images/9/9d/Modelo_Relat%C3%B3rio_aula_pratica_DouglasARS.pdf

Nota 3: Utilizem preferencialmente o LibreOffice Writer e exportem o arquivo PDF ao final (Arquivo >> Exportar como PDF).

4.2 Resultado da Correção REL1

(30 dias)