Oficina NCO e Filtros digitais: mudanças entre as edições

Ir para navegação

Ir para pesquisar

Sem resumo de edição |

Sem resumo de edição |

||

| Linha 3: | Linha 3: | ||

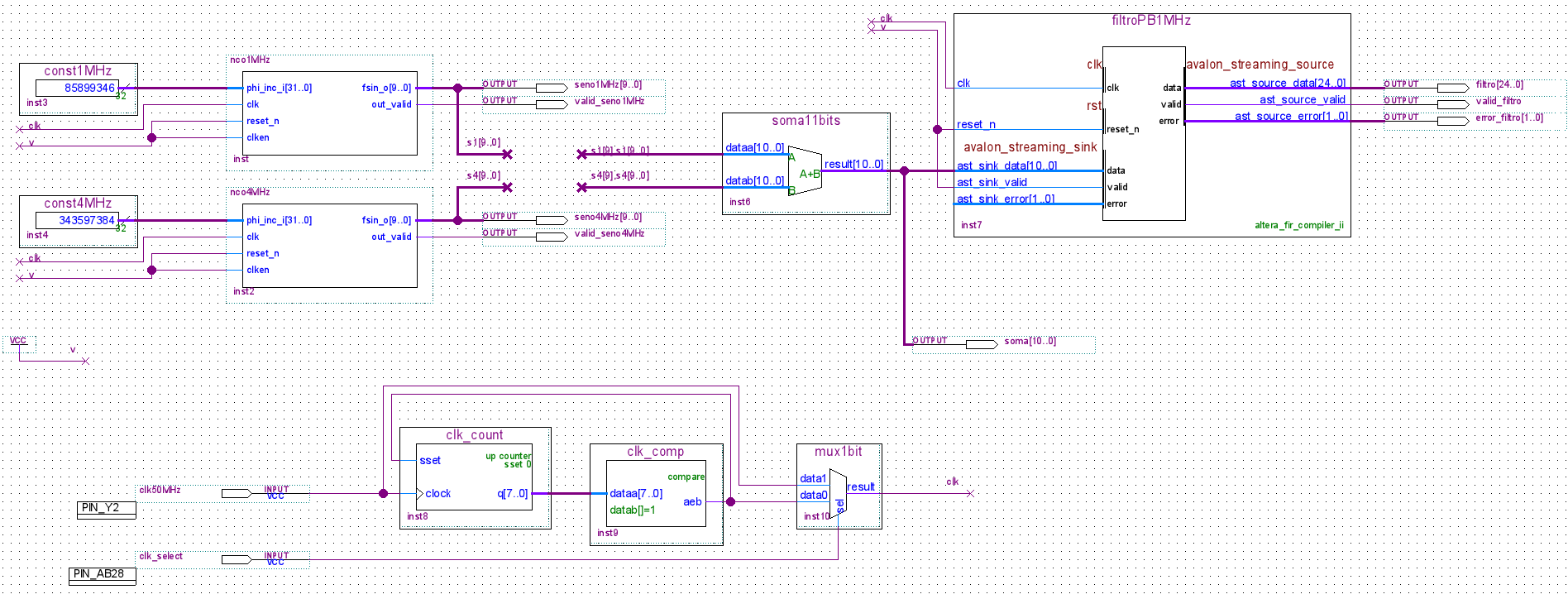

[[Imagem:PJI29008-OficinaSistema.png|thumb|Sistema desenvolvido|1200px|center]] | [[Imagem:PJI29008-OficinaSistema.png|thumb|Sistema desenvolvido|1200px|center]] | ||

<br style="clear:both;"> | <br style="clear:both;"> | ||

=== Geração dos sinais senoidais === | |||

Edição das 17h41min de 13 de março de 2017

Esta página traz um roteiro para a geração de sinais senoidais e a construção de filtros digitais em FPGAs Altera, usando o Quartus II. O sistema criado (figura abaixo) gera sinais senoidais de 1 MHz e 4 MHz, soma os dois sinais e realiza uma filtragem passa baixas, visando manter apenas o sinal de 1 MHz. Está prevista a construção de um multiplexador e de um divisor de clock. Todos os blocos utilizaram a ferramenta nativa do Quartus II, o MegaWizard Plug-In Manager.