Mudanças entre as edições de "DLP29006-Engtelecom (Diário) - Prof. Marcos Moecke"

Ir para navegação

Ir para pesquisar

| Linha 286: | Linha 286: | ||

:* Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops | :* Modifique o circuito do flip-flop para que ele passe a ter 4 flip-flops | ||

{{fig|2.5|RTL 4 FF| RTL_4FF.png| 400 px |}} | {{fig|2.5|RTL 4 FF| RTL_4FF.png| 400 px |}} | ||

| − | |||

| − | + | ====ATUAL==== | |

| − | ;Aula 7 ( | + | ;Aula 7 (19 abr.): |

* Uso de alguns sites auxiliares para a programação em VHDL: | * Uso de alguns sites auxiliares para a programação em VHDL: | ||

:*[[Preparando para gravar o circuito lógico no FPGA]] | :*[[Preparando para gravar o circuito lógico no FPGA]] | ||

| Linha 295: | Linha 294: | ||

:*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | :*[http://g2384.github.io/work/VHDLformatter.html VHDL Beautifier, Formatter] - para formatar automaticamente um código VHDL. | ||

:*[[Media:Quartus_II_Simulation.pdf | Tutorial do QSIM - Introduction to Simulation of VHDL Designs]] da ALTERA. | :*[[Media:Quartus_II_Simulation.pdf | Tutorial do QSIM - Introduction to Simulation of VHDL Designs]] da ALTERA. | ||

| − | *Exemplo de um | + | |

| − | + | *Exemplo de um Circuito para cálculo da '''distância de Hamming'''. | |

:*[[Medição de tempos de propagação em circuitos combinacionais]] | :*[[Medição de tempos de propagação em circuitos combinacionais]] | ||

| + | :*[https://wiki.sj.ifsc.edu.br/index.php/Medi%C3%A7%C3%A3o_de_tempos_de_propaga%C3%A7%C3%A3o_em_circuitos_combinacionais#Inserindo_restri.C3.A7.C3.B5es_de_atraso_m.C3.A1ximo_para_o_compilador Inserindo restrições de atraso máximo para o compilador] | ||

| + | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| + | *Exemplo de um '''contador''' em VHDL. [https://en.wikipedia.org/wiki/VHDL#Example:_a_counter COUNTER] na página de VHDL da Wikipedia. | ||

| + | :*[[Restringir a frequencia máxima de clock no Quartus II]] | ||

:* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | :* Objetivos: Copiar e colar o código no Quartus; diferença entre analise e síntese e compilação; observar o RTL (usar UNGROUP); simulação funcional e simulação temporal; observar os atrasos de propagação na simulação temporal. | ||

| − | *Revisitando o | + | *Exemplo do banco de 4 flip-flops |

| + | :*Revisitando o básico de simulação funcional e temporal com o QSIM. | ||

:*Realize as simulações funcional e temporal do circuito '''Flip-Flop4''' ou '''Counter''' usando o QSIM. | :*Realize as simulações funcional e temporal do circuito '''Flip-Flop4''' ou '''Counter''' usando o QSIM. | ||

| Linha 308: | Linha 312: | ||

{{fig|2.7|Simulação Temporal de 4 FF 100ns| SIM2_4FF.png| 800 px |}} | {{fig|2.7|Simulação Temporal de 4 FF 100ns| SIM2_4FF.png| 800 px |}} | ||

| − | Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. | + | :Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. |

''IMPORTANTE:'' Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo. | ''IMPORTANTE:'' Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo. | ||

| Linha 317: | Linha 321: | ||

*Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | *Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | ||

| − | |||

<big> Video motivational para apreender FPGA, VHDL [https://youtu.be/ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] </big> | <big> Video motivational para apreender FPGA, VHDL [https://youtu.be/ecyyZ6zTLic Microsoft's Bing* Intelligent Search with Intel® FPGAs] </big> | ||

| − | + | <!-- | |

| − | |||

| − | |||

| − | |||

| − | |||

;Aula 9 (3 nov): | ;Aula 9 (3 nov): | ||

* Uso das bibliotecas no VHDL. | * Uso das bibliotecas no VHDL. | ||

Edição das 15h20min de 19 de abril de 2022

Registro on-line das aulas

Unidade 1 - Introdução a disciplina

- 4 ENCONTROS

| Unidade 1 - Introdução a disciplina | ||||

|---|---|---|---|---|

|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

- 5 ENCONTROS

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

library library_name;

use library_name.package_name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is

[declarative_part]

begin

statement_part

end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

Exemplo de descrição de um multiplexador de 4 entradas entity mux_novo is

port

(

-- Input ports

X: in bit_vector (3 downto 0);

S : in bit_vector (1 downto 0);

-- Output ports

Y : out bit

);

end entity mux_novo;

-- Implementação com lógica pura

architecture v_logica_pura of mux_novo is

begin

Y <= (X(0) and (not S(1)) and (not S(0))) or

(X(1) and (not S(1)) and (S(0))) or

(X(2) and (S(1)) and (not S(0))) or

(X(3) and (S(1)) and (S(0)));

end architecture Logica_pura;

-- Implementação com WHEN ELSE

architecture v_WHEN of mux_novo is

begin

Y <= X(0) when S = "00" else

X(1) when S = "01" else

X(2) when S = "10" else

X(3);

end architecture v_WHEN;

-- Implementação com WITH SELECT

architecture v_WITH_SELECT of mux_novo is

begin

with S select

Y <= X(0) when "00", -- note o uso da ,

X(1) when "01",

X(2) when "10",

X(3) when others; -- note o uso de others, para todos os demais valores.

-- Não pode ser substituido por "11" mesmo que o signal seja bit_vector.

end architecture v_WITH_SELECT;

-- Implementação com IF ELSE

architecture v_IF_ELSE of mux_novo is

begin

-- Uma arquitetura vazia como essa é denominada de STUB,

-- Pode ser utilizada em um projeto durante para conferir as conexões externas.

-- Posteriormente a arquitetura será descrita.

end architecture v_IF_ELSET;

-- Design Unit que associa a architecture com a entity

configuration cfg_ifsc of mux_novo is

-- for v_WITH_SELECT end for;

for v_WHEN end for;

end configuration;

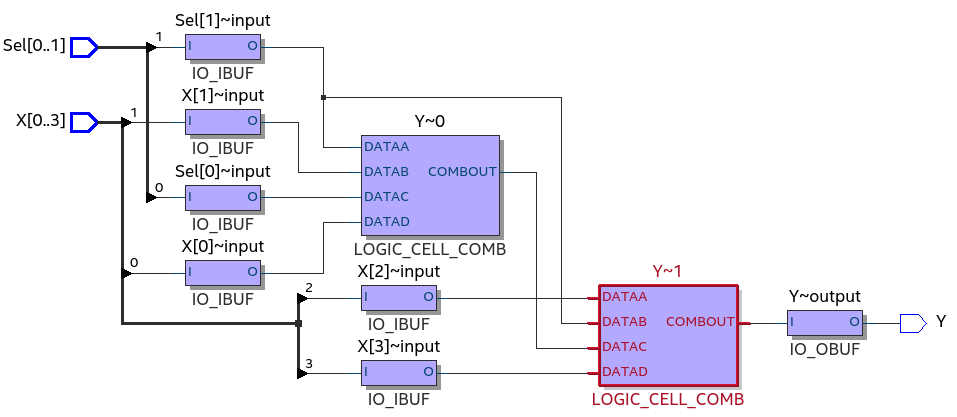

Figura 2.1 - Código RTL do mux 4x1 v_logica_pura  Figura 2.2 - Código RTL do mux 4x1 v_WHEN  Figura 2.3 - Código RTL do mux 4x1 v_WITH_SELECT

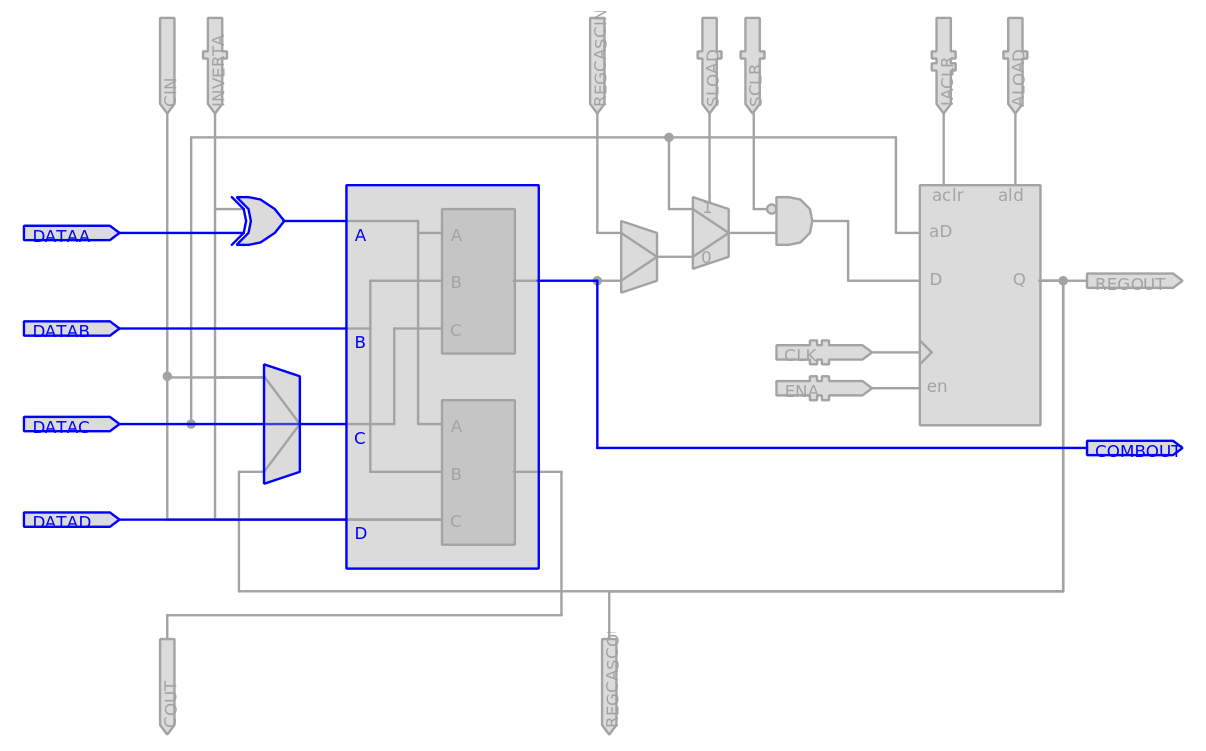

Figura 2.4 - Technology Map do mux 4x1 para a família Cyclone

Figura 2.5 - Elemento Lógico usado no mux 4x1 para a família Cyclone (node properties)

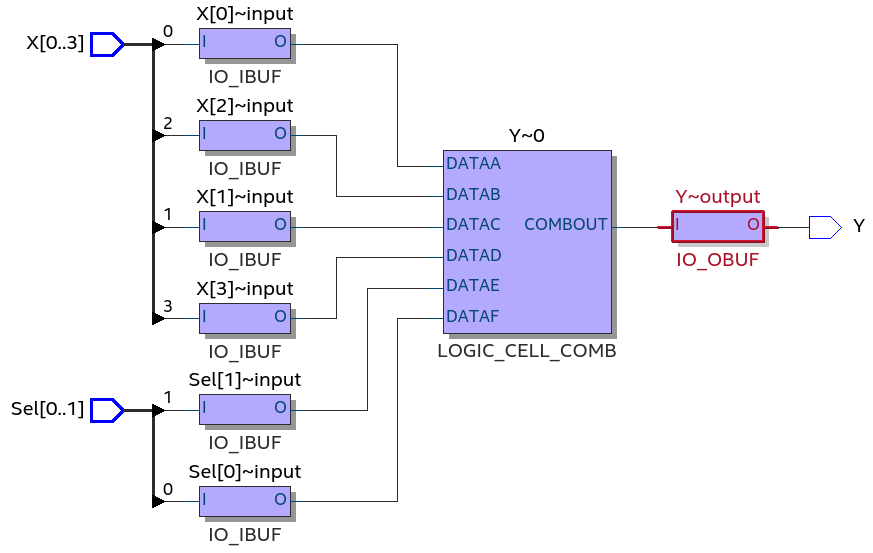

No entanto se utilizarmos um dispositivo FPGA da família Stratix III, que tem LUT tem 6 entradas, será necessário apenas 1 LE, conforme ilustrado a seguir. Figura 2.5 - Technology Map do mux 4x1 para a família Stratix III

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

Figura 2.2 - Código RTL do Exemplo 2.2

Figura 2.3 - Technology Map do Exemplo 2.2

Figura 2.4 - Chip Planner do Exemplo 2.2

Figura 2.5 - RTL 4 FF  ATUAL

Figura 2.6 - Simulação Funcional de 4 FF 100ns  Figura 2.7 - Simulação Temporal de 4 FF 100ns

IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possível verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

Video motivational para apreender FPGA, VHDL Microsoft's Bing* Intelligent Search with Intel® FPGAs |