Mudanças entre as edições de "Circuitos Lógicos Aritméticos"

Ir para navegação

Ir para pesquisar

| Linha 183: | Linha 183: | ||

==Análise dos resultados== | ==Análise dos resultados== | ||

*Identifique as diferenças entre os sinais gerados na simulação funcional e na simulação temporal. | *Identifique as diferenças entre os sinais gerados na simulação funcional e na simulação temporal. | ||

| − | * Como poderíamos fazer com que não ocorresse overflow nesse somador? Mostre esse procedimento | + | * Como poderíamos fazer com que não ocorresse overflow nesse somador? Mostre esse procedimento criando uma nova saída '''TesteSomador4bitsSemOverflow.vwf''' |

| + | |||

*Responda as seguintes questões:* | *Responda as seguintes questões:* | ||

;Como este tipo de somador deveria ser utilizado? | ;Como este tipo de somador deveria ser utilizado? | ||

Edição das 10h30min de 17 de fevereiro de 2021

Objetivos

- Construir testar um circuito somador completo (FA -full adder) a partir de portas lógicas usando o diagrama esquemático do QUARTUS II.

- Fazer a simulação funcional do circuito com o QSIM.

- Criar componentes após o teste e reutiliza-los em projetos maiores.

- Construir um somador de 4 bits usando os FA como componente.

- Construir um multiplicador de 4 bits usando os FA como componente.

- Construir um circuito que realiza o complemento de 2.

- Construir um somador/subtrator de 4 bits usando o somador de 4 bits e complemento de 2 como componentes. (TAREFA ADICIONAL PARA OS ALUNOS)

- Preparar o circuito para programação e implementação do hardware FPGA do kit DE2-115.

- Escrever relatório técnico do projeto seguindo as normas ABNT

Somador Completo

Diagrama Esquemático

- Crie uma pasta /home/aluno/somador.

- Abra o Quartus II e crie um novo projeto na pasta somador com nome FullAdder, utilizando a família family=Cyclone IV E com o dispositivo device=EP4CE115F29C7 ou Family = Cyclone IV E com dispositivo device = EP4CE30F23C7.

- Crie um novo diagrama esquemático (File >> New >> Block Diagram/Schematic File), conforme figura abaixo:

- Salve o arquivo como FullAdder.bdf.

- Faça a Análise e Síntese do projeto e tenha certeza que tudo esteja funcionando perfeitamente através da compilação do projeto.

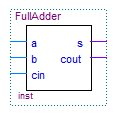

Criar o componente FullAdder

- Crie um simbolo para este circuito, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

- Note que um novo simbolo estará disponível para uso no diagrama esquemático com o nome FullAdder [Symbol >> Project >> FullAdder]

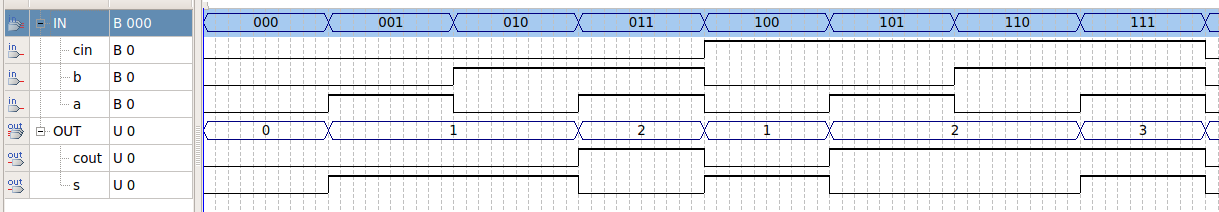

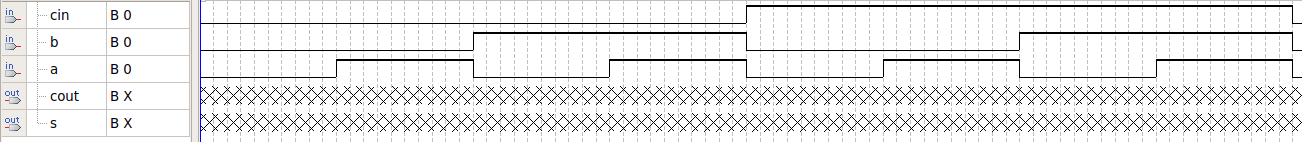

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF) (v 13.0 e 13.1).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

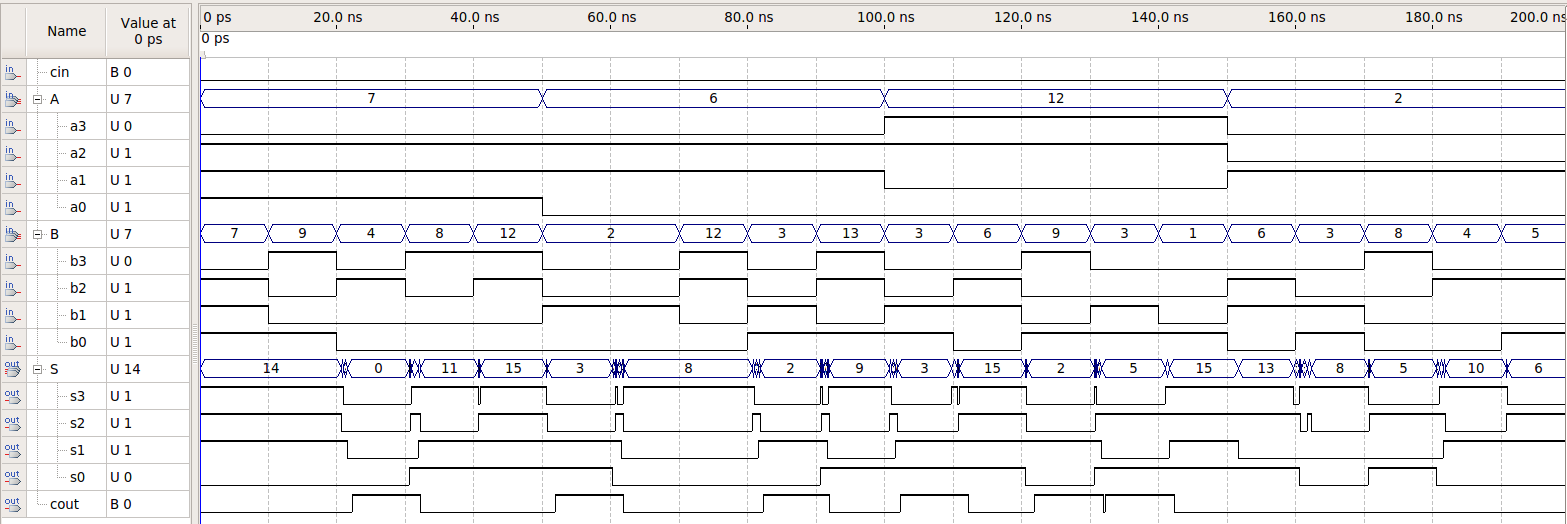

- Desenhe a forma de onda dos sinais de entrada conforme mostrado na figura abaixo, e salve com o nome TesteFA.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK] (v. 13.0)

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

- Note que os bits das entradas estão agrupados e definidos como RADIX "Binary". Para isso selecione os sinais [Edit > Grouping] [Group name = IN] > [Radix = Binary] > [OK].

- Note que os bits das saídas estão agrupados e definidos como RADIX = "Decimal sem sinal". Para isso selecione os sinais [Edit > Grouping] [Group name = OUT] > [Radix = Unsigned Decimal] > [OK].

Análise dos resultados

- Analise o resultado preenchendo a tabela-verdade abaixo:

| Entradas | Saídas | |||

|---|---|---|---|---|

| cin | a | b | s | cout |

| 0 | 0 | 0 | ||

| 0 | 0 | 1 | ||

| 0 | 1 | 0 | ||

| 0 | 1 | 1 | ||

| 1 | 0 | 0 | ||

| 1 | 0 | 1 | ||

| 1 | 1 | 0 | ||

| 1 | 1 | 1 | ||

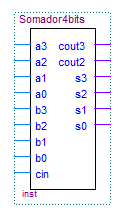

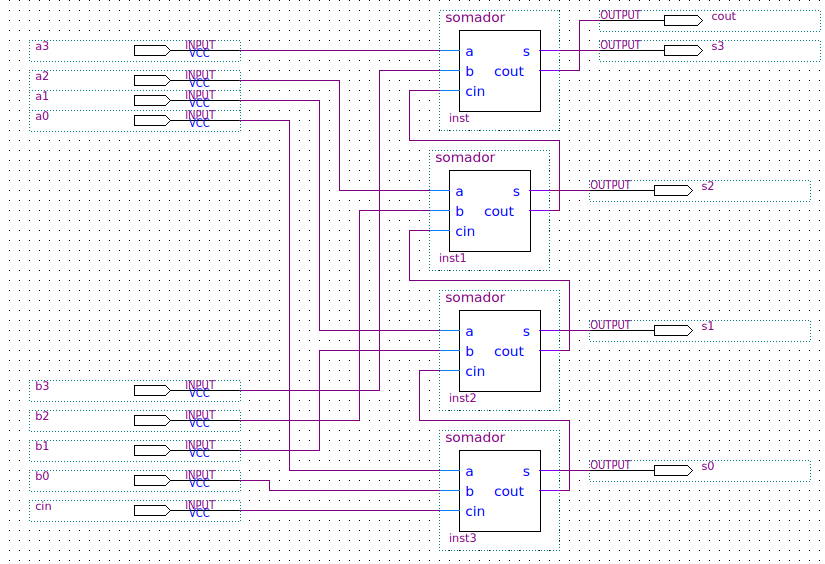

Somador de 4 bits

Diagrama Esquemático

- Crie um novo diagrama (File >> New >> Block Diagram/Schematic File) e insira o diagrama esquemático do somador completo, utilizando o componente FullAdder criado anteriormente.

- Salve o arquivo como Somador4bits.bdf na mesma pasta do somador.

- Mude o Top Level para este circuito (Aba Files >> tecla direita do mouse em Somador4bits >> Set as Top-Level Entity).

- Faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

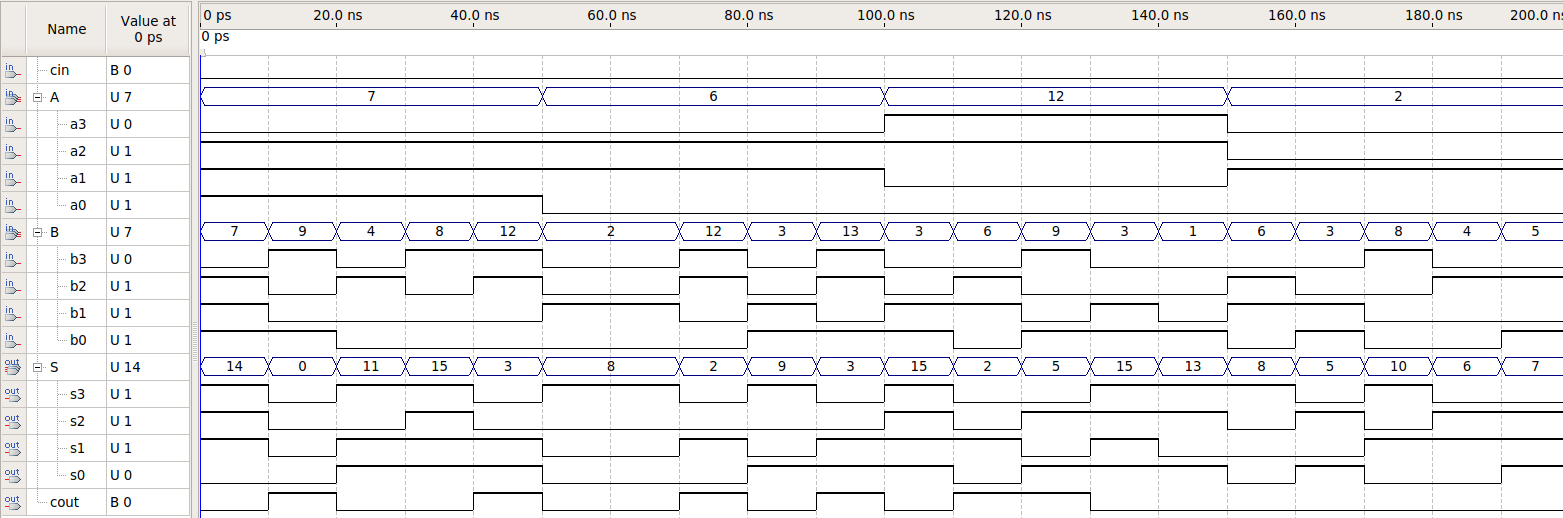

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 200 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

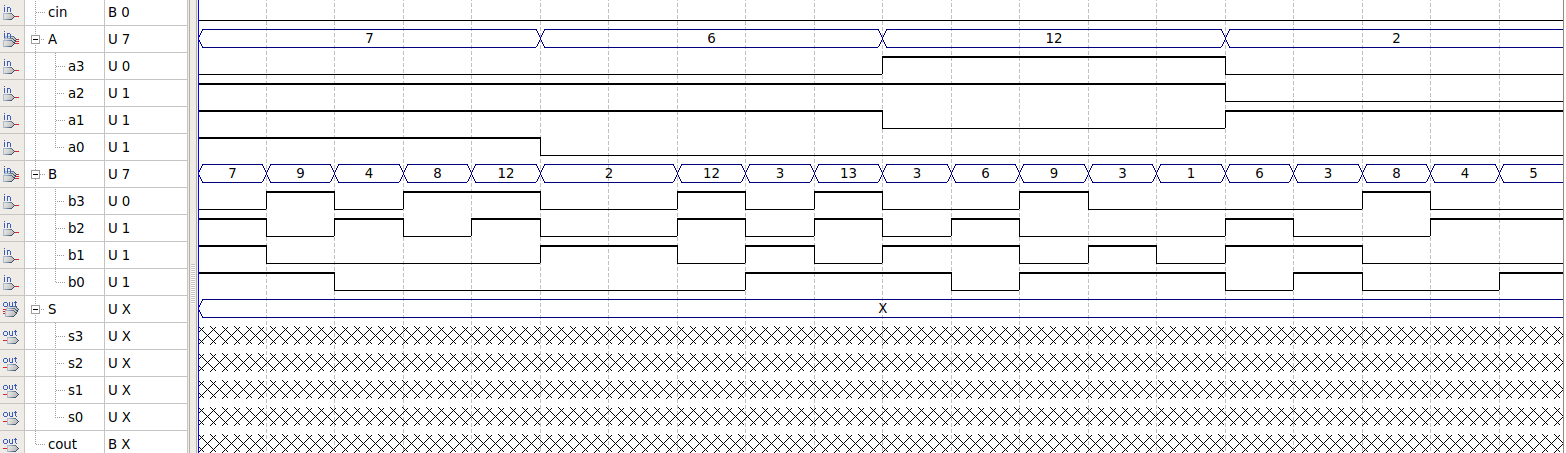

- Note que os bits das entradas e das saídas estão agrupados e definidos como RADIX "Unsigned Decimal". Para isso selecione os sinais a0, a1, a2, e a3 [Edit > Grouping] [Group name = A] > [Radix = Unsigned Decimal], b0, b1, b2 e b3 [Group name = B] > [Radix = Unsigned Decimal] e s0, s1, s2 e s3 [Group name = S] > [Radix = Unsigned Decimal]> [OK].

- Note que ao fazer este procedimento os bits estão provavelmente na ordem x0,x1,x2,x3. Isso implica que o simulador está interpretando o Vetor X como sendo x3 o LSB e x0 o MSB. Normalmente queremos que o x0 seja o LSB, então é necessário trocar a ordem. [Edit > Reverse Group or Bus Bit Order]

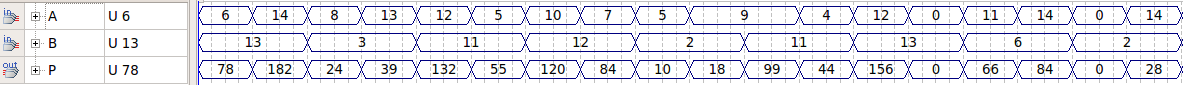

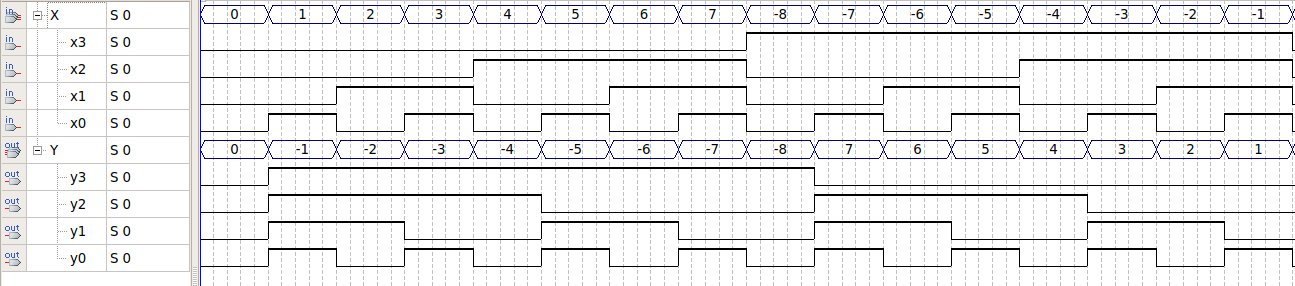

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A e B, e salve com o nome TesteSomador4bits.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

Análise dos resultados

- Analise os resultados preenchendo a tabela abaixo:

| Entradas | Saídas | |||

|---|---|---|---|---|

| cin | A | B | S | cout |

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

| . | ||||

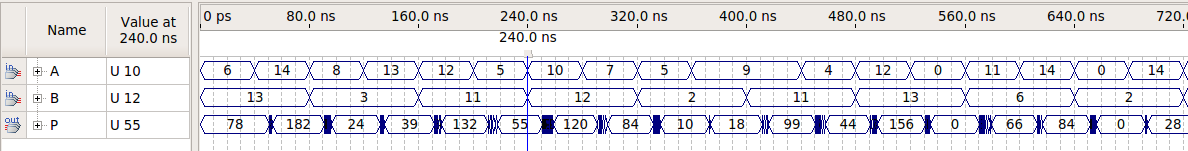

Simulação Temporal com o QSIM

- Mude a família lógica para que permita a simulação temporal (as famílias mais avançadas não admitem): Assignments >> Device >> Family: Cyclone II E e Available Devices: EP2C5AF256A7 >> OK

- Compile o circuito [Processing > Start Compilation] > após alguns minutos [OK]. Confira o [Compilation Report], verificando que o circuito e dispositivo corretos foram utilizados na compilação.

- Abra o arquivo TesteSomador4bits.vwf e faça a simulação temporal do circuito lógico usando o sinal anteriormente já criado (Simulation > Run Timing Simulation).

- O resultado da simulação deve corresponder a um somador completo com glitches e um atraso no sinal de saída.

- Dê zoom nos glitches e analise-os.

Análise dos resultados

- Identifique as diferenças entre os sinais gerados na simulação funcional e na simulação temporal.

- Como poderíamos fazer com que não ocorresse overflow nesse somador? Mostre esse procedimento criando uma nova saída TesteSomador4bitsSemOverflow.vwf

- Responda as seguintes questões:*

- Como este tipo de somador deveria ser utilizado?

- Meça o atraso do resultado em relação a entrada? Considere a resposta após o término dos gliches.

- Por que esse atraso acontece?

- Quantas somas por segundo o circuito pode realizar?

- Apresente alguma solução utilizar esse circuito mesmo com o atraso no resultado.

- Que tipo de outro circuito pode ser utilizado para fazer a soma de 4 bits?

Multiplicador de 4 bits

Diagrama Esquemático

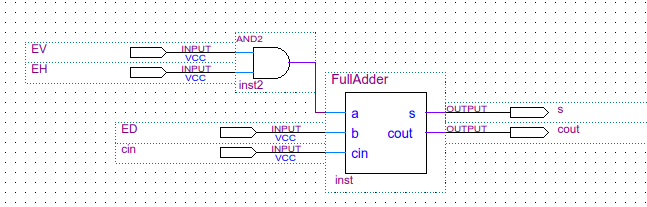

Abra o Quartus II e insira o diagrama esquemático do módulo básico do multiplicador, utilizando o componente FullAdder criado anteriormente.

- Salve o arquivo como ModuloBMultiplicador.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático do ModuloBMultiplicador > [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

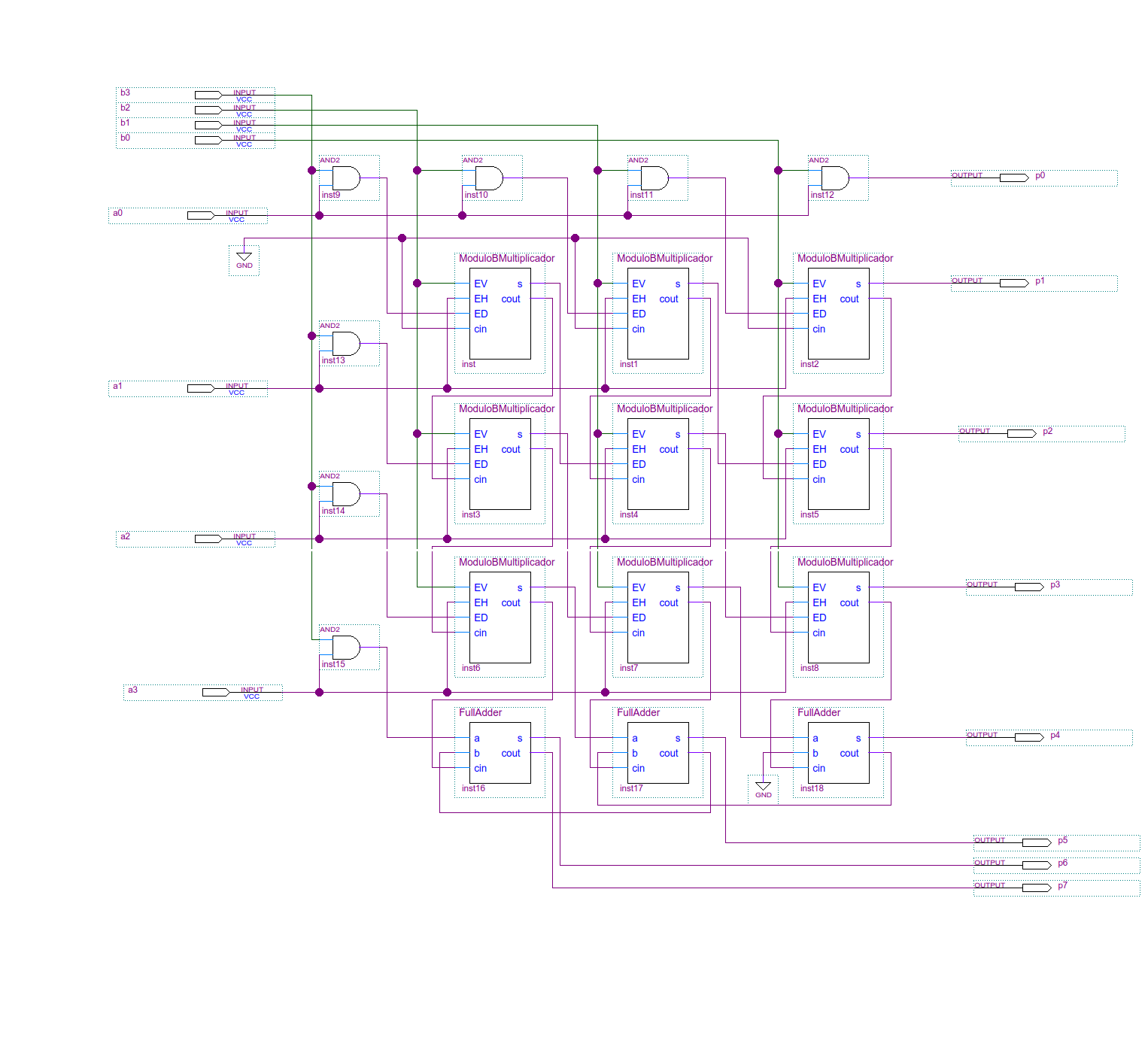

Abra um novo diagrama esquematico no Quartus II e insira o circuito digital abaixo utilizando os componentes FullAdder e ModuloBMultiplicador criados anteriormente.

- Salve o arquivo como Multiplicador4bits.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

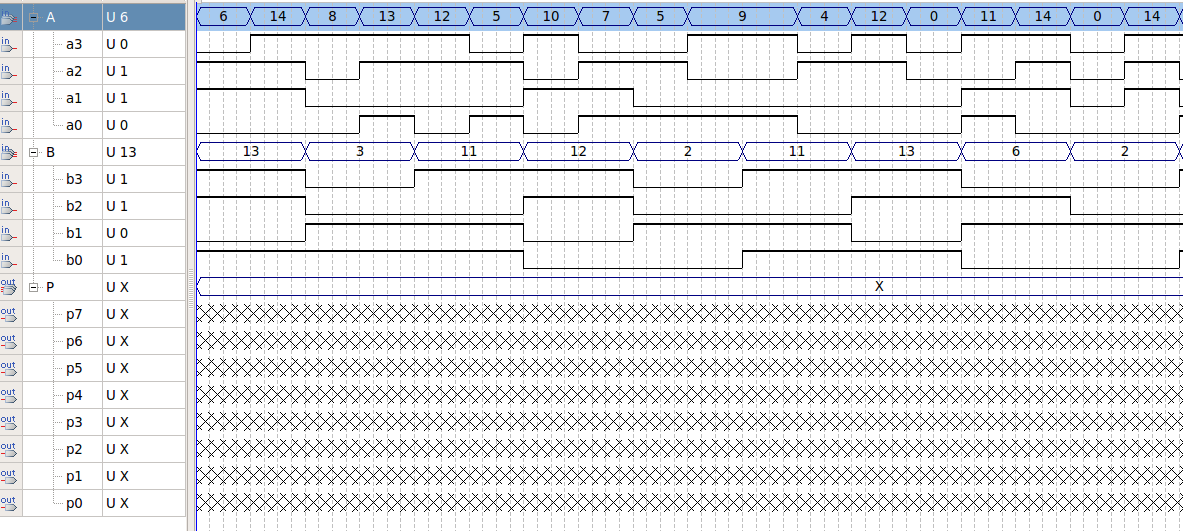

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A e B, e salve com o nome TesteMultiplicador4bits.vwf.

- Note que os bits das entradas e saídas estão agrupados em ordem reversa e definidos como RADIX = "Decimal sem sinal"

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

Análise dos resultados

- Analise os resultados preenchendo a tabela abaixo, e conferindo em uma calculadora:

| Entradas | Saídas | x | Entradas | Saídas | ||

|---|---|---|---|---|---|---|

| A | B | P | x | A | B | P |

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

| x | ||||||

Simulação Temporal com o QSIM

- Compile o circuito [Processing > Start Compilation] > após alguns minutos [OK]. Confira o [Compilation Report], verificando que o circuito correto foi compilado e anote o número de elementos lógicos e o total de pinos (16 -> 4 entradas A, 4 entradas B, 8 saidas P).

- Abra o arquivo TesteMultiplicador4bits.vwf e faça a simulação temporal do circuito lógico usando o sinal anteriormente já criado (Simulation > Run Timing Simulation)

- O resultado da simulação deve corresponder a um multiplicador de 4 bits com gliches e um atraso no sinal de saída.

Análise dos resultados

- Identifique as diferenças entre os sinais gerados na simulação funcional e na simulação temporal.

- Responda as seguintes questões:

- Como este tipo de multiplicar deveria ser utilizado?

- Meça o atraso do resultado em relação a entrada? Considere a resposta após o término dos gliches.

- Determine o atraso para 4 valores diferentes de multiplicação. Existem diferença nos atrasos dessas operações?

- Por que esse atraso acontece?

- Quantas multiplicações por segundo o circuito pode realizar?

- Compare o tempo do atraso do somador de 4 bits com o multiplicador de 4 bits.

- De que outra forma a mesma multiplicação poderia ser feita?

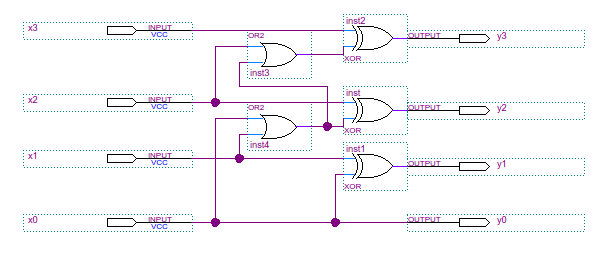

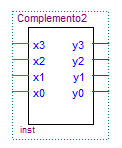

Complemento de 2

Diagrama Esquemático

Abra o Quartus II e insira o diagrama esquemático do módulo básico do complementador de 2.

- Salve o arquivo como Complemento2.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A e B, e salve com o nome TesteComplemento2.vwf.

- Note que os bits das entradas e saídas estão agrupados em ordem reversa e definidos como RADIX = "Decimal com sinal"

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

- O resultado da simulação deve corresponder a um somador completo.

Análise dos resultados

- Analise os resultados preenchendo a tabela abaixo, e conferindo se está correto:

| Entradas | Saídas | x | Entradas | Saídas | ||

|---|---|---|---|---|---|---|

| X >= 0 | Y | OK | x | X < 0 | Y | OK |

| 0 | x | |||||

| 1 | x | -1 | ||||

| 2 | x | -2 | ||||

| 3 | x | -3 | ||||

| 4 | x | -4 | ||||

| 5 | x | -5 | ||||

| 6 | x | -6 | ||||

| 7 | x | -7 | ||||

| 8 | x | -8 | ||||

- Responda as seguintes questões:

- Qual é o valor minimo e máximo que pode ser representado em complemento de 2 com 4 bits?

- Quais são as restrições de uso desse circuito?

- Qual o valor obtido quando colocamos um valor positivo na entrada?

- Qual o valor obtido quando colocamos um valor negativo na entrada?

- Se for inserido um inversor em cada saída qual é o resultado obtido? Como poderia ser chamado este circuito?

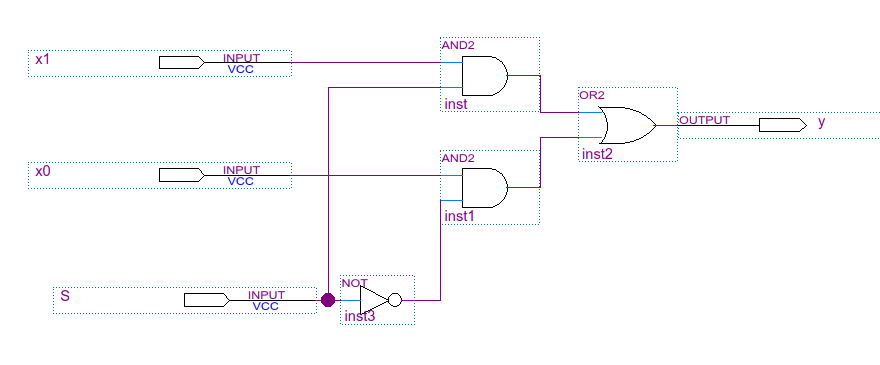

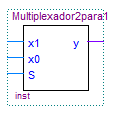

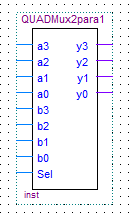

Multiplexador de 2 para 1

Diagrama Esquemático

Abra o Quartus II e insira o diagrama esquemático do módulo básico do complementador de 2.

- Salve o arquivo como Mux2para1.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

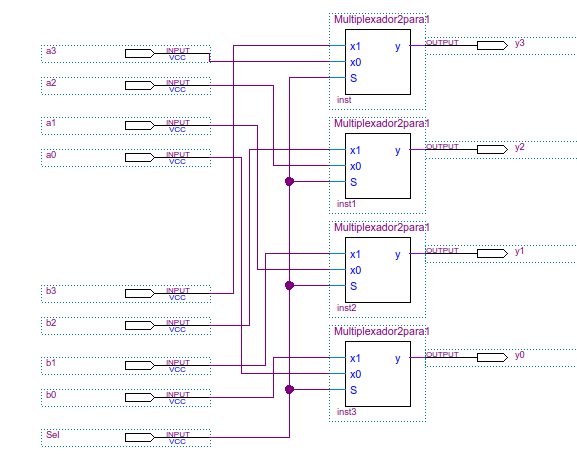

- Utilize 4 desses componentes para criar um multiplexador de 2 entradas para 1 saída de 4 bits.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

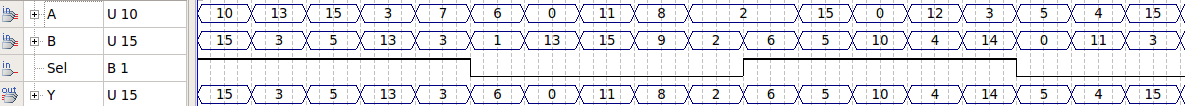

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A, B e Sel e salve com o nome QUADMux2para1.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

Análise dos resultados

- Verifique se o multiplexador está funcionando. Quando S = 0 => Y = x0, e quando S = 1 => Y = x1.

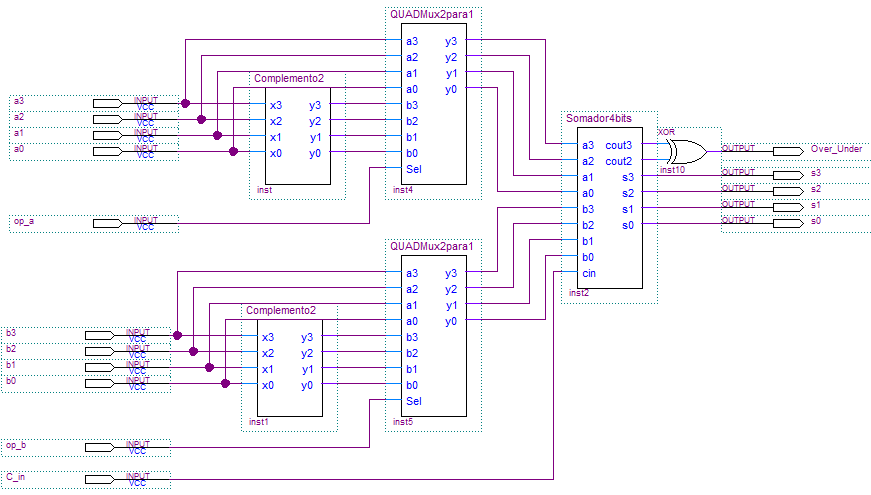

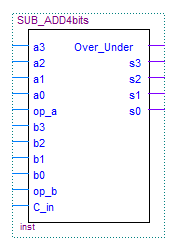

Circuito Somador e Substrator de 4 bits

Diagrama Esquemático

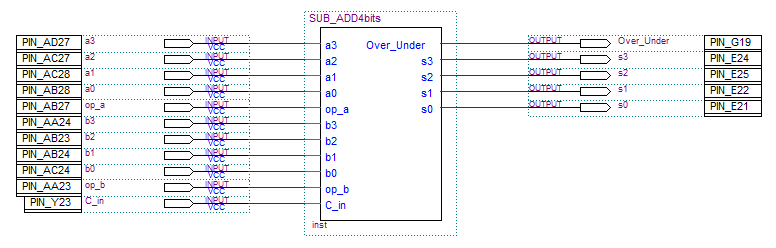

Utilizando os componentes anteriormente criados, insira o diagrama esquemático do circuito a seguir.

- Salve o arquivo como Sub_Add4bits.bdf na mesma pasta do PROJ2.

- Mude o Top Level para este circuito. Após isso faça a Análise e Síntese do projeto.

- Crie um simbolo para este módulo, selecionando na IDE do Quartus II o diagrama esquemático e [File > Create/Update > Create Symbol Files for Current File] > [Save] > [OK].

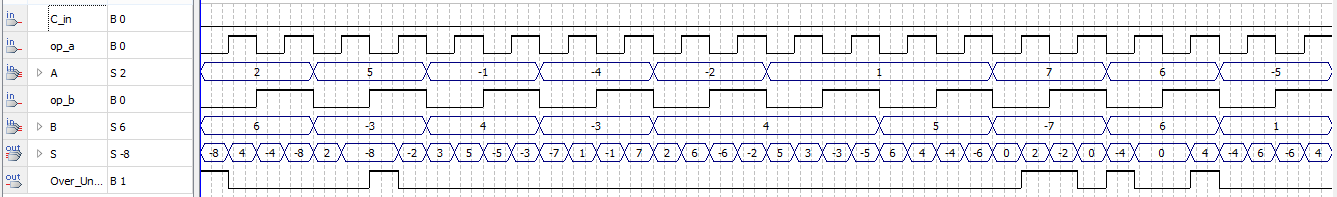

Simulação funcional com o QSIM

- Abra o editor de forma de onda do simulador QSIM (File > New > University Programa VWF).

- Defina o tempo de simulação (Edit > Set End Time ...) = 1000 ns.

- Importe todos os nós de lista do projeto (Edit > Insert > Insert Node or Bus) > [Node Finder] > [List] > [>>] > [OK] > [OK].

- Gere uma forma de onda dos sinais de entrada semelhante a mostrado na figura abaixo (Use a função [Randon Value] em A, B e Sel e salve com o nome Sub_Add4bits.vwf.

- Indique que o QSIM será usado na simulação (Simulation > Options > (x) Quartus II Simulator) > [OK] > [OK]

- Faça a simulação funcional do circuito lógico usando o sinal criado (Simulation > Run Functional Simulation)

Análise dos resultados

- Anote os resultados das operações de soma e subtração

| Entrada Carry | Entrada A | Entrada B | Saídas | |||

|---|---|---|---|---|---|---|

| C_in | Op_A | A | Op_B | B | Erro | Soma |

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

| . | ||||||

- Verifique se o circuito está funcionando corretamente.

- Responda as seguintes questões:

- Qual é o valor minimo e máximo que pode ser representado na saída do circuito sem que haja erro?

- Quais são as restrições de entrada no uso desse circuito?

- Qual a função da entrada op_a e op_b?

- Como interpretar o resultado da saída S do circuito quando a saída Over_Under está em 1?

Programação do FPGA e testes finais

Para programar o circuito lógico no FPGA, é necessário escolher um FPGA para a aplicação. Neste caso utilizaremos o kit DE2-115.

- Mude a família e dispositivo a ser usado (Assignments > Devices), [Family = Cyclone IV E] e selecione EP4CE115F29C7 ou ou Family = Cyclone IV E com dispositivo device = EP4CE30F23C7

- Defina como alta impedância o estado dos pinos não utilizados no projeto. (Assignments > Devices), [Device and Pin Options...], escolha a (Category=Unused Pins), e selecione Reserve all unused pins: As input tri-stated. [OK].

- Selecione as interfaces de entrada e saída que deseja no kit educacional disponível, utilizando 4 chaves para cada entrada de dado A (a0-3) e B (b0-3), 2 chaves para os op_A e Op_B, 1 chave para o C_in. Para as saídas utilize 4 leds para o dado S (s0-3) e um led para a indicação de erro.

- Entradas

- a0 -> PIN_AB28

- a1 -> PIN_AC28

- a2 -> PIN_AC27

- a3 -> PIN_AD27

- op_A -> PIN_AB27

- b0 -> PIN_AC24

- b1 -> PIN_AB24

- b2 -> PIN_AB23

- b3 -> PIN_AA24

- op_B -> PIN_AA23

- C_in -> PIN_Y23

- Saídas

- s0 -> PIN_E21

- s1 -> PIN_E22

- s2 -> PIN_E25

- s3 -> PIN_E24

- erro -> PIN_G19

- Para ver as pinagens completa das Interfaces de entrada e saída da DE2-115 no Manual.

- Compile o projeto. Note que agora a numeração dos pinos aparece no diagrama esquemático.