Mudanças entre as edições de "DLP29006-Engtelecom(2018-1) - Prof. Marcos Moecke"

| Linha 700: | Linha 700: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 5 - Código Sequencial}} |

===Unidade 5 - Código Sequencial=== | ===Unidade 5 - Código Sequencial=== | ||

| Linha 905: | Linha 905: | ||

{{collapse top| expand = true | Unidade 6 - Projeto a nível de Sistema}} | {{collapse top| expand = true | Unidade 6 - Projeto a nível de Sistema}} | ||

===Unidade 6 - Projeto a nível de Sistema=== | ===Unidade 6 - Projeto a nível de Sistema=== | ||

| − | + | ; Aula 27 ( ): | |

| − | ; Aula 27 ( | ||

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| Linha 916: | Linha 915: | ||

:* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | ||

| − | ; Aula 28 ( | + | ; Aula 28 ( ): |

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | :* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | ||

| Linha 924: | Linha 923: | ||

:* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula 29,30 ( | + | ;Aula 29,30 ( ): |

*Código Sequencial. | *Código Sequencial. | ||

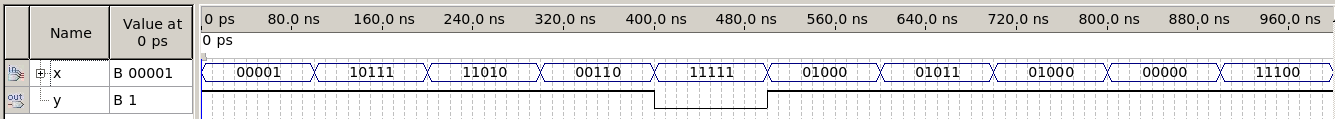

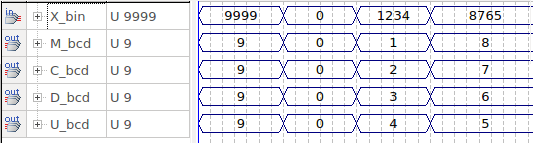

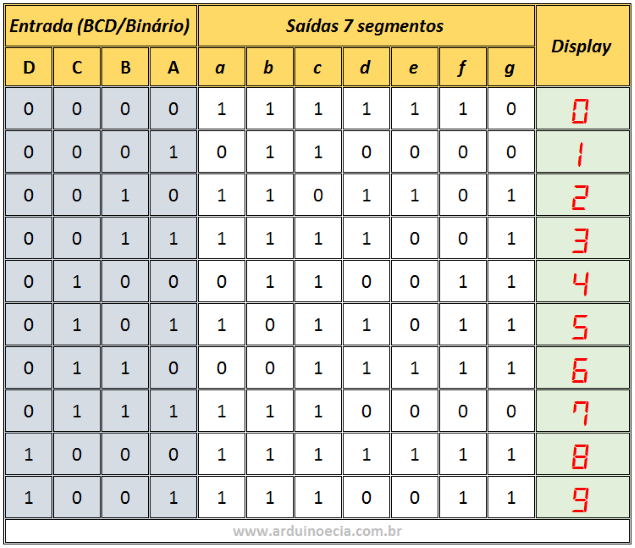

* Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando um COMPONENT contador BCD de 00 a 99. Instancie 3 COMPONENTES para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ser implementados com um COMPONENT "bin2ssd" que converte o número 0 a 9 em bits do código SSD. | * Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando um COMPONENT contador BCD de 00 a 99. Instancie 3 COMPONENTES para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ser implementados com um COMPONENT "bin2ssd" que converte o número 0 a 9 em bits do código SSD. | ||

| Linha 931: | Linha 930: | ||

| − | ; Aula 30 ( | + | ; Aula 30 ( ): |

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* Uso da instrução '''CONFIGURATION'''. | :* Uso da instrução '''CONFIGURATION'''. | ||

::* Ligação direta: ARCHITECTURE-ENTITY. | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| + | <!-- | ||

::*Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada. | ::*Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada. | ||

| Linha 1 050: | Linha 1 050: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | ===Unidade | + | {{collapse top| expand=true | Unidade 7 - Testbench}} |

| + | ===Unidade 7 - Testbench=== | ||

; Aula 33 (13 jun): | ; Aula 33 (13 jun): | ||

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| Linha 1 167: | Linha 1 168: | ||

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

:* Tempo livre para a resolução do Exercicio proposto. | :* Tempo livre para a resolução do Exercicio proposto. | ||

| + | --> | ||

| + | ;Aulas 34 a 36 | ||

| + | *Tempo livre para a realização do projeto final. | ||

| + | {{collapse bottom}} | ||

| − | ===Unidade 8=== | + | {{collapse top| expand=true | Unidade 8 - Maquinas de Estado Finitas}} |

| − | ; Aula 38 ( | + | ===Unidade 8 - Maquinas de Estado Finitas=== |

| + | ; Aula 38 ( ): | ||

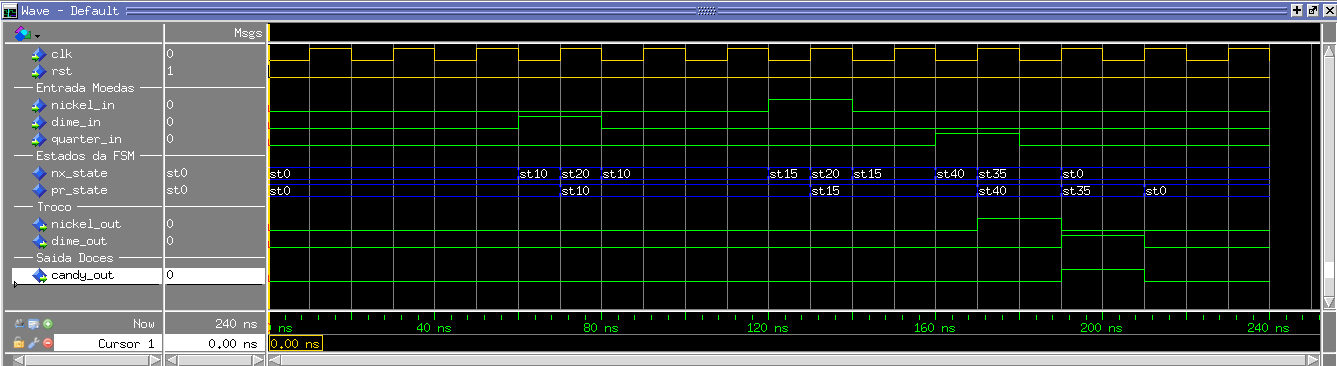

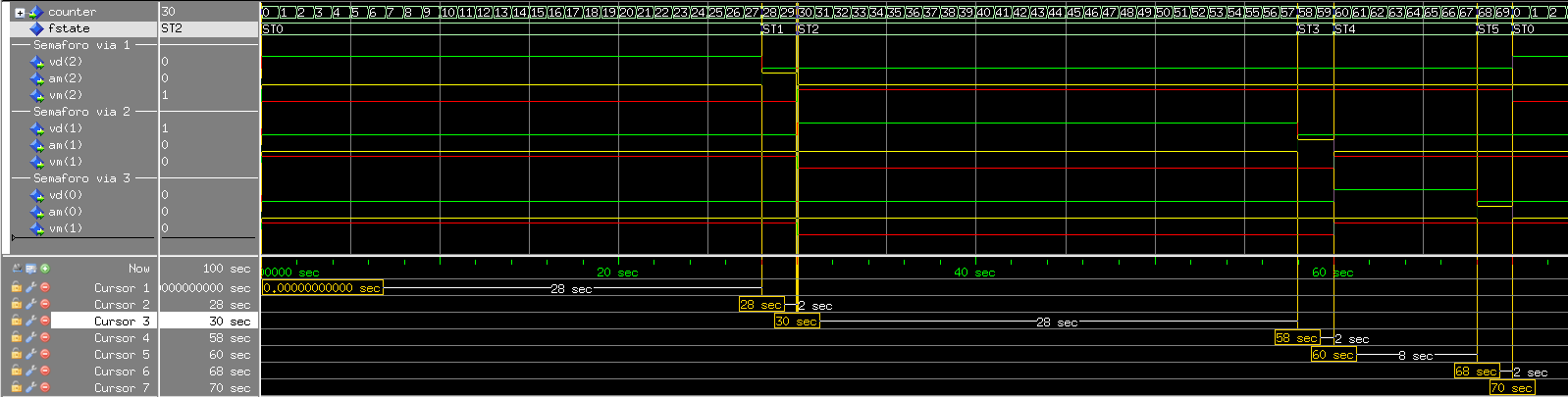

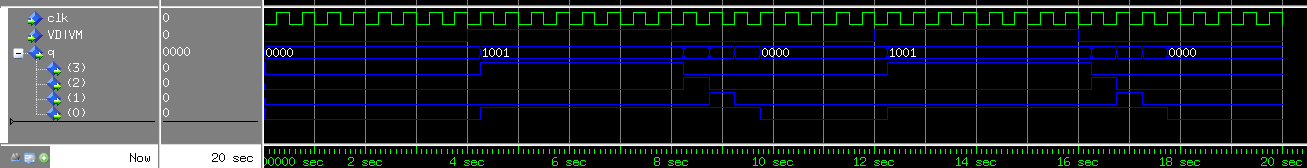

*Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

:* O que é uma FSM - Finite State Machine | :* O que é uma FSM - Finite State Machine | ||

| Linha 1 247: | Linha 1 253: | ||

:* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| − | + | <!-- | |

; Aula 40 (12 Jun): | ; Aula 40 (12 Jun): | ||

* Avaliação A2 | * Avaliação A2 | ||

| Linha 1 260: | Linha 1 266: | ||

;Aula 42 a 46 (20 Jun a 30 Jun): | ;Aula 42 a 46 (20 Jun a 30 Jun): | ||

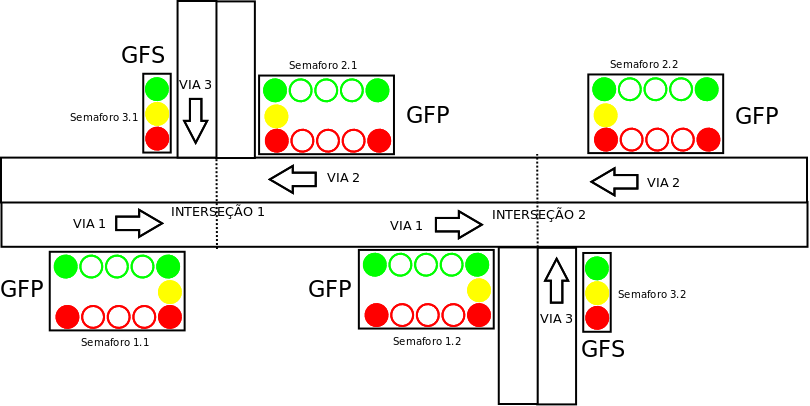

* Projeto Final - Sistema de controle de tráfego | * Projeto Final - Sistema de controle de tráfego | ||

| − | :* trabalho desenvolvido em equipes | + | :* trabalho desenvolvido em equipes |

| − | :* durante as aulas o professor | + | :* durante as aulas o professor está disponível para o esclarecimento de dúvidas e orienta o trabalho |

| − | + | <!-- | |

;Aula 47 (4 Jul): | ;Aula 47 (4 Jul): | ||

* Avaliação de Recuperação de A1 e A2. | * Avaliação de Recuperação de A1 e A2. | ||

Edição das 16h32min de 20 de junho de 2018

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ver pag. 60 a 73 de [2]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY operadores IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

div: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

);

END ENTITY;

ARCHITECTURE type_conv_arch OF operadores IS

BEGIN

-- Inserir o código e definir o tamanho das saidas.

END ARCHITECTURE;

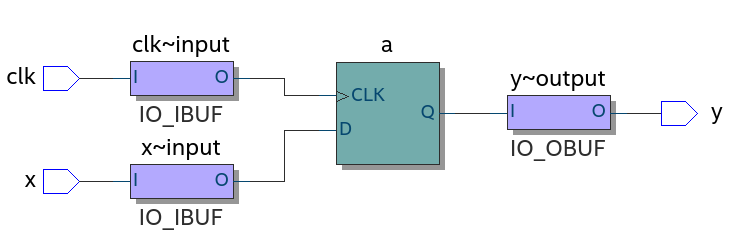

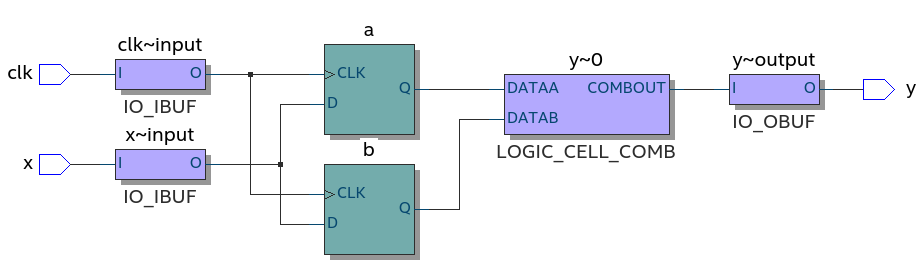

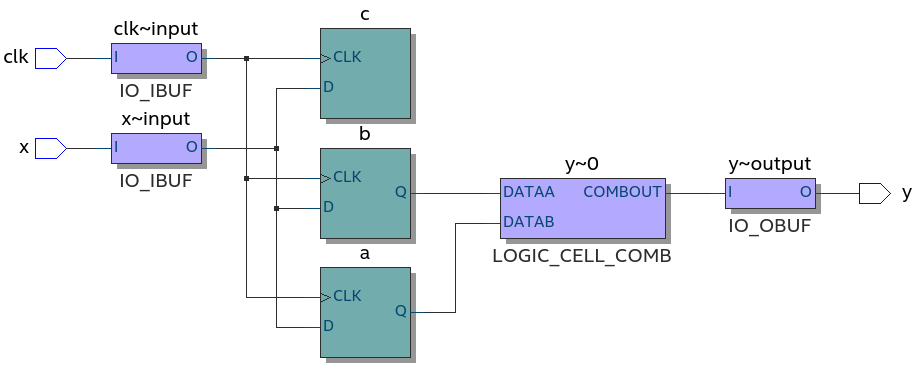

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

Uso da instrução ALIAS.

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

entity div_clk is entrada clk_in saída clk_out

entity countBCD99 is entradas clk_in saídas bcd_u, bcd_d

entity bcd2ssd is entradas bcd, ac_ccn saídas ssd

entity div_clk is entrada clk_in saída clk_out

entity shift_reg is entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in saídas d_out[N-1..0], s_out

entity port_par is entradas clk_in, rst, ena, d_in[N-1..0] saídas d_out[N-1..0]

|

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 6 - Projeto a nível de Sistema

|

| Unidade 7 - Testbench | ||||||||

|---|---|---|---|---|---|---|---|---|

Unidade 7 - Testbench

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

vsim

/opt/altera/13.0/quartus/modelsim_ae/linux/vsim

|

| Unidade 8 - Maquinas de Estado Finitas | ||||||||||

|---|---|---|---|---|---|---|---|---|---|---|

Unidade 8 - Maquinas de Estado Finitas

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END < entity_name > ;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF (clk'EVENT AND clk = '1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

CASE pr_state IS

WHEN A =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= C;

...

ELSE

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END < architecture_name > ;

PROJETO FINAL

Avaliações

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃOOs exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

Referências Bibliográficas:

|