|

|

| Linha 290: |

Linha 290: |

| :* Subprogramas (FUNCTION e PROCEDURE) | | :* Subprogramas (FUNCTION e PROCEDURE) |

| :* LIBRARY e PACKAGE | | :* LIBRARY e PACKAGE |

| :* PARTITION (fisica e lógica) consultar ([http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm], [https://www.altera.com/en_US/pdfs/literature/an/an567.pdf], [https://www.altera.com/en_US/pdfs/literature/wp/wp-01062-quartus-ii-increasing-productivity-incremental-compilation.pdf], [https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/qts/qts_qii5v1.pdf]) | | :* PARTITION (fisica e lógica) consultar |

| | ::*[http://quartushelp.altera.com/15.0/mergedProjects/optimize/dpp/dpp_pro_using_dpp.htm Using the Design Partition Planner], |

| | ::*[https://www.altera.com/en_US/pdfs/literature/an/an567.pdf AN 567: Quartus II Design Separation Flow], |

| | ::*[https://www.altera.com/en_US/pdfs/literature/wp/wp-01062-quartus-ii-increasing-productivity-incremental-compilation.pdf Increasing Productivity With Quartus II Incremental Compilation], |

| | ::*[https://www.altera.com/content/dam/altera-www/global/en_US/pdfs/literature/hb/qts/qts_qii5v1.pdf Quartus II Handbook Volume 1: Design and Synthesis], |

| | ::*[https://www.altera.com/en_US/pdfs/literature/hb/qts/qts_qii51015.pdf Quartus II Incremental Compilation for Hierarchical and Team-Based Design], |

| | ::*[https://www.altera.co.jp/ja_JP/pdfs/literature/hb/qts/qts_qii51017.pdf Best Practices for Incremental Compilation Partitions and Floorplan Assignments]) |

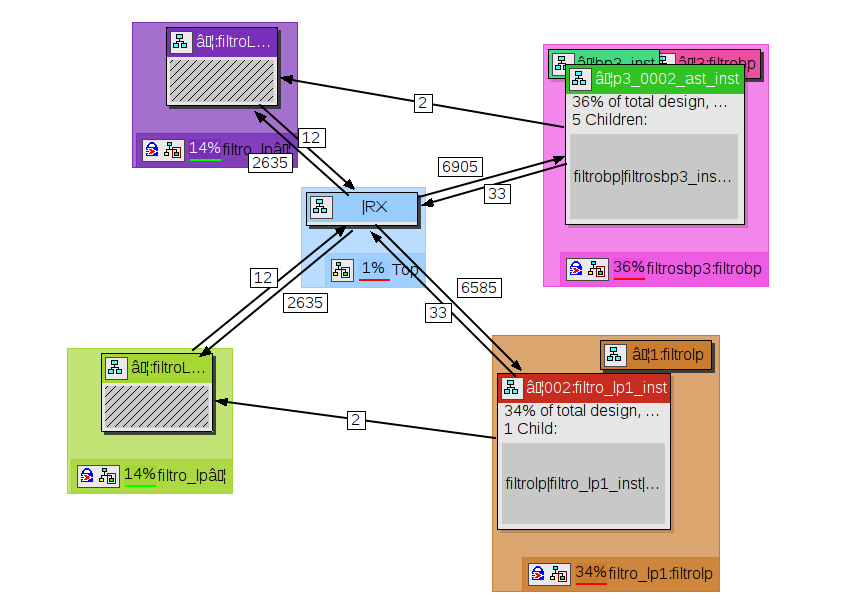

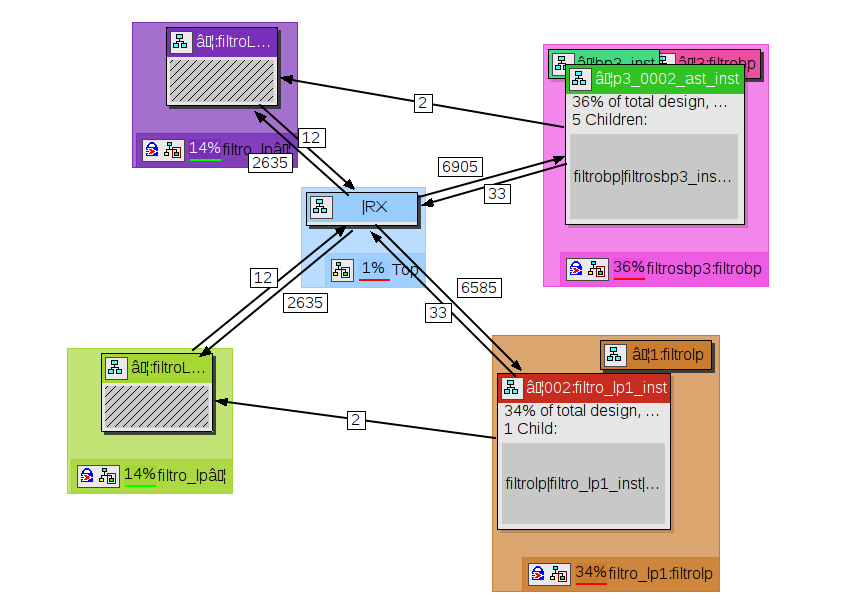

| | Exemplo de sistema particionado visto no Design Partition Planner |

| :[[Arquivo:DesignPartitionPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner]] | | :[[Arquivo:DesignPartitionPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner]] |

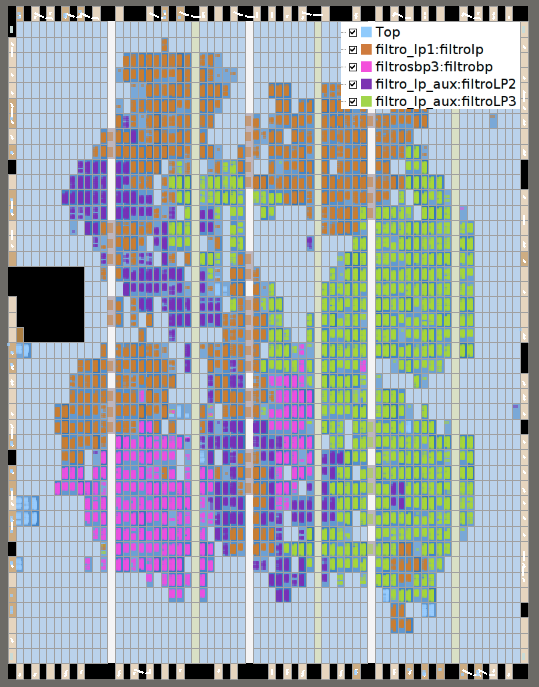

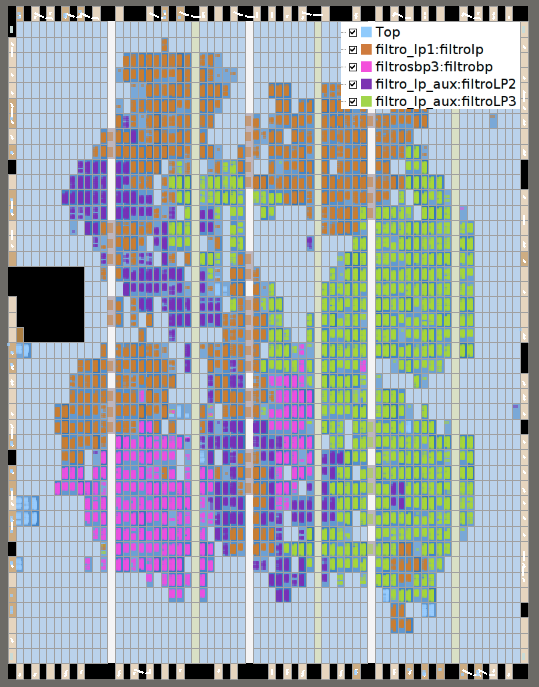

| | Exemplo de sistema acima visto no Chip Planner |

| :[[Arquivo:ChipPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner - Chip Planner]] | | :[[Arquivo:ChipPlanner_QII_Ex1.png | Exemplo de uso do Design Partition Planner - Chip Planner]] |

|

| |

|

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

| Unidade 1 - Processo de Síntese do código VDHL

|

1 Unidade 1

- Aula 6 e 7 (22 e 29 Ago)

- Processo de Síntese do código VDHL

- Limitações dos softwares de EDA: Computabilidade, Complexidade Computacional

- Realização dos operadores VHDL: simplificações para operando constante

- Realização dos tipos de dados: Alta impedância 'Z' -> buffer tri-state;

- Realização dos tipos de dados: uso de don't care '-'

- Tempos de propagação, caminho crítico, caminho falso,

- Síntese com restrições temporais,

- Perigos/Armadilhas (Glitches estáticos e dinâmicos, circuitos sensíveis ao atraso)

- Ver pag. 125 a 162 de [1]

- Ver também os slides Unidade 2: Processo de Síntese do código VDHL

- Ver IO -features: Programmable Delay Uso dos atrasos programáveis nos pinos programáveis de I/O

|

| Unidade 3 - Eficiência de Circuitos Combinacionais

|

2 Unidade 3

- Aula 8 e 9 (4 e 5 Set)

- Eficiência de Circuitos Combinacionais

- Compartilhamento de Operadores (Ex: 7.2.1, 7.2.2, 7.2.3, 7.2.4)

- Compartilhamento de funcionalidades (Ex: L7.1, L7.2, L7.3, L7.4, L7.5)

- Análise da área (Elementos Lógicos) x tempo de propagação.

- Questões relacionadas com o Leiaute do circuito

- Exemplos de circuitos XOR; (Ex: L7.15 - 7.18 e 7.19 - 7.23)

- Exemplos de Deslocador (rotate_right) (Ex: L7.27, 7.28)

- Exemplos de Deslocador (three-function) (Ex: L7.13, 7.14, 7.29)

- Exemplos de Multiplicadores (Ex: L7.34* ,L7.34, 7.35) * soma em cascata

- Ver pag. 163 a 211 de [1]

- Ver também os slides Unidade 3: Eficiência de Circuitos Combinacionais

- Comparação de circuitos somadores de M entradas de N bits. Comparar a implementação em árvore x cadeia. Experimente utilizando tipos Integer e/ou (un)signed. Utilize como base os circuitos dos Exercícios 7.15 e 7.18 [1], nos quais são mostradas implementações de portas XOR. O objetivo desse tópico é realizar medições de tempo, e mudar o desempenho do projeto seja mudando o código ou usando LogicLock ou restrições de tempo.

|

| Unidade 4 - Eficiência de Circuitos Sequenciais

|

3 Unidade 4

- Aula 10 (11 Set)

- Eficiência de Circuitos Sequenciais

- Tipos de Sincronismo em circuitos (globalmente síncronos, localmente síncronos, assíncronos)

- Circuitos síncronos (Modelo, vantagens e tipos)

- Descrição dos elementos básicos de memória (Latch D, Flip Flop D, Registros)

- Projetos síncronos.

| Modelo em VHDL de projeto síncrono

|

-- Declaração das bibliotecas e pacotes a serem utilizados

library ieee;

use ieee.std_logic_1164.all;

entity nome_entidade is

-- Declaração dos valores GENERIC

generic(

___: Natural := ___;

...

);

-- Declaração das portas de entradas e saída

port(

-- Declaração dos sinais de clock e reset assincrono

clk, reset: in std_logic;

-- Declaração das demais portas de entradas isoladas e barramentos

___: in std_logic;

___: in std_logic_vector(__ downto 0);

...

-- Declaração das portas de saídas isoladas e barramentos

___: out std_logic;

___: out std_logic_vector(__ downto 0);

...

);

end entity;

architecture nome_architetura of nome_entidade is

-- Declaração das entradas e saídas dos registros

signal ___reg: std_logic_vector(___ downto 0);

signal ___next: std_logic_vector(___ downto 0);

-- Declaração dos demais sinais internos

...

begin

-- Descrição da lógica sequencial registro

process(clk,reset)

begin

if (reset='1') then

___reg <= (others=>'0');

...

elsif (clk'event and clk='1') then

___reg <= ___next;

...

end if;

end process;

-- Descrição da lógica combinacional de próximo estado

...

...

-- Descrição da lógica combinacional dos circuitos de saída

...

...

end architecture;

|

- Exemplo de FF D com enable;

- Exemplo de FF T;

- Exemplos de registrador de deslocamento;

- Exemplos de contador modulo m;

- Ver pag. 213 a 239 de [1]

- Aula 11 (12 Set)

- Eficiência de Circuitos Sequenciais

-

- Violação do tempo de Setup; Frequencia máxima do clock;

- Temporização relacionadas as saídas.

- Porque não usar VARIABLE em circuitos sequenciais.

- Ver pag. 239 a 255 de [1]

- Ver também os slides Unidade 4: Eficiência de Circuitos Sequenciais

- Ver TimeQuest Clock Analysis

- Aula 12 (18 Set)

- Eficiência de Circuitos Sequenciais

- Praticas deficientes de projeto e soluções:

- Mal uso do RESET assincrono => Use CLEAR síncrono;

--Por exemplo em um contador de 0 a 9 use um CLEAR síncrono

r_next <= (others => '0') when r_reg = 9 else r_reg + 1;

- Mal uso de portas no CLOCK => Use o ENABLE do FF;

--Em um contador

r_next <= r_reg + 1 when ena = '1' else r_reg;

- Mal uso de CLOCK derivados => Use o ENABLE para habilitar o CLOCK durante uma borda de subida;

-- Não use multiplos clocks

elsif (clk'event and clk='1') then

...

elsif (sclk'event and sclk='1') then

...

elsif (mclk'event and mclk='1') then

...

-- Use um único clock com vários enables.

elsif (clk'event and clk='1') then

...

s_next <= (others=>'0') when (s_reg=59 and s_en='1') else

s_reg + 1 when s_en='1' else

s_reg;

...

m_next <= (others=>'0') when (m_reg=59 and m_en='1') else

m_reg + 1 when m_en='1' else

m_reg;

-

0000 0001 0011 0010 0110 0111 0101 0100 1100 1101 1111 1110 1010 1011 1001 1000 0000 ...

0001 0010 0100 1000 0001 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 1010 1011 1100 1101 1110 1111 0000 ...

0000 0001 0010 0011 0100 0101 0110 0111 1000 1001 0000 ...

- LFSR (Linear Feedback Shift Register) [1]

0001 1000 0100 0010 1001 1100 0110 1011 0101 1010 1101 1110 1111 0111 0011 0001 ...

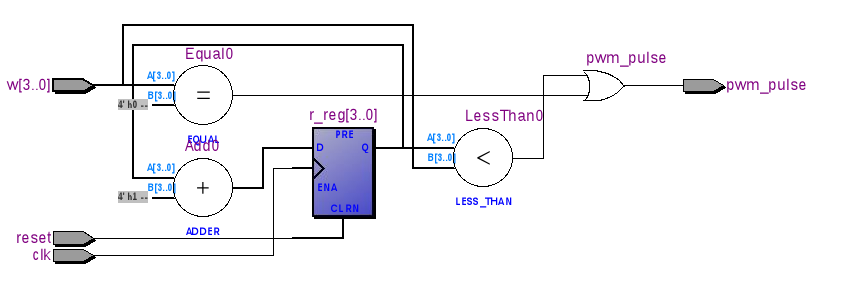

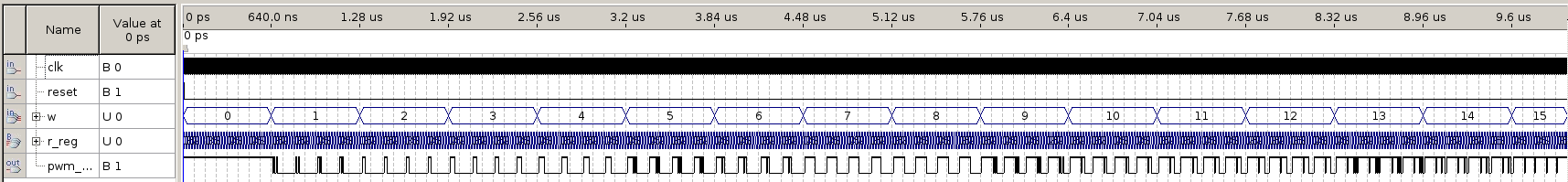

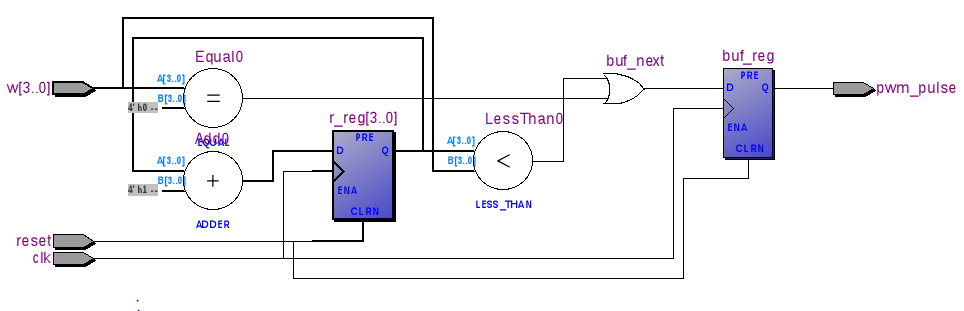

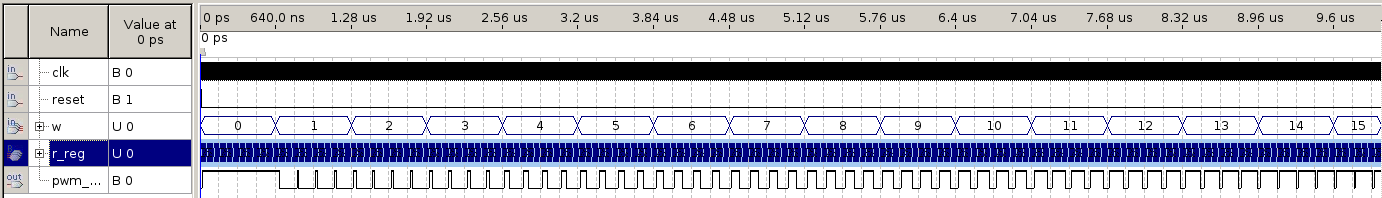

- Modulação por largura de pulso (PWM)

- Uso de um registrador de saída para evitar os erros devido a glitches.

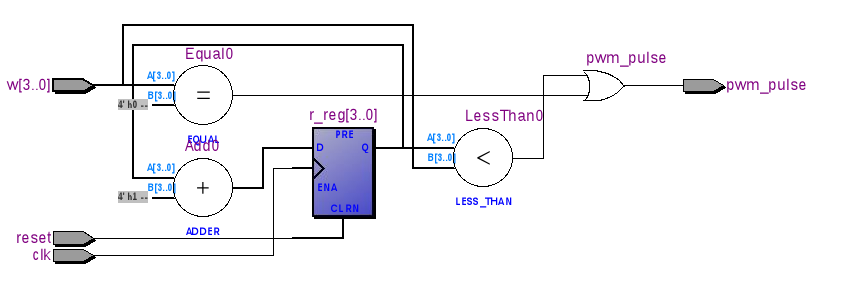

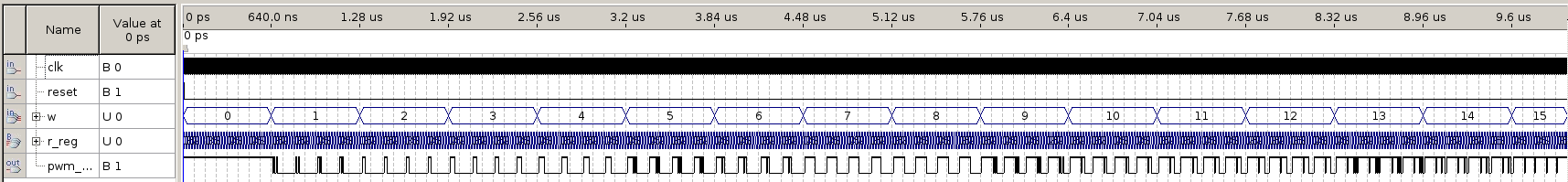

Figura 4.1 - PWM sem buffer de saída - tem gliches na saída.

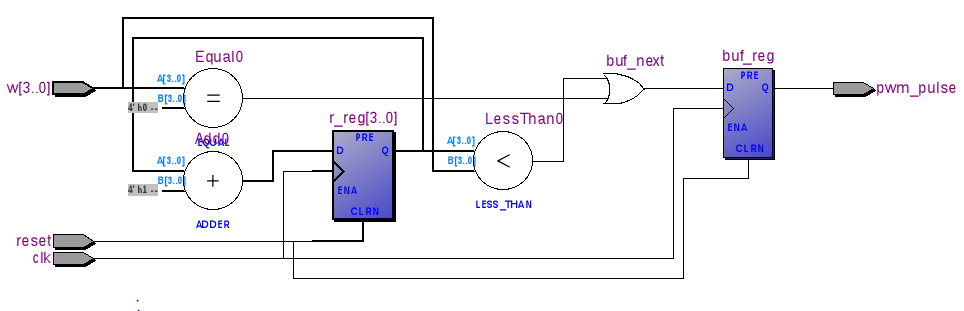

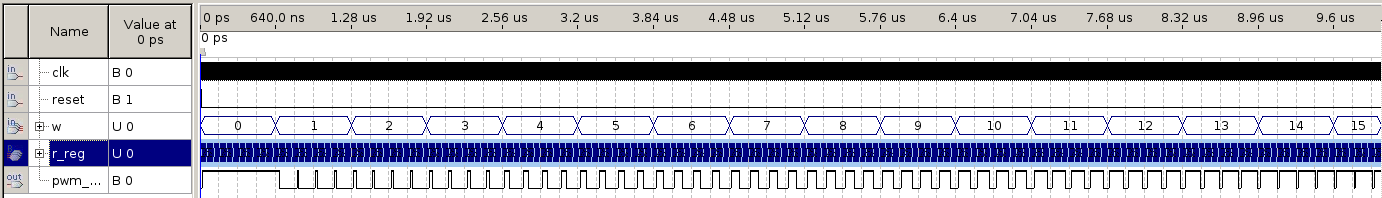

Figura 4.2 - PWM com buffer de saída - não tem gliches na saída.

- Aula 13 (19 Set)

- Uso de registradores como armazenamento temporário - Vetor de registradores.

- FIFO (First In First Out) baseada em vetor de registradores.

- Circuito de controle de FIFO - sinais full (cheia) e empty (vazia)

- Implementação com contador binário ampliado ou com FFs de estado.

- Controle de FIFO com contadores não binários (Gray, LFSR, contador em anel)

- Aula 14 (26 Set)

- Eficiência de Circuitos Combinacionais

- Comparação de circuitos somadores de M entradas de N bits. Comparar a implementação em árvore x cadeia. Experimente utilizando tipos Integer e/ou (un)signed. Utilize como base os circuitos dos Exercícios 7.15 e 7.18 [1], nos quais são mostradas implementações de portas XOR. (opcionalmente pode ser usado o circuito para determinar a distância de Hamming)

- O objetivo desse tópico é realizar medições de tempo, e mudar o desempenho do projeto seja mudando o código ou usando LogicLock ou restrições de tempo.

- Exercício: Verificar os tempos de propagação do caminho crítico nos somadores implementados usando FPGA da familia Ciclone e Ciclone IV E, Considerando um circuito com 8 entradas de 12 bits.

- Sem usar LogicLock anote os resultados. Observe a disposição dos elementos lógicos no Chip Planner.

- Usando o LogicLock, selecione uma região qualquer do chip para implementar o circuito, e faça a compilação do circuito. Use regiões na Vertical, na Horizontal e Retangular e anote os resultados.

- Anote em um tabela o número de Elementos lógicos (Totais|Normais|Aritméticos), o tempo de propagação do caminho crítico, indicando a origem e destino dele. Desconsidere os dois primeiros e dois últimos tempos indicados no Path Report, pois são referentes a entrada do sinal e saída dos sinais até a região de interesse no FPGA.

- Sem usar LogicLock, insira um arquivo de restrição SDC com a restrição (set_max_delay -from a* -to y* T), onde T é o atraso maximo entre as entradas a* até as saídas y*. Procure obter tempos de atraso menores que os anteriores.

- Experimente aumentar os tempos de atraso usando (set_min_delay -from a* -to y* T).

- Compare seus resultados com o dos colegas que escolheram outras regiões do chip.

|

| Unidade 8 - Projeto Hierarquico e Parametrizado

|

4 Unidade 8

- Aula 24 (21 Nov)

- COMPONENTS (declaração e instanciação). Mapeamento dos nomes das portas por nome X posição

- GENERIC

- CONFIGURATION (declaração X especificação X instanciação e configuração no VHDL 93)

- Subprogramas (FUNCTION e PROCEDURE)

- LIBRARY e PACKAGE

- PARTITION (fisica e lógica) consultar

Exemplo de sistema particionado visto no Design Partition Planner

Exemplo de sistema acima visto no Chip Planner

- Ver pag. 473 a 498 de [1]

|

5 Referências Bibliográficas:

- ↑ 1,0 1,1 1,2 1,3 1,4 1,5 1,6 1,7 1,8 Pong P. Chu, RTL Hardware Design Using VHDL: Coding for Efficiency, Portability, and Scalability. Wiley-IEEE Press, Hoboken, 2006, ISBN 0471720925

Curso de Engenharia de Telecomunicações