DLP29006-Engtelecom(2017-2) - Prof. Marcos Moecke: mudanças entre as edições

Ir para navegação

Ir para pesquisar

| Linha 297: | Linha 297: | ||

:: Ver pag. 91 a 108 de <ref name="PEDRONI2010b"/> | :: Ver pag. 91 a 108 de <ref name="PEDRONI2010b"/> | ||

;Aula 12 (6 Set): | |||

:* Atributos de síntese: | :* Atributos de síntese: | ||

::* Enum_encoding [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_enum_encoding.htm] | ::* Enum_encoding [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_enum_encoding.htm] | ||

::* chip_pin [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_chip.htm] | ::* chip_pin [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_chip.htm] | ||

;Aula 13 ( | ::* keep [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_keep.htm] | ||

:::* Exemplo 4.4: Delay line (Síntese e Simulação temporal sem o com o atributo keep) | |||

;Aula 13 (13 Set): | |||

*Atributos em VHDL. | *Atributos em VHDL. | ||

:* Atributos de síntese: | :* Atributos de síntese: | ||

:::* Exemplo 5.8 Gerador de Pulsos estreitos | :::* Exemplo 5.8 Gerador de Pulsos estreitos | ||

::* preserve [http://quartushelp.altera.com/15.0/mergedProjects/logicops/logicops/def_preserve_fanout_free_node.htm] | ::* preserve [http://quartushelp.altera.com/15.0/mergedProjects/logicops/logicops/def_preserve_fanout_free_node.htm] | ||

::* noprune. | ::* noprune. | ||

:::* Exemplo 4.5: Preserve and noprune attributes | :::* Exemplo 4.5: Preserve and noprune attributes | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 342: | Linha 345: | ||

<center> [[Arquivo:Ex4_5_PreserveAttribute.png| Preserve (or Keep) Attribute |400 px]] <br> '''Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep) '''</center> | <center> [[Arquivo:Ex4_5_PreserveAttribute.png| Preserve (or Keep) Attribute |400 px]] <br> '''Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep) '''</center> | ||

<center> [[Arquivo:Ex4_5_NopruneAttribute.png| Noprune Attribute| 400 px]] <br> '''Fig 14. Technology Map do Circuito com Attribute Noprune '''</center> | <center> [[Arquivo:Ex4_5_NopruneAttribute.png| Noprune Attribute| 400 px]] <br> '''Fig 14. Technology Map do Circuito com Attribute Noprune '''</center> | ||

:* Group | :* Group | ||

| Linha 365: | Linha 367: | ||

:: Ver pag. 108 a 119, 140 a 142 de <ref name="PEDRONI2010b"/> | :: Ver pag. 108 a 119, 140 a 142 de <ref name="PEDRONI2010b"/> | ||

<!-- | |||

===Unidade 4=== | ===Unidade 4=== | ||

;Aula 14 (21 mar): | ;Aula 14 (21 mar): | ||

Edição das 07h30min de 13 de setembro de 2017

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

1 Registro on-line das aulas

1.1 Unidade 1

- Aula 1 (27 Jul)

- Apresentação da disciplina

- Autoinscrição na Plataforma Moodle de DLP29006 (engtelecom)

- Ler In the beginning - ALTERA

- Ler ALTERA history

- Preços

- Fabricantes de DLPs/FPGAs e familias de DLPs atuais.

- Aula 2 (2 Ago)

- Introdução aos dispositivos lógicos programáveis:

- Conceito, tipos de PLDs

- SPLD: PAL, PLA e GAL

- CPLDs

| Exemplos de PLDs |

|---|

|

- Arquitetura de FPGAs (Xilinx e Altera): CLB, LAB, RAM, DSP, Clock, PLL, I/O

- Aula 3 (3 Ago)

-

- Vizualização no Chip Planner de um projeto. (importante todos alunos terem acesso a IFSC-CLOUD

- Historia, processo de produção dos chips.

- A Brief History of the Fabless Semiconductor Industry

- Taiwan Semiconductor Manufacturing Corporation (TSMC), [http://www.globalfoundries.com/ GLOBALFOUNDRIES

- Fabless: The Transformation of the Semiconductor Industry, 2014 - Download free

- 14nm FinFET Technology, Samsung & Globalfounfries, Funcionamento do FinFET, Produção do FinFET, [1]

- Processo de fabricação de um chip

1.2 Unidade 2

- Aula 4 (9 ago)

- Introdução ao VHDL e ambiente EDA - QUARTUS

- Estrutura do código VHDL

- Declaração das bibliotecas e pacotes LIBRARY / PACKAGE

library library_name; use library_name.package)name.all;

- ENTITY

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

- ARCHITECTURE

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

- Exemplo - Declaração de uma porta NAND em VHDL

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

- Exemplo 2.2 (VHDL) - programação de um flip-flop

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

- Após a criação do projeto em VHDL utilizando a descrição de hardware acima, compile o código VHDL.

- Use o RTL Viewer para ver a descrição RTL do circuito.

- Use o Technology Map Viewer para ver a como o circuito foi mapeado para os elementos lógicos disponíveis no dispositivo FPGA selecionado (EP1C3T100A8)

- Abra o Chip Planner e observe no Node Properties como esse circuito é conectado dentro do dispositivo FPGA selecionado

- Realizar as simulações funcional e temporal do circuito

- Aula 5 (10 Ago)

- Introdução ao VHDL e ambienta EDA - QUARTUS

- Estrutura do código VHDL

- Modifique o circuito para que ele passe a ter 16 flip-flops, e realize as simulações funcional e temporal do circuito.

- Exemplo 2.3 (VHDL e QSIM) - programação de um circuito somador com registrador

- Realizar as simulações funcional e temporal do circuito

- Observar o "Technology Map" e o "RTL" do circuito

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

- Acrescente saídas para o sinal sum e para o sinal comp, de modo a poder observar estes sinais no simulador QSIM e realize novas simulações funcional e temporal.

- ver Tutorial do QSIM - Introduction to Simulation of VHDL Designs da ALTERA.

- Ver pag. 3 a 24 de [2]

1.3 Unidade 3

- Aula 6 (17 Ago)

- Tipos de Dados em VHDL.

- Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE.

- Palavra chave OTHERS

- Ver pag. 31 a 35 de [2]

- Bibliotecas padrão IEEE (std_logic_1164, numeric_std).

- ATENÇÃO!!! Não use as bibliotecas que não são padrão (std_logic_arith, std_logic_unsigned, std_logic_signed)

- Aula 7 (23 Ago)

-

- Classificação dos tipos de dados.

- Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR

- Exemplo 3.1 Buffer Tri-state

- Exemplo 3.2 Circuito com Saida "don't care"

- Tipos de dados: SIGNED e UNSIGNED

- Exemplo 3.3 Multiplicador de 4x4 bits (UN)SIGNED e INTEGER

| Código Multiplicador |

|---|

--LIBRARY ieee;

--USE ieee.numeric_std.all;

ENTITY multiplicador4x4 IS

-- multiplicador usando UNSIGNED

-- PORT (a, b: IN UNSIGNED(3 DOWNTO 0); -- min(a) = 0; max(a) = 15 <-- 4 bits

-- y: OUT UNSIGNED(7 DOWNTO 0)); -- min(a*b) = 0, max(a*b) = 225 --> 8 bits

-- multiplicador usando SIGNED

-- PORT (a, b: IN SIGNED(3 DOWNTO 0); -- min(a) = -8; max(a) = 7 <-- 4 bits

-- y: OUT SIGNED(7 DOWNTO 0)); -- min(a*b) = -56, max(a*b) = 64 --> 8 bits

-- multiplicador usando INTEGER (positivos)

-- PORT (a, b: IN INTEGER RANGE 0 TO 15; -- min(a) = 0; max(a) = 15 --> 4 bits

-- y: OUT INTEGER RANGE 0 TO 225); -- min(a*b) = 0, max(a*b) = 225 --> 8 bits

-- multiplicador usando INTEGER (positivos e negativos)

-- PORT (a, b: IN INTEGER RANGE -8 TO 7; -- min(a) = -8; max(a) = 7 --> 4 bits

-- y: OUT INTEGER RANGE -56 TO 64); -- min(a*b) = -56, max(a*b) = 64 --> 8 bits

END ENTITY;

ARCHITECTURE v1 OF multiplicador4x4 IS

BEGIN

y <= a * b;

END ARCHITECTURE;

|

- Ver pag. 39 a 54 de [2]

- Aula 8 (24 Ago)

- Tipos de Dados em VHDL.

- Resumo dos Tipos predefinidos (Tabela 3.6).

- Tipos definidos pelo usuário:

- Escalares (Inteiros e Enumerados)

- Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D

- Exemplos Ex 3.5, Ex 3.6 e Ex 3.7

- Ver pag. 51 a 70 de [2]

- Aula 9 (30 Ago)

-

- Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer)

- RECORD e SUBTYPE

- Uso de ARRAYs em portas

- Declaração do TYPE em PACKAGE

- Exemplo 3.8: Multiplexador com porta 1D x 1D.

- Qualificação de tipos, conversão de tipos (automática, casting e funções de conversão).

- Resumo das funções de conversão de tipos (Tabela 3.10) e ver Aritmética com vetores em VDHL

- Exemplo 3.9: Multiplicador com sinal (entrada do tipo STD_LOGIC VECTOR)

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY signed_multiplier IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

y: OUT STD_LOGIC_VECTOR(7 DOWNTO 0)

);

END ENTITY;

ARCHITECTURE type_conv_arch OF signed_multiplier IS

BEGIN

y <= std_LOGIC_VECTOR(SIGNED(a) * SIGNED(b));

END ARCHITECTURE;

- Ver pag. 73 a 78 de [2]

- Aula 11 (31 Ago)

- Operadores em VHDL.

- Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching".

- Sobrecarga de operadores

- Atributos em VHDL.

- Atributos predefinidos: tipo escalar e enumerados; tipo array; de sinal;

- Exemplo 4.2 (Simulação funcional)

- Atributos definidos pelo usuário;

- Ver pag. 91 a 108 de [2]

- Aula 12 (6 Set)

-

- Atributos de síntese:

- Aula 13 (13 Set)

- Atributos em VHDL.

- Atributos de síntese:

- Exemplo 5.8 Gerador de Pulsos estreitos

- preserve [5]

- noprune.

- Exemplo 4.5: Preserve and noprune attributes

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.

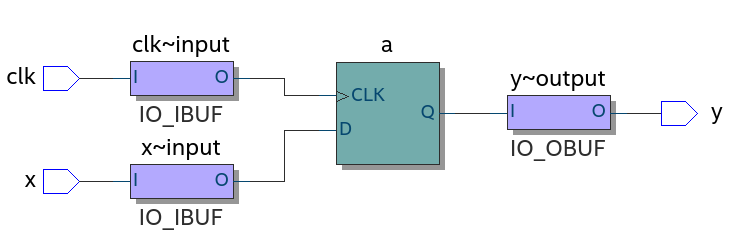

Fig 12. Technology Map do Circuito sem Attribute

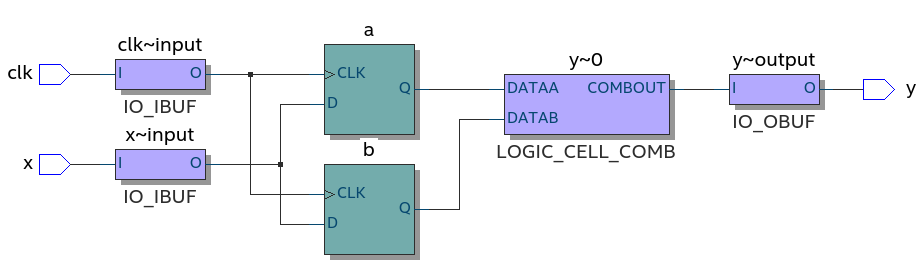

Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)

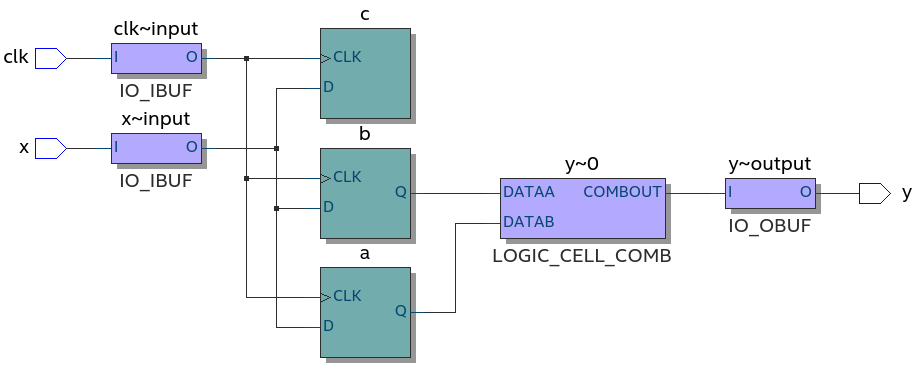

Fig 14. Technology Map do Circuito com Attribute Noprune

- Group

- Alias

- Exemplo de uso no pacote numeric_std.vhd

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

- Exercício 4.17: Discussão de possibilidades de implementação

- Ver pag. 108 a 119, 140 a 142 de [2]

2 Avaliações

- Avaliação A1 - Unidade 2 a 4 (XX/XX/2017) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2017) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2017) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

- Autoinscrição na Plataforma Moodle de DLP29006 (engtelecom) - ATENÇÃO! MUDEI O AMBIENTE PARA PRESERVAR O ACESSO DOS ALUNOS ANTERIORES.

| AE0 - Resumo estendido de Artigo |

|---|

|

- Projeto Final APF

2.1 ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

| EL0 - Resolução dos exercícios do Cap 2 |

|---|

especificado.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

|

| EL1 - Uso de tipos de dados e operadores |

|---|

|

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL3 - Conversor de Binário para BCD |

|---|

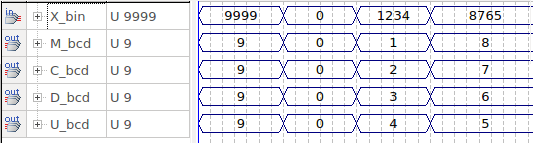

Fig. 20 - Simulação da conversão de binário para BCD

entity bin2bcd is

port (

X_bin : in std_logic_vector(13 downto 0); -- 0000 a 9999

M_bcd : out std_logic_vector(3 downto 0); -- Milhar

C_bcd : out std_logic_vector(3 downto 0); -- Centena

D_bcd : out std_logic_vector(3 downto 0); -- Dezena

U_bcd : out std_logic_vector(3 downto 0)); -- Unidade

end entity;

architecture example of bin2bcd is

--declaração de sinais auxiliares

begin

--descrição do hardware

end architecture;

M_bcd <= std_logic_vector(to_unsigned(M,4)); |

3 Referências Bibliográficas: