Mudanças entre as edições de "DLP29006-Engtelecom(2018-1) - Prof. Marcos Moecke"

| (79 revisões intermediárias por 2 usuários não estão sendo mostradas) | |||

| Linha 2: | Linha 2: | ||

==Registro on-line das aulas== | ==Registro on-line das aulas== | ||

{{collapse top| Unidade 1 - Introdução}} | {{collapse top| Unidade 1 - Introdução}} | ||

| − | ===Unidade 1 - | + | ===Unidade 1 - Introdução=== |

;Aula 1 (16 fev): | ;Aula 1 (16 fev): | ||

*[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | *[[DLP1-EngTel (Plano de Ensino) | Apresentação da disciplina]] | ||

| Linha 64: | Linha 64: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top| | + | {{collapse top| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS}} |

| + | |||

===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ===Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS=== | ||

;Aula 4 e 5 (26 e 28 fev): | ;Aula 4 e 5 (26 e 28 fev): | ||

| Linha 163: | Linha 164: | ||

::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | ::O Package '''standard''': é parte do VHDL desde a primeira versão (1987). Ela contem definição de tipos de dados (BIT, INTEGER, BOOLEAN, CHARACTER, etc.) e seus operadores logicos, aritméticos, de comparação e shift. | ||

::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | ::O Package textio fornece os recurso para o tratamento de textos e arquivos, que podem ser utilizados na simulação. | ||

| − | + | *Como declarar e usar os pacotes da biblioteca '''std'''. | |

| + | :: Note que esses pacotes são implicitamente carregados não precisando ser declarados. Ambos pacotes foram expandidos no VHDL 2008. | ||

:::<syntaxhighlight lang=vhdl> | :::<syntaxhighlight lang=vhdl> | ||

| + | -- NAO É NECESSARIO DECLARAR | ||

library std; | library std; | ||

use std.standard.all; | use std.standard.all; | ||

use std.textio.all; | use std.textio.all; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | *Onde estão os arquivos dessa biblioteca na versão Quartus II instalada nos computadores do IFSC e na IFSC_CLOUD? | ||

| + | ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std | ||

:*Library '''ieee''' | :*Library '''ieee''' | ||

| Linha 174: | Linha 179: | ||

:: O Package '''numeric_std''' define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo STD_LOGIC como base. | :: O Package '''numeric_std''' define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo STD_LOGIC como base. | ||

:: O Package '''numeric_bit''' define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo BIT como base. | :: O Package '''numeric_bit''' define os tipos de dados SIGNED e UNSIGNED e seus operadores considerando o tipo BIT como base. | ||

| − | :: O Package '''numeric_std_unsigned''' introduz operadores sobre o tipo | + | :: O Package '''numeric_std_unsigned''' introduz operadores sobre o tipo STD_LOGIC_VECTOR, considerando os como números sem sinal. |

| − | + | :: O Package '''numeric_bit_unsigned''' introduz operadores sobre o tipo BIT_VECTOR, considerando os como números sem sinal. | |

| − | + | :: O Package '''fixed_pkg''' (e pacotes associados) definem os tipos de ponto fixo unsigned (UFIXED) e signed (SFIXED) e seus operadores. | |

| − | + | :: O Package '''float_pkg''' (e pacotes associados) definem o tipo de ponto flutuante (FLOAT) e seus operadores. | |

| − | + | :* Pacotes não padronizados ('''NÃO UTILIZAR''') | |

| − | + | : O Package std_logic_arith define os tipos de dados SIGNED e UNSIGNED e seus operadores. Deve ser sempre substituído por pelo pacote padrão equivalente numeric_std. (disponível da Mentor e Synopsys) | |

| − | + | : O Package std_logic_unsigned é semelhante ao numeric_std_unsigned. (disponível da Synopsys) | |

| + | : O Package std_logic_signed é semelhante ao acima operando sobre números com sinal. (disponível da Synopsys) | ||

| + | |||

| + | *Como declarar e usar os pacotes da biblioteca '''ieee'''. | ||

| + | :::<syntaxhighlight lang=vhdl> | ||

| + | library ieee; | ||

| + | -- UTILIZAR ESTES PACOTES | ||

| + | use ieee.std_logic_1164.all; | ||

| + | use ieee.numeric_std.all; | ||

| + | |||

| + | -- NAO UTILIZAR ESTES PACOTES | ||

| + | use ieee.std_logic_arith.all; | ||

| + | use ieee.std_logic_signed.all; | ||

| + | use ieee.std_logic_unsigned.all; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | *Onde estão os arquivos dessa biblioteca na versão Quartus II versão 13.0sp1 instalada nos computadores do IFSC e na IFSC_CLOUD? | ||

| + | ::Os pacotes padrão: | ||

| + | ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee | ||

| + | |||

| + | ::Os pacotes não padrão: | ||

| + | ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) | ||

| + | ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys) | ||

| + | |||

| + | *Os arquivos dessa biblioteca do padrão (versão 2008) estão apenas disponíveis a partir do Quartus II versão 16.0 instalado na IFSC_CLOUD? | ||

| + | ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008 | ||

;Aula 6 (2 mar): | ;Aula 6 (2 mar): | ||

| Linha 195: | Linha 225: | ||

<center> Figura 2.7 - Simulação Temporal de 4 FF 100ns</center> | <center> Figura 2.7 - Simulação Temporal de 4 FF 100ns</center> | ||

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. | Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. | ||

| + | |||

| + | ''IMPORTANTE:'' Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo. | ||

| + | * Para definir as restrições de tempo do clock por exemplo, pode ser adicionado um arquivo .sdc ao projeto definindo a frequencia do clock esperada através da seguinte linha: | ||

| + | |||

| + | create_clock -name CLK50MHz -period 50MHz [get_ports {*}] | ||

| + | |||

:* Exemplo 2.3 (VHDL e QSIM) - programação de um circuito somador com registrador | :* Exemplo 2.3 (VHDL e QSIM) - programação de um circuito somador com registrador | ||

| Linha 233: | Linha 269: | ||

::Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | ::Ver pag. 3 a 24 de <ref name="PEDRONI2010b"> PEDRONI, Volnei A. '''Circuit Design and Simulation with VHDL'''; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335 </ref> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | ||

| − | {{collapse top| Unidade 3 - Tipos de Dados e Operadores em VHDL}} | + | {{collapse top | Unidade 3 - Tipos de Dados e Operadores em VHDL}} |

===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ===Unidade 3 - Tipos de Dados e Operadores em VHDL=== | ||

| − | ;Aula | + | ;Aula 7 (5 mar): |

*Tipos de Dados em VHDL. | *Tipos de Dados em VHDL. | ||

:*Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE. | :*Objetos de VHDL: CONSTANT, SIGNAL, VARIABLE, FILE. | ||

| Linha 243: | Linha 279: | ||

:* Bibliotecas padrão IEEE ('''std_logic_1164''', '''numeric_std'''). | :* Bibliotecas padrão IEEE ('''std_logic_1164''', '''numeric_std'''). | ||

::* '''ATENÇÃO!!! Não use as bibliotecas que não são padrão (''std_logic_arith, std_logic_unsigned, std_logic_signed''''') | ::* '''ATENÇÃO!!! Não use as bibliotecas que não são padrão (''std_logic_arith, std_logic_unsigned, std_logic_signed''''') | ||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

:* Exemplo 3.3 Multiplicador de 4x4 bits (UN)SIGNED e INTEGER | :* Exemplo 3.3 Multiplicador de 4x4 bits (UN)SIGNED e INTEGER | ||

{{collapse top | Código Multiplicador}} | {{collapse top | Código Multiplicador}} | ||

| Linha 286: | Linha 315: | ||

:: Ver pag. 39 a 54 de <ref name="PEDRONI2010b"/> | :: Ver pag. 39 a 54 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula 8 ( | + | ;Aula 8 (7 mar): |

*Tipos de Dados em VHDL. | *Tipos de Dados em VHDL. | ||

| − | :* Resumo dos Tipos predefinidos ( | + | * Classificação dos tipos de dados. |

| + | :* Tipos de dados: BIT, BIT_VECTOR, BOOLEAN, INTEGER, NATURAL, POSITIVE, CHARACTER, STRING, STD_(U)LOGIG, STD_(U)LOGIG_VECTOR | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | package standard is | ||

| + | type boolean is (false,true); | ||

| + | type bit is ('0', '1'); | ||

| + | type severity_level is (note, warning, error, failure); | ||

| + | type integer is range -2147483647 to 2147483647; | ||

| + | type real is range -1.0E308 to 1.0E308; | ||

| + | type time is range -2147483648 to 2147483647 | ||

| + | units | ||

| + | fs; | ||

| + | ps = 1000 fs; | ||

| + | ns = 1000 ps; | ||

| + | us = 1000 ns; | ||

| + | ms = 1000 us; | ||

| + | sec = 1000 ms; | ||

| + | min = 60 sec; | ||

| + | hr = 60 min; | ||

| + | end units; | ||

| + | subtype natural is integer range 0 to integer'high; | ||

| + | subtype positive is integer range 1 to integer'high; | ||

| + | type string is array (positive range <>) of character; | ||

| + | type bit_vector is array (natural range <>) of bit; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | <syntaxhighlight lang=vhdl> | ||

| + | PACKAGE std_logic_1164 IS | ||

| + | TYPE std_ulogic IS ( 'U', -- Uninitialized | ||

| + | 'X', -- Forcing Unknown | ||

| + | '0', -- Forcing 0 | ||

| + | '1', -- Forcing 1 | ||

| + | 'Z', -- High Impedance | ||

| + | 'W', -- Weak Unknown | ||

| + | 'L', -- Weak 0 | ||

| + | 'H', -- Weak 1 | ||

| + | '-' -- Don't care | ||

| + | ); | ||

| + | TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic; | ||

| + | SUBTYPE std_logic IS resolved std_ulogic; | ||

| + | TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic; | ||

| + | </syntaxhighlight> | ||

| + | |||

| + | ::* Exemplo 3.1 Buffer Tri-state | ||

| + | ::: '''Importante''': O terceiro estado 'Z' só pode ser usado em saídas, e a sua realização nos FPGAs só ocorre nos nós de I/O. | ||

| + | ::* Exemplo 3.2 Circuito com Saida "don't care" | ||

| + | |||

| + | :* Tipos de dados: SIGNED e UNSIGNED | ||

| + | ::* Exemplo 3.3 Multiplicador (visto anteriormente) | ||

| + | :* Resumo dos Tipos predefinidos. | ||

| + | {| class="wikitable sortable" border="1" cellpadding="3" cellspacing="0" style="text-align:left; font-size:100%" bgcolor="#efefef" | ||

| + | ! scope="col" width=15% align="left"| Tipo de Dado | ||

| + | ! scope="col" width=10% align="left"| Package | ||

| + | ! scope="col" width=7% align="left"| Library | ||

| + | ! scope="col" width=50% align="left"| Valores | ||

| + | ! scope="col" width=15% align="left"| Observações | ||

| + | |- | ||

| + | | BOOLEAN || standard || std || TRUE e FALSE || sintetizável | ||

| + | |- | ||

| + | | BIT || standard || std || valores '0', '1' || sintetizável | ||

| + | |- | ||

| + | | INTEGER || standard || std || números inteiros de 32 bits [de -2^31 até + (2^31 - 1)] || sintetizável | ||

| + | |- | ||

| + | | NATURAL || standard || std || números inteiros não negativos [de 0 até + (2^31 - 1)] || sintetizável | ||

| + | |- | ||

| + | | POSITIVE || standard || std || números inteiros positivos [de 1 até + (2^31 - 1)] || sintetizável | ||

| + | |- | ||

| + | | BOOLEAN_VECTOR || standard (2008) || std || vetor de BOOLEAN || sintetizável | ||

| + | |- | ||

| + | | BIT_VECTOR || standard || std || vetor de BIT || sintetizável | ||

| + | |- | ||

| + | | INTEGER_VECTOR || standard || std || vetor de INTEGER || sintetizável | ||

| + | |- | ||

| + | | REAL || standard || std || números reais [de -1.0E-38 até + 1.0E-38] || simulação | ||

| + | |- | ||

| + | | CHARACTER || standard || std || caracteres ASCII || | ||

| + | |- | ||

| + | | STRING || standard || std || vetor de CHARACTER || | ||

| + | |- | ||

| + | | STD_LOGIC || std_logic_1164 || ieee || valores 'U', 'X', '0', '1', 'Z', 'W', 'L', 'H', '-' || sintetizável | ||

| + | |- | ||

| + | | STD_LOGIC_VECTOR || std_logic_1164 || ieee || vetor de STD_LOGIC || sintetizável | ||

| + | |- | ||

| + | | SIGNED || numeric_std || ieee || STD_LOGIC_VECTOR que aceitam operações aritméticas com sinal|| sintetizável | ||

| + | |- | ||

| + | | UNSIGNED || numeric_std || ieee || STD_LOGIC_VECTOR que aceitam operações aritméticas || sintetizável | ||

| + | |- | ||

| + | | SIGNED || numeric_bit || ieee || BIT_VECTOR que aceitam operações aritméticas com sinal || sintetizável | ||

| + | |- | ||

| + | | UNSIGNED || numeric_bit || ieee || BIT_VECTOR que aceitam operações aritméticas || sintetizável | ||

| + | |- | ||

| + | | SIGNED || std_logic_arith || ieee || STD_LOGIC_VECTOR que aceitam operações aritméticas com sinal || sintetizável (não é padrão) | ||

| + | |- | ||

| + | | UNSIGNED || std_logic_arith || ieee || STD_LOGIC_VECTOR que aceitam operações aritméticas || sintetizável (não é padrão) | ||

| + | |- | ||

| + | | UFIXED || fixed_pkg + (2008) || ieee || números de ponto fixo sem sinal|| sintetizável | ||

| + | |- | ||

| + | | SFIXED || fixed_pkg + (2008) || ieee || números de ponto fixo com sinal|| sintetizável | ||

| + | |- | ||

| + | | FLOAT || float_pkg + (2008) || ieee || Números de ponto flutuante || sintetizável | ||

| + | |||

| + | |} | ||

| + | |||

| + | ;Aula 9 (12 mar): | ||

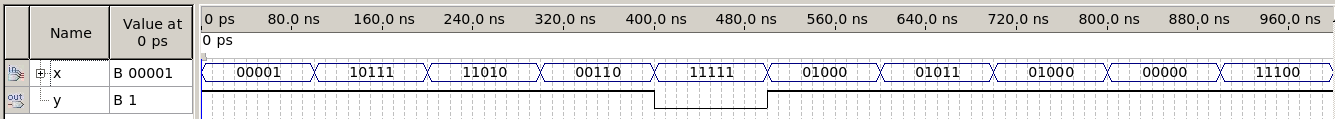

| + | * '''Desafio''' - Fazer um circuito que detecte se existe alguma vaga vazia em um lote de 5 vagas. Cada entrada x(n) está alta '1' se a vaga está vazia. A saída y estará alta '1' sempre que houver uma ou mais vagas vazias. | ||

| + | :'''Importante''': O ''don't care'' não funciona como se espera para uma entrada, por isso, use ''don't care'' apenas para saídas. | ||

| + | x = "1----" -- não funciona em VHDL | ||

| + | *Se quiser mesmo usar ''don't care'' em entradas use a função '''std_match''' do pacote '''numeric_std''' | ||

| + | std_match(x, "1----") -- funciona em VHDL | ||

| + | *Faça a simulação do circuito para ver se está funcionando, | ||

| + | [[Arquivo:vagas5.png | 800px]] | ||

| + | * Os alunos foram liberados para assistir uma palestra pelos 30 anos do campus SJE as 14h00. | ||

| + | |||

| + | ;Aula 10 (14 mar): | ||

:* Tipos definidos pelo usuário: | :* Tipos definidos pelo usuário: | ||

::* Escalares (Inteiros e Enumerados) | ::* Escalares (Inteiros e Enumerados) | ||

::* Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D | ::* Tipos de Array 1D x 1D, 2D , 1D x 1D x 1D, 3D | ||

:::Exemplos Ex 3.5, Ex 3.6 e Ex 3.7 | :::Exemplos Ex 3.5, Ex 3.6 e Ex 3.7 | ||

| − | :: Ver pag. | + | :* RECORD e SUBTYPE |

| + | :* Uso de ARRAYs em portas | ||

| + | ::* Declaração do TYPE em PACKAGE | ||

| + | ::* Exemplo 3.8: Multiplexador com porta 1D x 1D.:: | ||

| + | Ver pag. 60 a 73 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula | + | ;Aula 11 (16 mar): |

:* Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | :* Tipos de dados predefinidos: FIXED e FLOAT (apenas conhecer) | ||

| − | + | ||

| − | |||

| − | |||

| − | |||

*Qualificação de tipos, conversão de tipos (automática, casting e funções de conversão). | *Qualificação de tipos, conversão de tipos (automática, casting e funções de conversão). | ||

:* Resumo das funções de conversão de tipos (Tabela 3.10) e ver [[Aritmética com vetores em VDHL]] | :* Resumo das funções de conversão de tipos (Tabela 3.10) e ver [[Aritmética com vetores em VDHL]] | ||

| − | :* | + | :* Exercicio: Multiplicador/Divisor/Somador/Subtrator com sinal e sem sinal (entradas do tipo STD_LOGIC VECTOR) |

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

LIBRARY ieee; | LIBRARY ieee; | ||

| Linha 309: | Linha 453: | ||

USE ieee.numeric_std.all; | USE ieee.numeric_std.all; | ||

| − | ENTITY | + | ENTITY operadores IS |

PORT ( | PORT ( | ||

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0); | a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0); | ||

| − | + | mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0); | |

| − | ); | + | div: OUT STD_LOGIC_VECTOR(? DOWNTO 0); |

| + | sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0); | ||

| + | sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0); | ||

| + | ); | ||

END ENTITY; | END ENTITY; | ||

| − | ARCHITECTURE type_conv_arch OF | + | ARCHITECTURE type_conv_arch OF operadores IS |

BEGIN | BEGIN | ||

| − | + | -- Inserir o código e definir o tamanho das saidas. | |

END ARCHITECTURE; | END ARCHITECTURE; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

:: Ver pag. 73 a 78 de <ref name="PEDRONI2010b"/> | :: Ver pag. 73 a 78 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula | + | ;Aula 12 e 13 (21 e 26 mar): |

*Operadores em VHDL. | *Operadores em VHDL. | ||

:* Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching". | :* Operadores predefinidos: Atribuição, Lógicos, Aritméticos, Comparação, Deslocamento, Concatenação, "Matching". | ||

:* Sobrecarga de operadores | :* Sobrecarga de operadores | ||

| − | |||

| − | |||

| − | |||

| − | |||

| + | {{collapse top | Conversor de Binário para BCD}} | ||

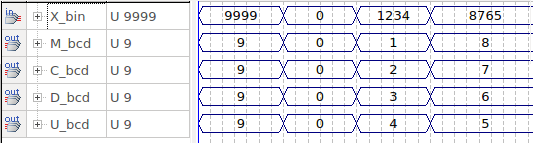

| + | *Considere um número decimal entre 000 e 999. Usando operadores predefinidos, obtenha na saída os dígitos decimais separados. | ||

| + | :*Escreva o código VHDL e analise o número de elementos lógicos necessários. | ||

| + | :*Faça a simulação funcional do circuito. | ||

| + | <center> [[Arquivo:tb_bin2bcd.jpg]]<br> '''Fig. 20 - Simulação da conversão de binário para BCD''' </center> | ||

| + | :*Compare sua implementação com os outros estudantes e analise as diferenças, observe o código RTL, o número de elementos lógicos e também o tempo de propagação. | ||

| + | ::Para separar os dígitos decimais do número de entrada pense nos operadores de "+", "-", "*", "/", "REM" e "MOD", shift. | ||

| + | ::Para facilitar os testes e a troca de informações entre as equipes, a ENTITY deverá ter o seguinte formato: | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | entity bin2bcd is | ||

| + | port ( | ||

| + | X_bin : in std_logic_vector(9 downto 0); -- 000 a 999 | ||

| + | C_bcd : out std_logic_vector(3 downto 0); -- Centena | ||

| + | D_bcd : out std_logic_vector(3 downto 0); -- Dezena | ||

| + | U_bcd : out std_logic_vector(3 downto 0)); -- Unidade | ||

| + | |||

| + | end entity; | ||

| + | |||

| + | architecture example of bin2bcd is | ||

| + | --declaração de sinais auxiliares | ||

| + | |||

| + | begin | ||

| + | --descrição do hardware | ||

| + | |||

| + | end architecture; | ||

| + | </syntaxhighlight> | ||

| + | :: Note que com ''X_bin'' 10 bits é possível representar números sem sinal entre ''0'' e <math> 2^{10}-1 </math>. No entanto, os testes devem ser limitados a números entre 000 e 999, pois não há especificação para valores maiores que 999. | ||

| + | :: Existe um algoritmo [https://en.wikipedia.org/wiki/Double_dabble Double Dabble] que possibilita fazer essa conversão com menos hardware. | ||

| + | ::Dica para converter de INTEGER para STD_LOGIC_VECTOR de 4 bits. | ||

| + | M_bcd <= std_logic_vector(to_unsigned(M,4)); | ||

| + | {{collapse bottom}} | ||

:: Ver pag. 91 a 108 de <ref name="PEDRONI2010b"/> | :: Ver pag. 91 a 108 de <ref name="PEDRONI2010b"/> | ||

| − | + | ;Aula 14 (28 mar): | |

| − | ;Aula | + | *Atributos em VHDL. |

:* Atributos de síntese: | :* Atributos de síntese: | ||

| − | ::* | + | ::* '''ATTRIBUTE enum_encoding''' [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_enum_encoding.htm] |

| − | ::* chip_pin [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_chip.htm] | + | ::* '''ATTRIBUTE chip_pin''' [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_chip.htm] |

| − | ::* keep [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_keep.htm] | + | ::* '''ATTRIBUTE keep''' [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_keep.htm] |

:::* Exemplo 4.4: Delay line (Síntese e Simulação temporal sem o com o atributo keep) | :::* Exemplo 4.4: Delay line (Síntese e Simulação temporal sem o com o atributo keep) | ||

:::* Exemplo 5.8 Gerador de Pulsos estreitos | :::* Exemplo 5.8 Gerador de Pulsos estreitos | ||

| − | + | ::* '''ATTRIBUTE preserve''' [http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_preserve.htm], [http://quartushelp.altera.com/15.0/mergedProjects/logicops/logicops/def_preserve_fanout_free_node.htm]. | |

| − | + | ::* '''ATTRIBUTE noprune'''[http://quartushelp.altera.com/15.0/mergedProjects/hdl/vhdl/vhdl_file_dir_noprune.htm]. | |

| − | + | :::* Exemplo 4.5: Registros redundantes (Síntese sem e com os atributos keep, preserve e noprune) | |

| − | :* | ||

| − | |||

| − | ::* noprune. | ||

| − | :::* Exemplo 4.5: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

ENTITY redundant_registers IS | ENTITY redundant_registers IS | ||

| Linha 380: | Linha 550: | ||

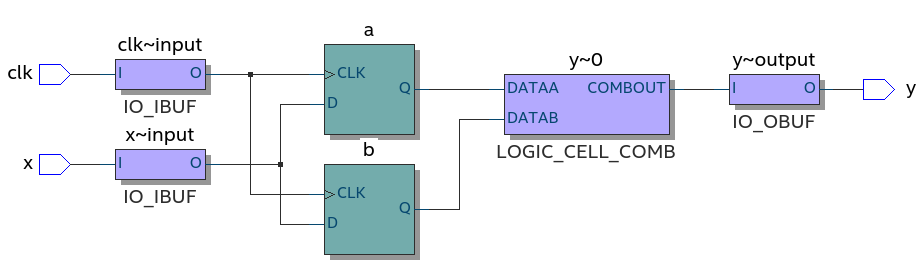

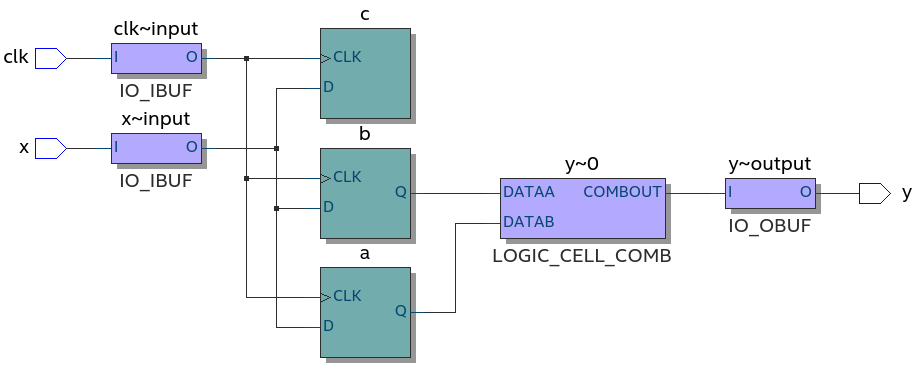

<center> [[Arquivo:Ex4_5_NoAttribute.png | Sem Attribute| 400 px]] <br> '''Fig 12. Technology Map do Circuito sem Attribute'''</center> | <center> [[Arquivo:Ex4_5_NoAttribute.png | Sem Attribute| 400 px]] <br> '''Fig 12. Technology Map do Circuito sem Attribute'''</center> | ||

<center> [[Arquivo:Ex4_5_PreserveAttribute.png| Preserve (or Keep) Attribute |400 px]] <br> '''Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep) '''</center> | <center> [[Arquivo:Ex4_5_PreserveAttribute.png| Preserve (or Keep) Attribute |400 px]] <br> '''Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep) '''</center> | ||

| − | <center> [[Arquivo:Ex4_5_NopruneAttribute.png| Noprune Attribute| 400 px]] <br> '''Fig 14. Technology Map do Circuito com Attribute Noprune '''</center> | + | <center> [[Arquivo:Ex4_5_NopruneAttribute.png| Noprune Attribute| 400 px]] <br> '''Fig 14. Technology Map do Circuito com Attribute Noprune '''</center>:: Ver pag. 91 a 111 de <ref name="PEDRONI2010b"/> |

| − | :* | + | ;Aula 15 (2 abr): |

| − | :* | + | *Atributos em VHDL. |

| − | ::*Exemplo de uso no pacote numeric_std.vhd | + | :* Atributos predefinidos: tipo escalar e enumerados; tipo array; de sinal; |

| + | :* Exemplo 4.2 (Simulação funcional) | ||

| + | :* Atributos definidos pelo usuário; | ||

| + | Uso da instrução ALIAS. | ||

| + | ::*Exemplo de uso de alias no pacote numeric_std.vhd | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is | function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is | ||

| Linha 401: | Linha 575: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

:: '''NOTA''': No exemplo acima, a CONSTANT L_LEFT recebe o tamanho do parâmetro (L), que pode ser qualquer. Esse tamanho é utilizado para criar dois ALIAS para os parâmetros L e R, utilizando uma indexação (L_LEFT DOWNTO 0). Com isso é possível dentro do FOR-LOOP criar os circuitos que realizam as operações lógicas que realizam a operação de soma. | :: '''NOTA''': No exemplo acima, a CONSTANT L_LEFT recebe o tamanho do parâmetro (L), que pode ser qualquer. Esse tamanho é utilizado para criar dois ALIAS para os parâmetros L e R, utilizando uma indexação (L_LEFT DOWNTO 0). Com isso é possível dentro do FOR-LOOP criar os circuitos que realizam as operações lógicas que realizam a operação de soma. | ||

| − | |||

| − | |||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

{{collapse top| Unidade 4 - Código Concorrente}} | {{collapse top| Unidade 4 - Código Concorrente}} | ||

| + | |||

===Unidade 4 - Código Concorrente=== | ===Unidade 4 - Código Concorrente=== | ||

| + | ;Aula 15 - cont (2 abr): | ||

*Código Concorrente. | *Código Concorrente. | ||

:* Uso de Operadores | :* Uso de Operadores | ||

| − | :* WHEN, | + | :* instrução WHEN-ELSE (WHEN) |

| + | <syntaxhighlight lang=vhdl> | ||

| + | <optional_label>: <target> <= | ||

| + | <value> when <condition> else | ||

| + | <value> when <condition> else | ||

| + | <value> when <condition> else | ||

| + | ... | ||

| + | <value>; | ||

| + | </syntaxhighlight> | ||

| + | ::*Importante: O último ELSE deve cobrir todos os demais valores para evitar a criação de LATCHES. | ||

| + | ::* No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Conditional Signal Assignment]''' | ||

| + | |||

| + | :* instrução WITH-SELECT-WHEN (SELECT) | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | <optional_label>: with <expression> select | ||

| + | <target> <= | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | <value> when <choices>, | ||

| + | ... | ||

| + | <value> when others; | ||

| + | </syntaxhighlight> | ||

| + | ::*Importante: O valor deve cobrir todas as demais possibilidades usando WHEN OTHERS para evitar a criação de LATCHES. | ||

| + | ::* No QuartusII existe um template pronto para ser utilizado em: '''[Edit > Insert Template > Language templates = VHDL (+) > Constructs (+) > Concurrent Statemens (+) > Selected Signal Assignment]'''. Mas ATENÇÃO, faltam as virgulas após cada escolha. | ||

| + | |||

:* Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com portas, com WHEN-ELSE, com WITH-SELECT) | :* Exemplo 5.1 + 5.2 mux: com 3 tipos de arquiteturas (com portas, com WHEN-ELSE, com WITH-SELECT) | ||

::Verifique os três circuitos considerando as entradas x0 a x3 e a saída y com apenas um elemento. | ::Verifique os três circuitos considerando as entradas x0 a x3 e a saída y com apenas um elemento. | ||

| Linha 416: | Linha 613: | ||

:::No caso do uso de WHEN-ELSE e WITH-SELECT é só alterar o tamanho dos vetores STD_LOGIC_VECTOR. | :::No caso do uso de WHEN-ELSE e WITH-SELECT é só alterar o tamanho dos vetores STD_LOGIC_VECTOR. | ||

:::Qual é a solução para a descrição com portas? | :::Qual é a solução para a descrição com portas? | ||

| − | |||

| − | |||

| − | |||

:* Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION. | :* Para selecionar uma entre várias arquiteturas para a mesma ENTITY use a CONFIGURATION. | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 427: | Linha 621: | ||

END CONFIGURATION; | END CONFIGURATION; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| + | ::Ver pag. 121 a 127 de <ref name="PEDRONI2010b"/> | ||

| + | ;Aula 16 (4 abr): | ||

*Código Concorrente. | *Código Concorrente. | ||

| − | :*Exemplo de uso de operadores e SELECT. | + | :*Exemplo de uso de operadores e instrução WITH-SELECT. |

::Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU). | ::Exemplo 5.3 - Unidade de Lógica e Aritmética (ALU). | ||

| − | ::* | + | ::*Fazer as seguintes alterações do código da ALU: |

:::* Inclusão de um sinal que indica "erro" quando ocorre ''overflow''/''underflow'' nas operações de soma, incremento ou decremento. | :::* Inclusão de um sinal que indica "erro" quando ocorre ''overflow''/''underflow'' nas operações de soma, incremento ou decremento. | ||

:::* Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro. | :::* Inclusão de um circuito que satura o sinal no máximo positivo ou negativo nas situações de erro. | ||

:::* Teste da ALU usando simulação funcional. | :::* Teste da ALU usando simulação funcional. | ||

| − | ;Aula | + | ;Aula 17 (9 abr): |

| − | :* Uso | + | :* Uso da instrução FOR-GENERATE |

<i><code> | <i><code> | ||

label: FOR identificador IN faixa GENERATE | label: FOR identificador IN faixa GENERATE | ||

| Linha 447: | Linha 643: | ||

</syntaxhighlight> </i> | </syntaxhighlight> </i> | ||

| − | ::Exemplo 5.4 - Decodificador genérico de endereços. | + | ;Aula 18 (11 abr): |

| + | *Código Concorrente. | ||

| + | :*Exemplo 5.4 - Decodificador genérico de endereços. | ||

| + | :*Ver pag. 127 a 134 de <ref name="PEDRONI2010b"/> | ||

| − | + | * Implementação de circuitos aritméticos com operadores. | |

| − | |||

| − | |||

:* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar a biblioteca ''numeric_std''. | :* Para o uso dos operadores o mais adequado é utilizar o padrão industrial '''STD_LOGIC_VECTOR'''. Internamente os valores das portas devem ser convertidos ou para valores '''INTEGER''' ou para '''UNSIGNED'''/'''SIGNED'''. para tal é necessário utilizar a biblioteca ''numeric_std''. | ||

:* Também é fundamental considerar a faixa de valores coberta por <math> N </math> bits. Para tipos '''UNSIGNED''' a faixa é de <math> 0 </math> até <math> 2^{N}-1 </math>, enquanto que para '''SIGNED''' a faixa é de <math> -2^{N-1} </math> até <math> 2^{N-1}-1 </math>. Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED. | :* Também é fundamental considerar a faixa de valores coberta por <math> N </math> bits. Para tipos '''UNSIGNED''' a faixa é de <math> 0 </math> até <math> 2^{N}-1 </math>, enquanto que para '''SIGNED''' a faixa é de <math> -2^{N-1} </math> até <math> 2^{N-1}-1 </math>. Assim com 3 bits é possível representar valores entre -4 até 3 com um tipo SIGNED e 0 até 7 com um tipo UNSIGNED. | ||

| Linha 482: | Linha 679: | ||

::Exemplo 5.7 - Somador/Subtrator Recomendado. | ::Exemplo 5.7 - Somador/Subtrator Recomendado. | ||

| + | :*Ver pag. 139 a 140 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula | + | ;Aula 19 (13 abr): |

*Código Concorrente. | *Código Concorrente. | ||

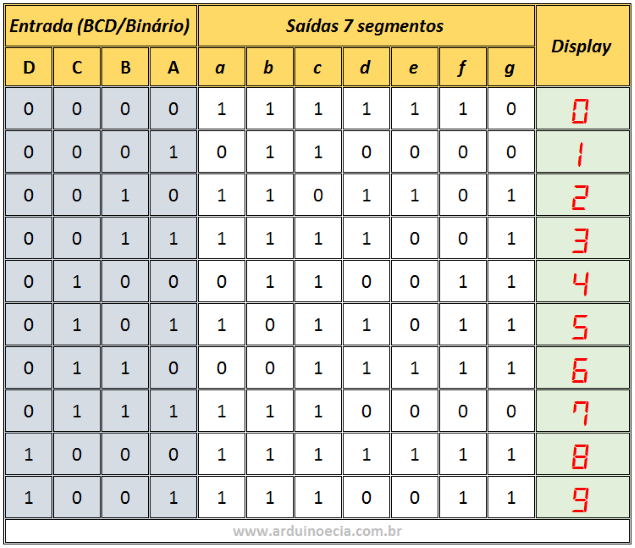

| − | + | * Exemplo Conversor de binário para sete segmentos. | |

| − | : | + | :* Implemente em VHDL um conversor de binário para sete segmentos, conforme a tabela abaixo. |

| − | :: | + | <center> |

| + | :[[Arquivo:bin2ssd.png | 400px]] | ||

| − | + | :<small>FONTE: https://www.arduinoecia.com.br/2016/08/cd4511-arduino-display-7-segmentos.html</small> | |

| − | + | </center> | |

| − | + | :* Use como entrada x[3..0] no lugar de D..A | |

| − | + | :* Use como saídas y[0..6] no lugar de a..g | |

| − | + | :* Se a entrada estiver com um valor binário entre 10 e 15, a saída deverá mostra a letra "E". | |

| − | + | :* O circuito deverá ser programado no kit DE2-115. Use as chaves SW0 a SW4 para as entradas, e o Display HEX0 para a saída. | |

| − | + | :* Para facilitar a visualização adicione 1 LED em cada entrada para mostrar o estado das chaves. Use o LED imediatamente acima da chave. | |

| − | + | :* Antes de programar confira se os pinos não usados estão no terceiro estado. | |

| − | + | :* Verifique se o display acende conforme indicado na tabela. | |

| − | + | :* Se houver algum problema corrija o código e reprograme o hardware. | |

| − | + | :* Consulte também a página [[Display de 7 segmentos]] | |

| − | |||

| − | |||

| − | |||

| − | |||

| − | : | ||

| − | |||

| − | : | ||

| − | |||

| − | : | ||

| − | |||

| − | : | ||

| − | |||

| − | :* | ||

| − | : | ||

| − | : | ||

| − | : | ||

| − | |||

| − | |||

| − | * | ||

{{collapse bottom}} | {{collapse bottom}} | ||

{{collapse top| Unidade 5 - Código Sequencial}} | {{collapse top| Unidade 5 - Código Sequencial}} | ||

| + | |||

===Unidade 5 - Código Sequencial=== | ===Unidade 5 - Código Sequencial=== | ||

| − | ;Aula 20 ( | + | ;Aula 20 (16 abr): |

| − | |||

| − | |||

| − | |||

*Código Sequencial. | *Código Sequencial. | ||

:*Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial | :*Diferenças entre código concorrente e sequencial <=> circuitos combinacional e sequencial | ||

| Linha 559: | Linha 737: | ||

END IF [rótulo]; | END IF [rótulo]; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | :*Exemplos: | |

| − | + | ::* DFFs with Reset and Clear (Variação Ex 6.1), | |

| + | ::* Contador Básico 0-N (baseado no Ex.6.2) | ||

| + | ::* Registrador de deslocamento (Ex.6.3) | ||

:*Ver pag. 161 a 160 de <ref name="PEDRONI2010b"/> | :*Ver pag. 161 a 160 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula 21 e 22 ( | + | ;Aula 21 e 22 (18 e 23 abr): |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

*Código Sequencial. | *Código Sequencial. | ||

:*Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | :*Instrução '''WAIT''': WAIT UNTIL, WAIT FOR (simulação apenas), WAIT ON (não implementada no Quartus II). | ||

| + | ::Recomenda-se utilizar a lista de sensibilidade do PROCESS e a instrução IF no lugar do WAIT. | ||

::Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ::Algumas instruções de '''WAIT''' serão utilizadas na criação de '''TestBench''' em VHDL para a simulação com o '''MODELSIM'''. | ||

| + | |||

:*Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | :*Instruções do tipo '''LOOP''': LOOP incondicional, FOR-LOOP, WHILE-LOOP, NEXT, EXIT | ||

| − | |||

::*LOOP incondicional: | ::*LOOP incondicional: | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 630: | Linha 798: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | + | :* Exemplos: | |

| + | ::*Carry-Ripple Adder (FOR-LOOP) (Ex 6.4) | ||

| + | ::* Leading Zeros (LOOP com EXIT) (Ex 6.5) | ||

| + | :*Ver pag. 161 a 164 de <ref name="PEDRONI2010b"/> | ||

| + | |||

| + | ;Aula 23 (25 abr): | ||

| + | Revisão - UN2, UN3, UN4 | ||

| + | |||

| + | ;Aula 24 (27 abr): | ||

| + | Avaliação A1 - UN2, UN3, UN4 | ||

| + | |||

| + | ;Aula 25 (2 mai): | ||

| + | *Código Sequencial. | ||

:*Instrução '''CASE''' | :*Instrução '''CASE''' | ||

<syntaxhighlight lang=vhdl> | <syntaxhighlight lang=vhdl> | ||

| Linha 643: | Linha 823: | ||

END CASE; | END CASE; | ||

</syntaxhighlight> | </syntaxhighlight> | ||

| − | :* | + | :* Contador de 0 a 9 segundos com saída SSD (Ex 6.6). |

| − | ::* | + | ::* v1 - Unir os códigos anteriormente realizados para o contador de 0 a 9 (código sequencial), e o conversor de binário para sete segmentos (código concorrente) |

| − | :*Ver | + | ::* v2 - mudar o conversor para SSD de forma a usar código sequencial (CASE), acrescentar uma saída ERROR que indique quando o número é fora da faixa de 0-9. |

| + | ::* v3 - incluir o conversor para SSD de forma a usar código sequencial (CASE)no mesmo processo que tem o contador de 0-9. | ||

| + | |||

| + | :* Contador de 0 a max com saída em código Gray (Exercício 6.2). | ||

| + | |||

| + | ;Aula 26 (7 mai): | ||

| + | *Especificação do relógio HH:MM:SS | ||

| + | *Uso do Modelsim para simulação. | ||

| + | :*Ver [[Seguindo o tutorial da ALTERA para o MODELSIM]], para utilizar o básico do MODELSIM. | ||

| + | :* [http://www.vhdl.us/Book_VHDL_2ed_unrestricted/Pedroni_VHDL_2ed_tutorial_ModelSim_10.1d_v2.pdf Pedroni VHDL 2ed Tutorial of ModelSim 10.1d] | ||

| + | :* [https://www.youtube.com/watch?v=Z8whdGa7RtY ModelSim Video Tutorial] - Kirk Weedman | ||

| + | :* [[Documentação do ModelSim]], para conhecer mais a fundo o MODELSIM. | ||

| − | ;Aula | + | ;Aula 27 e 28 (9 e 11 mai): |

| − | * | + | * Implementação do relógio HH:MM:SS |

| − | ::* | + | * Simulação do relógio com ModelSim. Na simulação definir o clk1sec com duração de 1 segundo e iniciar o circuito com um reset durante 10 ps. |

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

| − | |||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | {{collapse top | + | {{collapse top| Unidade 6 - Projeto a nível de Sistema}} |

| + | |||

===Unidade 6 - Projeto a nível de Sistema=== | ===Unidade 6 - Projeto a nível de Sistema=== | ||

| − | ; Aula | + | ; Aula 29 (14 mai): |

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | :* O '''PACKAGE''' e '''PACKAGE BODY''': onde declarar e como usar. | ||

| Linha 679: | Linha 857: | ||

:* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | :* Ver pag. 201 a 208 de <ref name="PEDRONI2010b"/> | ||

| − | ; Aula | + | ; Aula 30 (16 mai): |

*Projeto a nível de Sistema. | *Projeto a nível de Sistema. | ||

:* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | :* Criação de '''COMPONENT''' redimensionáveis. GENERIC -> '''GENERIC MAP''' | ||

| Linha 687: | Linha 865: | ||

:* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | :* Ver pag. 208 a 213 de <ref name="PEDRONI2010b"/> | ||

| − | ;Aula 29,30 ( | + | :* Uso da instrução '''CONFIGURATION'''. |

| + | ::* Ligação direta: ARCHITECTURE-ENTITY. | ||

| + | ::* Ligação da instanciação dos componentes: COMPONENT-ENTITY(ARCHITECTURE). | ||

| + | |||

| + | ;Aula 31 e 32 (21 e 23 mai): | ||

| + | * Implementação do relógio HH:MM:SS usando componentes. | ||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo '''generic N''' | ||

| + | entity div_clk is | ||

| + | entrada clk_in | ||

| + | saída clk_out | ||

| + | : Componente 2 - Contador de 00 a 99 com saída em BCD, com o valor final configurável pelos '''generic U e D''' | ||

| + | entity countBCD99 is | ||

| + | entradas clk_in | ||

| + | saídas bcd_u, bcd_d | ||

| + | |||

| + | : Componente 3 - Conversor de BCD para SSD, com um porta '''ac_ccn''' para selecionar Anodo ou Catodo Comum. | ||

| + | entity bcd2ssd is | ||

| + | entradas bcd, ac_ccn | ||

| + | saídas ssd | ||

| + | |||

| + | * Simulação do relógio com ModelSim. Na simulação definir o clk1sec com duração de 1 segundo e iniciar o circuito com um reset durante 10 ps. | ||

| + | *Após verificar que o circuito funciona "simulado", configurar o FPGA do kit DE2-115 para implementar este circuito. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. Utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0-5[0-6]: PIN_G18 - PIN_H22 ...). Note que a chave usada para o rst é normalmente alta, e portanto é necessário acrescentar um inversor a esta entrada. | ||

| + | |||

| + | ;Aula 33 a 35 (25 a 30 mai): | ||

| + | As aulas foram suspensas pela direção do campus em funções da '''GREVE DOS CAMINHONEIROS''' | ||

| + | |||

| + | ;Aula 36 a 38 (4 a 8 jun): | ||

| + | * Implementação de um serializador e um deserializador usando componentes. | ||

| + | : Componente 1 - Divisor de Clock, con o valor da divisão configurável pelo '''generic N''' | ||

| + | entity div_clk is | ||

| + | entrada clk_in | ||

| + | saída clk_out | ||

| + | : Componente 2 - Registrador de deslocamento com entrada serial e paralelo e saída serial e paralelo com N FF, configurável pelo '''generic N''' | ||

| + | entity shift_reg is | ||

| + | entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in | ||

| + | saídas d_out[N-1..0], s_out | ||

| + | |||

| + | : Componente 3 - Porta paralela com N entradas, configurável pelo '''generic N'''. | ||

| + | entity port_par is | ||

| + | entradas clk_in, rst, ena, d_in[N-1..0] | ||

| + | saídas d_out[N-1..0] | ||

| + | |||

| + | * Simulação do serializador e deserializador com ModelSim. | ||

| + | * Integração dos dois componentes em um único componente. | ||

| + | |||

| + | <!-- | ||

| + | ;Aula 27 (7 mai): | ||

| + | * Correção da Avaliação A1. [https://moodle.sj.ifsc.edu.br/mod/assign/view.php?id=3062&action=grading Conceitos na Avaliação] | ||

| + | * Implementar um circuito de relógio que conte HH:MM:SS. | ||

| + | |||

| + | :::*PROBLEMA: Uso de um período de clock de 20 ns => 50 MHz, verificar a impossibilidade prática de uma simulação deste circuito (1 segundo => 5 minutos de simulação), devido ao tamanho do contador (count1) que conta de 0 a 50M-1. | ||

| + | :::*SOLUÇÃO: modificar o contador para um valor maximo menor (0 a 5-1), e a mesmo tempo mudar o período de clock para 200 ms => 5 Hz. Notar que a simulação é extremamente rápida neste caso. | ||

| + | :::*Após verificar que o circuito funciona "simulado", configurar o FPGA do kit DE2-115 para implementar este circuito. As informações necessárias estão em [[Preparando para gravar o circuito lógico no FPGA]]. Utilize os pinos (clk = CLOCK_50: PIN_Y2, rst = KEY[0]: PIN_M23, ssd = HEX0[0-6]: PIN_G18 - PIN_H22). Note que a chave usada para o rst é normalmente alta, e portanto é necessário acrescentar um inversor a esta entrada. | ||

| + | <syntaxhighlight lang=vhdl> | ||

| + | -- Renomeie a porta rst para rst_in. | ||

| + | PORT ( | ||

| + | clk, rst_in : IN BIT; | ||

| + | |||

| + | --Crie um sinal interno para inverter o clock | ||

| + | ARCHITECTURE counter OF slow_counter IS | ||

| + | signal rst : BIT; | ||

| + | BEGIN | ||

| + | rst <= not rst_in; | ||

| + | </syntaxhighlight> | ||

| + | :::*Programe o FPGA usando o programador e verifique se a contagem está correta (a cada segundo). | ||

| + | --> | ||

| + | |||

| + | <!-- | ||

| + | ;Aula 29,30 ( ): | ||

*Código Sequencial. | *Código Sequencial. | ||

* Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando um COMPONENT contador BCD de 00 a 99. Instancie 3 COMPONENTES para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ser implementados com um COMPONENT "bin2ssd" que converte o número 0 a 9 em bits do código SSD. | * Projeto de relógio HH:MM:SS com conversor para 7 segmentos. Implementar um relógio usando um COMPONENT contador BCD de 00 a 99. Instancie 3 COMPONENTES para implementar a hora, o minuto e o segundo. O relógio deve contar de 00:00:00 até 23:59:59. Os mostradores de 7 segmentos devem ser implementados com um COMPONENT "bin2ssd" que converte o número 0 a 9 em bits do código SSD. | ||

| Linha 693: | Linha 939: | ||

:* Implementar o relógio no kit DE2-115 (opcional) - neste caso é necessário incluir um divisor de clock antes do contador de segundo. | :* Implementar o relógio no kit DE2-115 (opcional) - neste caso é necessário incluir um divisor de clock antes do contador de segundo. | ||

| − | + | --> | |

| − | + | <!-- | |

| − | |||

| − | |||

| − | |||

| − | |||

::*Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada. | ::*Exercício 28.1: Inserir as duas soluções de ARCHITECTURE do exercício EX 6.10 (Timer de dois digitos) em uma única ENTITY. Utilizar CONFIGURATION para fazer a ligação com a arquitetura desejada. | ||

| Linha 810: | Linha 1 052: | ||

:*Uso de '''FUNCTION''' e '''PROCEDURE'''. | :*Uso de '''FUNCTION''' e '''PROCEDURE'''. | ||

::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ::*Exercícios: 9.1 a 9.4, 9.6 a 9.9 | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| − | {{collapse | + | {{collapse top| Unidade 7 - Testbench}} |

| − | ===Unidade 7=== | + | ===Unidade 7 - Testbench=== |

| − | ; Aula | + | ; Aula 40 (13 jun): |

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

:*Tipos de simulação: | :*Tipos de simulação: | ||

| Linha 836: | Linha 1 080: | ||

:*Ver também [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_func_sim.htm Performing a Functional Simulation with the ModelSim-Altera Software], e [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_timing_sim.htm Performing a Timing Simulation with the ModelSim-Altera Software]. | :*Ver também [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_func_sim.htm Performing a Functional Simulation with the ModelSim-Altera Software], e [http://quartushelp.altera.com/13.1/mergedProjects/eda/simulation/modelsim/eda_pro_msim_timing_sim.htm Performing a Timing Simulation with the ModelSim-Altera Software]. | ||

| + | <!-- | ||

; Aula 36 (30 Mai): | ; Aula 36 (30 Mai): | ||

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

| Linha 842: | Linha 1 087: | ||

[[Arquivo:slr_adder.png]] | [[Arquivo:slr_adder.png]] | ||

</center> | </center> | ||

| + | --> | ||

::*Criar um testbench em VHDL para testar cada componente (SOMADOR, o SRL_L) e o sistema final. (faça com o test bench teste no minimo o funcionamento da entrada LOAD para 2 entradas diferentes de DADOS, o RESET, o SOMADOR e o funcionamento do SRL_L para uma sequencia de pelo menos N clocks, onde N é o número de bits das entradas. | ::*Criar um testbench em VHDL para testar cada componente (SOMADOR, o SRL_L) e o sistema final. (faça com o test bench teste no minimo o funcionamento da entrada LOAD para 2 entradas diferentes de DADOS, o RESET, o SOMADOR e o funcionamento do SRL_L para uma sequencia de pelo menos N clocks, onde N é o número de bits das entradas. | ||

| Linha 924: | Linha 1 170: | ||

</syntaxhighlight> | </syntaxhighlight> | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | <!-- | |

; Aula 37 (2 Jun): | ; Aula 37 (2 Jun): | ||

*Simulação de sistemas digitais com Modelsim e testbench em VHDL | *Simulação de sistemas digitais com Modelsim e testbench em VHDL | ||

:* Tempo livre para a resolução do Exercicio proposto. | :* Tempo livre para a resolução do Exercicio proposto. | ||

| + | --> | ||

| + | {{collapse bottom}} | ||

| − | ===Unidade 8=== | + | {{collapse top| Unidade 8 - Maquinas de Estado Finitas}} |

| − | ; Aula | + | |

| + | ===Unidade 8 - Maquinas de Estado Finitas=== | ||

| + | ; Aula 46 (29 jun): | ||

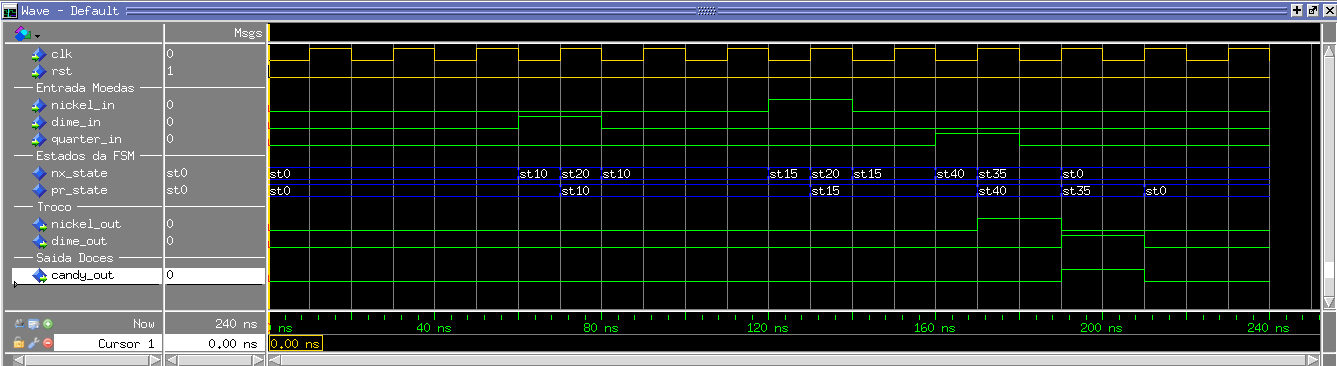

*Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

:* O que é uma FSM - Finite State Machine | :* O que é uma FSM - Finite State Machine | ||

| Linha 999: | Linha 1 249: | ||

:: Ver pag. 277 a 35 de <ref name="PEDRONI2010b"/> | :: Ver pag. 277 a 35 de <ref name="PEDRONI2010b"/> | ||

| − | |||

*Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | *Introdução ao Projeto de Maquinas de Estado Finitas (FSM) em VHDL | ||

:* Exemplo 11.1 Controlador de uma máquina de Venda | :* Exemplo 11.1 Controlador de uma máquina de Venda | ||

| Linha 1 009: | Linha 1 258: | ||

:* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | :* Exercício: Altere a FSM para vender doces que custam 30 centavos. Considere que as moedas aceitas são 5, 10, 25 e 50 centavos. Desenho primeiro a FSM e em seguida implemente-a em VHDL e faça a simulação. | ||

| − | + | {{collapse bottom}} | |

| − | |||

| − | + | {{collapse top| Unidade 9 - Projeto Final (Semáforo)}} | |

| − | + | ||

| − | : | + | ===Unidade 9 - Projeto Final (Semáforo)=== |

| − | + | ;Aula 39 (11 jun): | |

| + | * Projeto Final - Especificação do sistema de controle de tráfego | ||

| − | + | ;Aula 41 a 44 (20 jun a 25 jun): | |

| − | ;Aula | ||

* Projeto Final - Sistema de controle de tráfego | * Projeto Final - Sistema de controle de tráfego | ||

| − | :* trabalho desenvolvido em equipes ( | + | :* trabalho desenvolvido em equipes |

| − | :* durante as aulas o professor | + | :* durante as aulas o professor está disponível para o esclarecimento de dúvidas e orienta o trabalho |

| + | |||

| + | ;Aula 46 (27 jun): | ||

| + | As aulas foram suspensas pela direção do campus em funções do '''JOGO DO BRASIL NA COPA 2018''' | ||

| + | |||

| + | ;Aula 47 a 49 (30 jun a 02 jul): | ||

| + | * Projeto Final - Sistema de controle de tráfego | ||

| + | :* trabalho desenvolvido em equipes | ||

| + | :* durante as aulas o professor está disponível para o esclarecimento de dúvidas e orienta o trabalho | ||

| + | |||

| + | ;Aula 50 (04 jul): | ||

| + | * Projeto Final - Sistema de controle de tráfego | ||

| + | :*Apresentação do sistema no kit FPGA pelas equipes. | ||

| + | |||

| + | ;Aula 51 (06 jul): | ||

| + | As aulas foram suspensas pela direção do campus em funções do '''JOGO DO BRASIL NA COPA 2018''' | ||

| − | + | {{collapse bottom}} | |

| − | |||

| − | |||

==Avaliações== | ==Avaliações== | ||

| − | *Avaliação A1 - Unidade 2 a 4 ( | + | *Avaliação A1 - Unidade 2 a 4 (27/04/2018) - Local: Lab Redes II. |

*Avaliação A2 - Unidade 5 a 7 (XX/XX/2018) - Local: Lab Redes II. | *Avaliação A2 - Unidade 5 a 7 (XX/XX/2018) - Local: Lab Redes II. | ||

::As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues [[Media:VHDL_QRC-Qualis.pdf | VHDL QUICK REFERENCE CARD]] e [[Media:VHDL1164_QRC-Qualis.pdf | VHDL 1164 PACKAGES QUICK REFERENCE CARD]], e as [[Media:Tabelas_Pedroni.pdf | tabelas das figuras 3.6, 3.10 e 4.1]] do livro do Pedroni. Dica use também como fonte de consulta os '''templates''' do Quartus. | ::As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues [[Media:VHDL_QRC-Qualis.pdf | VHDL QUICK REFERENCE CARD]] e [[Media:VHDL1164_QRC-Qualis.pdf | VHDL 1164 PACKAGES QUICK REFERENCE CARD]], e as [[Media:Tabelas_Pedroni.pdf | tabelas das figuras 3.6, 3.10 e 4.1]] do livro do Pedroni. Dica use também como fonte de consulta os '''templates''' do Quartus. | ||

| Linha 1 035: | Linha 1 296: | ||

*Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle | *Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle | ||

| + | |||

| + | *Projeto Final APF | ||

| + | {{collapse top | expand = true | APF - Projeto Final - Sistema de controle de tráfego (Entrega e prazos ver Moodle)}} | ||

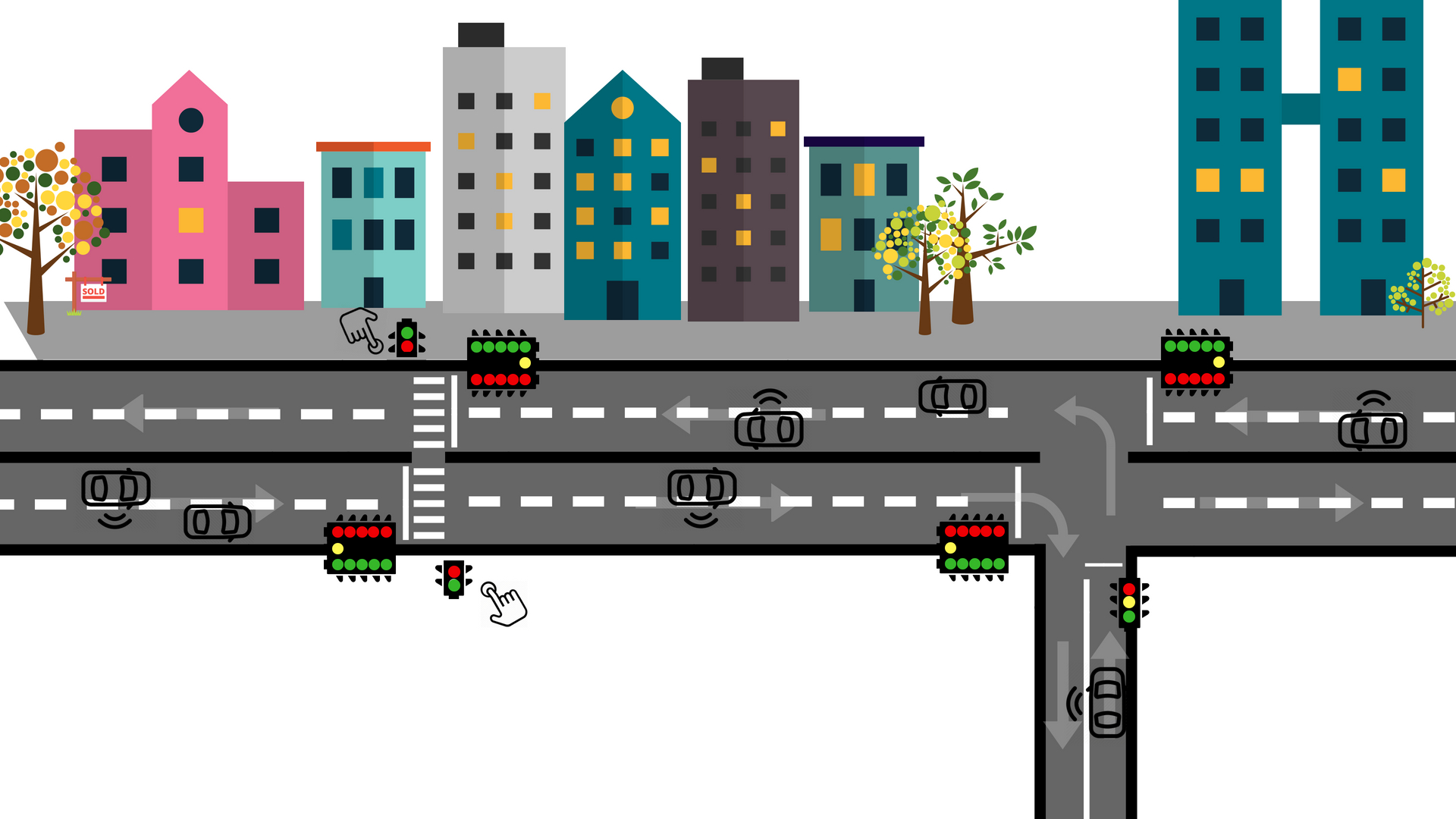

| + | * Cada aluno (ou equipe de 2 alunos) deverá desenvolver um sistema de controle de tráfego das vias indicadas na figura abaixo: | ||

| + | <center> | ||

| + | [[Arquivo:APF_DLP29006_2018_1.png | 600 px]] | ||

| + | :Figura 1 - Diagrama de descrição física dos semáforos. | ||

| + | :FONTE: Maria Fernanda Tutui | ||

| + | </center> | ||

| + | * O primeiro semáforo (esquerda) é para a passagem de pedestres. Ele é controlado por botões que os pedestres acionam do lado 1 ou 2 da passagem de pedestres para solicitar a travessia. Ao ser acionado o semáforo pode: 1) liberar imediatamente a passagem do pedestre se não houver veículos circulando na via 1 e via 2. 2) aguardar até 2 minutos se houver veículos circulando. A descrição exata do funcionamento deve ser obtida com o cliente durante a entrevista de requisitos. | ||

| + | :* Os grupos focais das vias 1 e 2 devem ser do tipo progressivo, mas podem funcionar de forma imediata quando não há veículos circulando. | ||

| + | :* A passagem de pedestre tem: 1) um botão em cada lado da passagem; 2) um sistema para iluminação noturna da passagem de pedestre, 3) dois grupos focais simples (GFS) com lampadas verdes e vermelhas. | ||

| + | ::* A iluminação deve acender assim que um botão for acionado e apagar novamente quando o GFS passar de verde para vermelho. | ||

| + | ::* O tempo de passagem do pedestre é configurável (default = 15 s). | ||

| + | :* Se não houver acionamento do botão de solicitação de passagem do pedestre, as vias 1 e 2 devem permanecer sempre em verde. | ||

| + | * O segundo semáforo (direita) é para controlar a entrada dos veículos da via 3 para as vias 1 e 2. Ele é controlado por um sensor de veículo na via 3. Ao passar um veículo no sensor, o semáforo pode: 1) liberar imediatamente a passagem do veículo da via 3 se não houver veículos circulando na via 1 e via 2. 2) aguardar até 2 minutos se houver veículos circulando. A descrição exata do funcionamento deve ser obtida com o cliente durante a entrevista de requisitos. | ||

| + | :* a conversão a direita da via 2 para a via 4 é livre indicada por um grupo focal apropriado. | ||

| + | |||

| + | <center> | ||

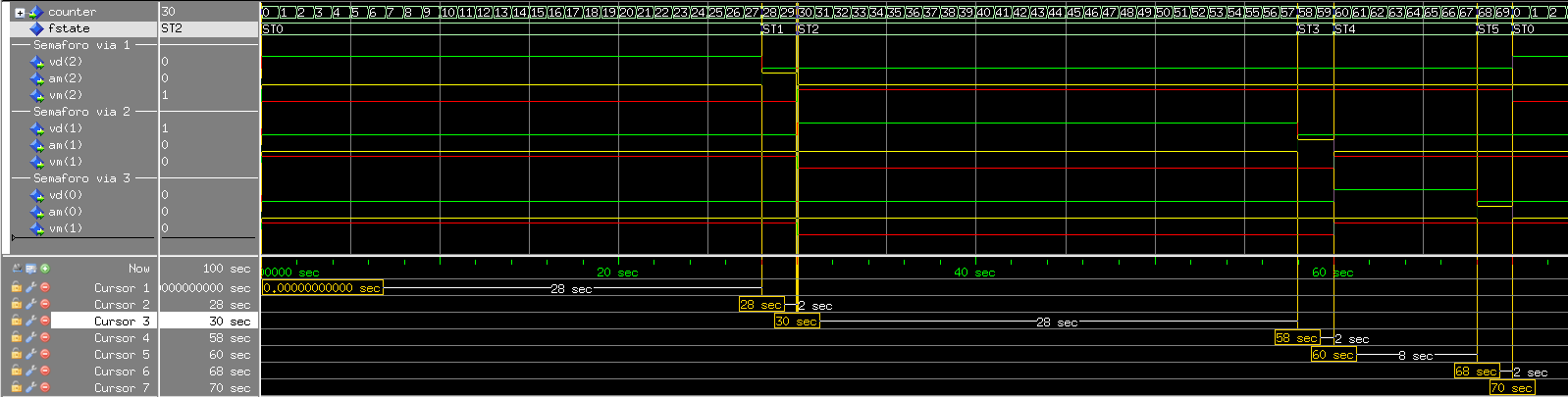

| + | :[[Arquivo:APF_DLP29006_2017_1_times.png | 900 px]] | ||

| + | :Figura 2 - Funcionamento de um GFS. | ||

| + | </center> | ||

| + | |||

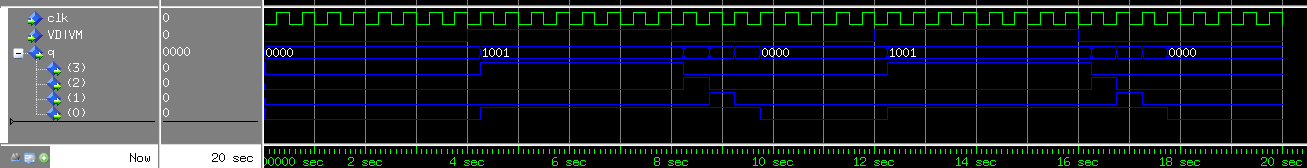

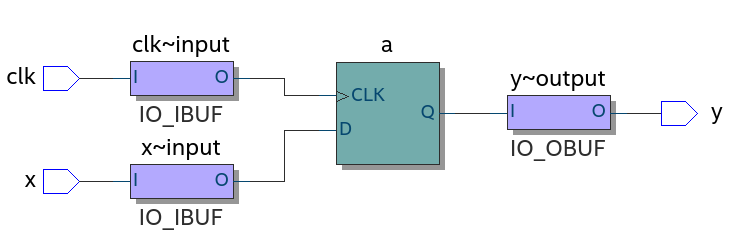

| + | * O sistema de controle do semáforo poderá ser descrito através de máquinas de estado finita (FSM). Os grupos focais simples (GFS) deverão ser acionados por um sinal VD_VM. Os grupos focais progressivos (GFP) para as cores verde e vermelho, deverão ser controlados por um subsistema adicional que controla o acendimento e desligamento dos leds a partir de um sinal VD_VM. | ||

| + | * Na figura abaixo está representado em AZUL o funcionamento do GFP, onde VD_VM é a saída da máquina de estado e os sinais "q(3..0)" são os acionamentos das lampadas do GFP. | ||

| + | <center> | ||

| + | [[Arquivo:APF_DLP29006_2017_1_times_GFP.png | 900 px]] | ||

| + | :Figura 3 - Funcionamento de uma das colunas (verde ou vermelho) do GFP. | ||

| + | </center> | ||

| + | <!-- | ||

| + | * Para a FSM sugere-se utilizar GENERIC para definir os tempos de verde de cada VIA, e o tempo de amarelo de todas as VIAS. | ||

| + | * Sugere-se fazer uma versão V1 do sistema apenas com GFS em todas as vias. Na versão V2 as vias 1 e 2 devem receber GFPs. | ||

| + | :* Ao modificar o tipo de grupo focal recomenda-se mudar o projeto da maquina de estado de modo que passe a incluir o tempo progressivo de (4 x 0.5 seg). | ||

| + | --> | ||

| + | * O sistema de controle das FSM será baseado no valor de um timer de segundos externo a FSM (conforme mostrado em aula). | ||

| + | * O sistema poderá ser implementado no kit FPGA DE2-115 (ou Mercurio IV) usando os leds disponíveis ou pinos da GPIO para acionar leds externos. | ||

| + | * Os sinais de relógio necessários deverão ser obtidos a partir do sinal de clock da placa de 50MHz. Durante as simulações esse circuito deverá ter seu valor alterado de modo a viabilizar a simulação. | ||

| + | * O arquivo QAR do projeto, e os arquivos .do e o testbench .vht para o MODELSIM devem ser enviados antecipadamente; | ||

| + | * Escreva um relatório técnico contendo os resultados em no máximo 10 paginas A4. O relatório além das tabelas com os dados de frequência máxima, número de componente, número de pinos, deverá conter a figura dos circuitos RTL da ENTITY top level com uma explicação do seu funcionamento. Também devem ser apresentadas as simulações funcionais e uma análise textual dos resultados obtidos. A descrição da função dos pinos no Kit DE2-115 também deve ser feita. | ||

| + | {{collapse bottom}} | ||

<!-- | <!-- | ||

| Linha 1 170: | Linha 1 471: | ||

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo. | Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo. | ||

| − | |||

{{collapse top | EL0 - Resolução dos exercícios do Cap 2}} | {{collapse top | EL0 - Resolução dos exercícios do Cap 2}} | ||

*Resolva os exercícios do capítulo 2 (1, 2, 3) pag. 28 a 30 | *Resolva os exercícios do capítulo 2 (1, 2, 3) pag. 28 a 30 | ||

| Linha 1 217: | Linha 1 517: | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | <!-- | ||

{{collapse top | EL1 - Uso de tipos de dados e operadores}} | {{collapse top | EL1 - Uso de tipos de dados e operadores}} | ||

*Implementar em VHDL um circuito que efetue a operação <math>\ y = a^2 + 2*a*b + 5 </math>, utilizando portas do tipo STD_LOGIC_VECTOR para valores de entrada <math>\ a </math> e <math>\ b </math> com sinal e ocupando 4 bits, utilize na saída <math>\ y </math> 8 bits. | *Implementar em VHDL um circuito que efetue a operação <math>\ y = a^2 + 2*a*b + 5 </math>, utilizando portas do tipo STD_LOGIC_VECTOR para valores de entrada <math>\ a </math> e <math>\ b </math> com sinal e ocupando 4 bits, utilize na saída <math>\ y </math> 8 bits. | ||

| Linha 1 224: | Linha 1 525: | ||

*Determine o número de elementos lógicos e pinos e verifique o código RTL obtido. Compare com os colegas. | *Determine o número de elementos lógicos e pinos e verifique o código RTL obtido. Compare com os colegas. | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | --> | |

{{collapse top | EL2 - Resolução dos exercícios do Cap 3}} | {{collapse top | EL2 - Resolução dos exercícios do Cap 3}} | ||

*Resolva os exercícios do capítulo 3 (1, 2, '''9''', 11, 12, 13, 14-17, '''18''', '''20''', '''22''', 23-30) pag. 81 a 89 | *Resolva os exercícios do capítulo 3 (1, 2, '''9''', 11, 12, 13, 14-17, '''18''', '''20''', '''22''', 23-30) pag. 81 a 89 | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| + | <!-- | ||

{{collapse top | AR2- Conversor de Binário para BCD}} | {{collapse top | AR2- Conversor de Binário para BCD}} | ||

*Considere um número decimal entre 000 e 999. Usando operadores predefinidos, obtenha na saída os dígitos decimais separados. | *Considere um número decimal entre 000 e 999. Usando operadores predefinidos, obtenha na saída os dígitos decimais separados. | ||

| Linha 1 260: | Linha 1 562: | ||

M_bcd <= std_logic_vector(to_unsigned(M,4)); | M_bcd <= std_logic_vector(to_unsigned(M,4)); | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | --> | |

{{collapse top | EL4 - Resolução dos exercícios do Cap 4}} | {{collapse top | EL4 - Resolução dos exercícios do Cap 4}} | ||

*Resolva os exercícios do capítulo 4 (4-8, '''9''', 10-11, 13, 15-16, '''17''' ) pag. 115 a 120 | *Resolva os exercícios do capítulo 4 (4-8, '''9''', 10-11, 13, 15-16, '''17''' ) pag. 115 a 120 | ||

| Linha 1 268: | Linha 1 570: | ||

*Resolva os exercícios do capítulo 5 (1, 2, '''3''', 4, '''6''', '''7''', 8-9, '''10-11''', '''14-16''', 17-18, '''19''' ) pag. 144 a 150 | *Resolva os exercícios do capítulo 5 (1, 2, '''3''', 4, '''6''', '''7''', 8-9, '''10-11''', '''14-16''', 17-18, '''19''' ) pag. 144 a 150 | ||

{{collapse bottom}} | {{collapse bottom}} | ||

| − | + | <!-- | |

{{collapse top | AR3 - Unidade somadora e subtratora}} | {{collapse top | AR3 - Unidade somadora e subtratora}} | ||

*Implementar em VHDL uma unidade de processamento que efetue a operação de soma ou subtração considerando valores SIGNED e UNSIGNED. As características do circuito são: | *Implementar em VHDL uma unidade de processamento que efetue a operação de soma ou subtração considerando valores SIGNED e UNSIGNED. As características do circuito são: | ||

Edição atual tal como às 01h15min de 6 de julho de 2018

MURAL DE AVISOS E OPORTUNIDADES DA ÁREA DE TELECOMUNICAÇÕES

Registro on-line das aulas

| Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS |

|---|

Unidade 2 - Introdução ao VHDL e ambienta EDA - QUARTUS

library library_name; use library_name.package)name.all;

entity entity_name is

[generic (

cons_name1: const_type const_value;

cons_name2: const_type const_value;

...

cons_nameN: const_type const_value);]

[port (

signal_name1: mode signal_type;

signal_name2: mode signal_type;

...

signal_nameN: mode signal_type);]

[declarative_part]

[begin

statement_part]

end [entity] [entity_name];

architecture arch_name of entity_name is [declarative_part] begin statement_part end [architecture] [arch_name];

library std;

use std.standard.all;

entity nand_gate is

port (a, b: in bit; x: out bit);

end entity;

architecture nome_arch of nand_gate is

begin

x <= a nand b;

end architecture;

-- Declaração das bibliotecas e pacotes

LIBRARY ieee;

USE ieee.std_logic_1164.all;

-- Especificação de todas as entradas e saídas do circuito

ENTITY flip_flop IS

PORT (d, clk, rst: IN STD_LOGIC;

q: OUT STD_LOGIC);

END;

-- Descrição de como o circuito deve funcionar

ARCHITECTURE flip_flop OF flip_flop IS

BEGIN

PROCESS (clk, rst)

BEGIN

IF (rst='1') THEN

q <= '0';

ELSIF (clk'EVENT AND clk='1') THEN

q <= d;

END IF;

END PROCESS;

END;

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/std

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/ieee

ls /opt/altera/13.0sp1/quartus/libraries/vhdl/mentor/arithmetic (Mentor Graphics) ls /opt/altera/13.0sp1/quartus/libraries/vhdl/synopsys/ieee (Synopsys)

ls /opt/altera/16.0/quartus/libraries/vhdl/ieee/2008

Note que na simulação funcional a mudança da saída Q ocorre no instante em que ocorre a borda de subida do clock ou no momento do reset. No entanto, no caso da simulação com timing, existe um atraso de ~6ns nestas mudanças. IMPORTANTE: Na prática normalmente não é necessário fazer a simulação temporal, pois através do Time Quest Report é possivel verificar se o circuito atende as restrições de tempo.

create_clock -name CLK50MHz -period 50MHz [get_ports {*}]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

ENTITY registered_comp_add IS

PORT (clk: IN STD_LOGIC;

a, b: IN INTEGER RANGE 0 TO 7;

reg_comp: OUT STD_LOGIC;

reg_sum: OUT INTEGER RANGE 0 TO 15);

END;

ARCHITECTURE circuit OF registered_comp_add IS

SIGNAL comp: STD_LOGIC;

SIGNAL sum: INTEGER RANGE 0 TO 15;

BEGIN

comp <= '1' WHEN a>b ELSE '0';

sum <= a + b;

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

reg_comp <= comp;

reg_sum <= sum;

END IF;

END PROCESS;

END;

|

| Unidade 3 - Tipos de Dados e Operadores em VHDL | |||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||||

|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|---|

Unidade 3 - Tipos de Dados e Operadores em VHDL

package standard is

type boolean is (false,true);

type bit is ('0', '1');

type severity_level is (note, warning, error, failure);

type integer is range -2147483647 to 2147483647;

type real is range -1.0E308 to 1.0E308;

type time is range -2147483648 to 2147483647

units

fs;

ps = 1000 fs;

ns = 1000 ps;

us = 1000 ns;

ms = 1000 us;

sec = 1000 ms;

min = 60 sec;

hr = 60 min;

end units;

subtype natural is integer range 0 to integer'high;

subtype positive is integer range 1 to integer'high;

type string is array (positive range <>) of character;

type bit_vector is array (natural range <>) of bit;

PACKAGE std_logic_1164 IS

TYPE std_ulogic IS ( 'U', -- Uninitialized

'X', -- Forcing Unknown

'0', -- Forcing 0

'1', -- Forcing 1

'Z', -- High Impedance

'W', -- Weak Unknown

'L', -- Weak 0

'H', -- Weak 1

'-' -- Don't care

);

TYPE std_ulogic_vector IS ARRAY ( NATURAL RANGE <> ) OF std_ulogic;

SUBTYPE std_logic IS resolved std_ulogic;

TYPE std_logic_vector IS ARRAY ( NATURAL RANGE <>) OF std_logic;

x = "1----" -- não funciona em VHDL

std_match(x, "1----") -- funciona em VHDL

Ver pag. 60 a 73 de [2]

LIBRARY ieee;

USE ieee.std_logic_1164.all;

USE ieee.numeric_std.all;

ENTITY operadores IS

PORT (

a, b: IN STD_LOGIC_VECTOR(3 DOWNTO 0);

mult: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

div: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sum: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

sub: OUT STD_LOGIC_VECTOR(? DOWNTO 0);

);

END ENTITY;

ARCHITECTURE type_conv_arch OF operadores IS

BEGIN

-- Inserir o código e definir o tamanho das saidas.

END ARCHITECTURE;

ENTITY redundant_registers IS

PORT (

clk, x: IN BIT;

y: OUT BIT);

END ENTITY;

ARCHITECTURE arch OF redundant_registers IS

SIGNAL a, b, c: BIT;

-- NORMAL -- 1 LE

--ATTRIBUTE preserve: BOOLEAN;

--ATTRIBUTE preserve OF a, b, c: SIGNAL IS TRUE; -- 2 LE

--ATTRIBUTE noprune: BOOLEAN;

--ATTRIBUTE noprune OF a, b, c: SIGNAL IS TRUE; --3 LE

--ATTRIBUTE keep: BOOLEAN;

--ATTRIBUTE keep of a,b,c: SIGNAL IS TRUE;

BEGIN

PROCESS (clk)

BEGIN

IF (clk'EVENT AND clk='1') THEN

a <= x;

b <= x;

c <= x;

END IF;

END PROCESS;

y <= a AND b;

END ARCHITECTURE;

Após a compilação do código acima, observe o número de elementos lógicos obtidos, observe o Technology Map dos circuitos gerados e verifique a localização dos FFs no Chip Planner.  Fig 12. Technology Map do Circuito sem Attribute  Fig 13. Technology Map do Circuito com Attribute Preserve (or Keep)  Fig 14. Technology Map do Circuito com Attribute Noprune

Uso da instrução ALIAS.

function ADD_UNSIGNED (L, R: UNSIGNED; C: STD_LOGIC) return UNSIGNED is

constant L_LEFT: INTEGER := L'LENGTH-1;

alias XL: UNSIGNED(L_LEFT downto 0) is L;

alias XR: UNSIGNED(L_LEFT downto 0) is R;

variable RESULT: UNSIGNED(L_LEFT downto 0);

variable CBIT: STD_LOGIC := C;

begin

for I in 0 to L_LEFT loop

RESULT(I) := CBIT xor XL(I) xor XR(I);

CBIT := (CBIT and XL(I)) or (CBIT and XR(I)) or (XL(I) and XR(I));

end loop;

return RESULT;

end ADD_UNSIGNED;

|

| Unidade 4 - Código Concorrente |

|---|

Unidade 4 - Código Concorrente

<optional_label>: <target> <=

<value> when <condition> else

<value> when <condition> else

<value> when <condition> else

...

<value>;

<optional_label>: with <expression> select

<target> <=

<value> when <choices>,

<value> when <choices>,

<value> when <choices>,

...

<value> when others;

CONFIGURATION which_mux OF mux IS

FOR Operator_only END FOR;

-- FOR with_WHEN END FOR;

-- FOR with_SELECT END FOR;

END CONFIGURATION;

|

| Unidade 5 - Código Sequencial |

|---|

Unidade 5 - Código Sequencial

[rótulo:] PROCESS [(lista_de_sensibilidade)] [IS]

[parte_declarativa]

BEGIN

afirmação_sequencial;

afirmação_sequencial;

...

END PROCESS [rótulo];

[rótulo:] IF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSIF condição THEN

afirmação_sequencial;

afirmação_sequencial;

...

ELSE

afirmação_sequencial;

afirmação_sequencial;

...

END IF [rótulo];

[rótulo:] LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] FOR identificador IN faixa LOOP

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] WHILE condição LOOP -- Executa as "afirmações enquanto a "condição" for verdadeira

afirmação_sequencial;

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

EXIT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, termina o "LOOP"

afirmação_sequencial;

...

END LOOP [rótulo];

[rótulo:] [FOR identificador IN faixa] LOOP

afirmação_sequencial;

NEXT [rótulo] [WHEN condição]; -- Se a "condição" é verdadeira, não executa as linhas até a linha "END LOOP"

-- e incrementa o "identificador".

afirmação_sequencial;

...

END LOOP [rótulo];

Revisão - UN2, UN3, UN4

Avaliação A1 - UN2, UN3, UN4

[rótulo:] CASE expressão IS

WHEN valor => atribuições; -- valor único

...

WHEN valor1 | valor2 | ... | valorN => atribuições; -- lista de valores

...

WHEN valor1 TO valor2 => atribuições; -- faixa de valores

...

END CASE;

|

| Unidade 6 - Projeto a nível de Sistema |

|---|

Unidade 6 - Projeto a nível de Sistema

entity div_clk is entrada clk_in saída clk_out

entity countBCD99 is entradas clk_in saídas bcd_u, bcd_d

entity bcd2ssd is entradas bcd, ac_ccn saídas ssd

As aulas foram suspensas pela direção do campus em funções da GREVE DOS CAMINHONEIROS

entity div_clk is entrada clk_in saída clk_out

entity shift_reg is entradas clk_in, rst_in, ena_in, d_in[N-1..0], s_in saídas d_out[N-1..0], s_out

entity port_par is entradas clk_in, rst, ena, d_in[N-1..0] saídas d_out[N-1..0]

|

| Unidade 7 - Testbench | ||||||||

|---|---|---|---|---|---|---|---|---|

Unidade 7 - Testbench

/opt/altera/13.0sp1/modelsim_ae/bin/vsim

vsim

/opt/altera/13.0/quartus/modelsim_ae/linux/vsim

|

| Unidade 8 - Maquinas de Estado Finitas |

|---|

Unidade 8 - Maquinas de Estado Finitas

LIBRARY ieee;

USE ieee.std_logic_1164.ALL;

----------------------------------------------------------

ENTITY < entity_name > IS

PORT (

clk, rst : IN STD_LOGIC;

input : IN < data_type > ;

output : OUT < data_type >);

END < entity_name > ;

----------------------------------------------------------

ARCHITECTURE < architecture_name > OF < entity_name > IS

TYPE state IS (A, B, C, ...);

SIGNAL pr_state, nx_state : state;

ATTRIBUTE ENUM_ENCODING : STRING; --optional attribute

ATTRIBUTE ENUM_ENCODING OF state : TYPE IS "sequential";

BEGIN

------Logica Sequencial da FSM:------------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

pr_state <= A;

ELSIF (clk'EVENT AND clk = '1') THEN

pr_state <= nx_state;

END IF;

END PROCESS;

------Logica Combinacional da FSM:------------

PROCESS (pr_state, input)

BEGIN

CASE pr_state IS

WHEN A =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= B;

...

ELSE

nx_state <= A;

END IF;

WHEN B =>

output <= < value > ;

IF (input =< value >) THEN

nx_state <= C;

...

ELSE

nx_state <= B;

END IF;

WHEN ...

END CASE;

END PROCESS;

------Seção de Saída (opcional):-------

PROCESS (clk, rst)

BEGIN

IF (rst = '1') THEN

new_output <= < value > ;

ELSIF (clk'EVENT AND clk = '1') THEN --or clk='0'

new_output <= output;

END IF;

END PROCESS;

END < architecture_name > ;

|

| Unidade 9 - Projeto Final (Semáforo) |

|---|

Unidade 9 - Projeto Final (Semáforo)

As aulas foram suspensas pela direção do campus em funções do JOGO DO BRASIL NA COPA 2018

As aulas foram suspensas pela direção do campus em funções do JOGO DO BRASIL NA COPA 2018 |

Avaliações

- Avaliação A1 - Unidade 2 a 4 (27/04/2018) - Local: Lab Redes II.

- Avaliação A2 - Unidade 5 a 7 (XX/XX/2018) - Local: Lab Redes II.

- As avaliações A1 e A2 são com consulta apenas as folhas de consulta entregues VHDL QUICK REFERENCE CARD e VHDL 1164 PACKAGES QUICK REFERENCE CARD, e as tabelas das figuras 3.6, 3.10 e 4.1 do livro do Pedroni. Dica use também como fonte de consulta os templates do Quartus.

- Recuperação R1-2 - Unidade 2 a 7 (XX/XX/2018) - Local: Lab Redes II.

- Ao final das avaliações o aluno deverá enviar a avaliação para a plataforma moodle ou email moecke AT ifsc.edu.br com os arquivos solicitados.

- Entrega dos Atividades Extraclasse ao longo do semestre AE0 a AE(N). A entrega, detalhes e prazos de cada AE serão indicados na plataforma Moodle

- Projeto Final APF

| APF - Projeto Final - Sistema de controle de tráfego (Entrega e prazos ver Moodle) |

|---|

|

ESTUDOS SEM ENTREGA DE DOCUMENTAÇÃO

Os exemplos e exercícios essenciais estão destacados em negrito na listagens abaixo.

| EL0 - Resolução dos exercícios do Cap 2 |

|---|

especificado.

---------------------------------------

-- File: mux.vdh

---------------------------------------

-- Declaração das Bibliotecas e Pacotes

--

LIBRARY ieee;

USE _________________________ ;

---------------------------------------

-- Especificação das entradas e saídas e nome da ENTITY

ENTITY mux IS

PORT (

__ , __ : ___ STD_LOGIC_VECTOR (7 DOWNTO 0);

sel : IN ____________________________ ;

___ : OUT STD_LOGIC_VECTOR (7 DOWNTO 0));

END _____ ;

---------------------------------------

ARCHITECTURE example OF _____ IS

BEGIN

PROCESS (a, b, ____ )

BEGIN

IF (sel = "00") THEN

c <= "00000000";

ELSIF (__________) THEN

c <= a;

_____ (sel = "10") THEN

c <= __;

ELSE

c <= (OTHERS => '__');

END ___ ;

END _________ ;

END _________ ;

---------------------------------------

|

| EL2 - Resolução dos exercícios do Cap 3 |

|---|

|

| EL4 - Resolução dos exercícios do Cap 4 |

|---|

|

| EL5 - Resolução dos exercícios do Cap 5 |

|---|

|

Referências Bibliográficas:

- ↑ PEDRONI, Volnei A. Eletrônica digital moderna e VHDL; 1ª ed. Rio de Janeiro:Elsevier, 2010. 619p. . ISBN 9788535234657

- ↑ 2,00 2,01 2,02 2,03 2,04 2,05 2,06 2,07 2,08 2,09 2,10 2,11 2,12 2,13 2,14 2,15 PEDRONI, Volnei A. Circuit Design and Simulation with VHDL; 2ª ed. Massachusetts-EUA:MIT, 2010. 608 p. ISBN 9780262014335