Mudanças entre as edições de "DIG222802 AULA03"

| (22 revisões intermediárias pelo mesmo usuário não estão sendo mostradas) | |||

| Linha 3: | Linha 3: | ||

Os contadores são circuitos que utilizam flip-flops e são aplicados, principalmente, em contagens, diversas, divisão de frequência, medição de frequência e tempo, divisão de formas de onda e conversão de analógico para digital. Estes circuitos sequenciais são divididos basicamente em duas categorias: | Os contadores são circuitos que utilizam flip-flops e são aplicados, principalmente, em contagens, diversas, divisão de frequência, medição de frequência e tempo, divisão de formas de onda e conversão de analógico para digital. Estes circuitos sequenciais são divididos basicamente em duas categorias: | ||

| − | *Contadores assíncronos e | + | *Contadores assíncronos; e |

*Contadores síncronos. | *Contadores síncronos. | ||

| − | Basicamente a principal diferença entre eles é que o síncrono utiliza um sinal de clock comum a todos os | + | Basicamente a principal diferença entre eles é que o síncrono utiliza um sinal de ''clock'' comum a todos os flip-flops e o assíncrono possuí um sinal de ''clock'' que é dividido até o último flip-flops. |

==Contadores assíncronos== | ==Contadores assíncronos== | ||

| − | Estes contadores também são conhecidos como seriais ou contadores por pulsação (''ripple counter''). Tal nome advém do fato dos flip-flops (FF) do contador não serem disparados diretamente pelo sinal de clock. Cada FF é disparado pela saída do FF anterior. Esta característica torna estes contadores limitados em termos de velocidade, pois o tempo de ativação (tempo de resposta) é dado aproximadamente pela soma dos tempos de atraso de propagação de cada FF. | + | Estes contadores também são conhecidos como seriais ou contadores por pulsação (''ripple counter''). Tal nome advém do fato dos flip-flops (FF) do contador não serem disparados diretamente pelo sinal de ''clock''. Cada FF é disparado pela saída do FF anterior. Esta característica torna estes contadores limitados em termos de velocidade, pois o tempo de ativação (tempo de resposta) é dado aproximadamente pela soma dos tempos de atraso de propagação de cada FF. |

| Linha 17: | Linha 17: | ||

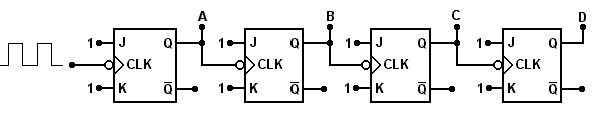

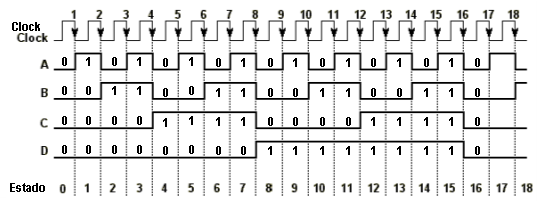

Um circuito típico de um contador assíncrono crescente construído com FF do tipo JK é mostrado na Figura 1. Os FF JK estão com ambas entradas J e K permanentemente em nível alto, estando configuradas portanto como FF tipo T. Cada FF é disparado pela saída do FF anterior. A Figura 2 mostra o diagrama de tempo para esse contador. | Um circuito típico de um contador assíncrono crescente construído com FF do tipo JK é mostrado na Figura 1. Os FF JK estão com ambas entradas J e K permanentemente em nível alto, estando configuradas portanto como FF tipo T. Cada FF é disparado pela saída do FF anterior. A Figura 2 mostra o diagrama de tempo para esse contador. | ||

| + | |||

[[Imagem:fig14_DIG222802.png|center|500px]] | [[Imagem:fig14_DIG222802.png|center|500px]] | ||

| Linha 42: | Linha 43: | ||

|- | |- | ||

| 0 | | 0 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| 0 | | 0 | ||

|- | |- | ||

| 1 | | 1 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| 1 | | 1 | ||

|- | |- | ||

| 2 | | 2 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 2 |

| 2 | | 2 | ||

|- | |- | ||

| 3 | | 3 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 3 |

| 3 | | 3 | ||

|- | |- | ||

| 4 | | 4 | ||

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 4 |

| 4 | | 4 | ||

|- | |- | ||

| 5 | | 5 | ||

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 5 |

| 5 | | 5 | ||

|- | |- | ||

| 6 | | 6 | ||

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 6 |

| 6 | | 6 | ||

|- | |- | ||

| 7 | | 7 | ||

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 7 |

| 7 | | 7 | ||

|- | |- | ||

| 8 | | 8 | ||

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 8 |

| 8 | | 8 | ||

|- | |- | ||

| 9 | | 9 | ||

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 9 |

| 9 | | 9 | ||

|- | |- | ||

| 10 | | 10 | ||

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 10 |

| 10 | | 10 | ||

|- | |- | ||

| 11 | | 11 | ||

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 11 |

| 11 | | 11 | ||

|- | |- | ||

| 12 | | 12 | ||

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 12 |

| 12 | | 12 | ||

|- | |- | ||

| 13 | | 13 | ||

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 13 |

| 13 | | 13 | ||

|- | |- | ||

| 14 | | 14 | ||

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 14 |

| 14 | | 14 | ||

|- | |- | ||

| 15 | | 15 | ||

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| − | | | + | | 15 |

| 15 | | 15 | ||

|- | |- | ||

| 16 | | 16 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| 0 | | 0 | ||

|- | |- | ||

| 17 | | 17 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 1 |

| 1 | | 1 | ||

|- | |- | ||

| 18 | | 18 | ||

| − | | | + | | 0 |

| − | | | + | | 0 |

| − | | | + | | 1 |

| − | | | + | | 0 |

| − | | | + | | 2 |

| 2 | | 2 | ||

|} | |} | ||

| − | |||

| − | O contador tem como conteúdo (estado interno) a contagem do número de transições negativas do clock, de forma que quando ocorre uma transição o conteúdo é incrementado de uma unidade. O conteúdo do contador é dado pelo número binário DCBA, onde A é o bit LSB (bit menos significativo) e D é o bit MSB (bit mais significativo). | + | O contador tem como conteúdo (estado interno) a contagem do número de transições negativas do ''clock'', de forma que quando ocorre uma transição o conteúdo é incrementado de uma unidade. O conteúdo do contador é dado pelo número binário DCBA, onde A é o bit LSB (bit menos significativo) e D é o bit MSB (bit mais significativo). |

| − | O modulo (MOD) de um contador é o seu número de estados distintos, portanto, o módulo de um contador com N FF pode ser no máximo o número de possíveis saídas (<math>2^N</math>). A Tabela mostra os estados de contagem de um contador assíncrono com 4 FF (4 bits). Podemos perceber que após 16 transições de | + | O modulo (MOD) de um contador é o seu número de estados distintos, portanto, o módulo de um contador com N FF pode ser no máximo o número de possíveis saídas (<math>2^N</math>). A Tabela mostra os estados de contagem de um contador assíncrono com 4 FF (4 bits). Podemos perceber que após 16 transições de ''clock'' o contador reinicia a contagem. Por isso, este contador é de MOD-16, ou seja, tem 16 estados distintos (0000b até 1111b). |

| − | Nos contadores assíncronos, a | + | Nos contadores assíncronos, a frequência do ''clock'' é dividida por 2 em cada FF, ou seja: na saída A temos ''clock/2'', e na saída D temos ''clock/16''. Portanto, os contadores assíncronos são divisores de frequência e no último FF a frequência de ''clock'' é dividida pelo módulo do contador. |

===Contadores com módulo < <math>2^N</math>=== | ===Contadores com módulo < <math>2^N</math>=== | ||

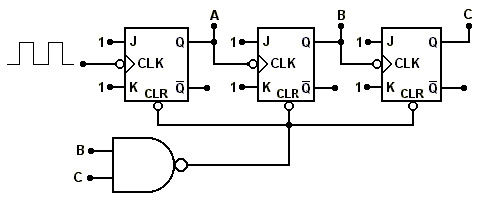

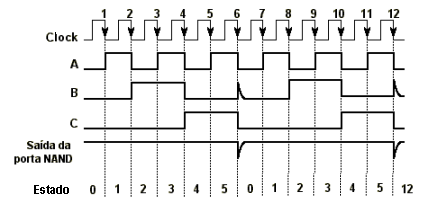

| − | Para obter um contador com módulo menor do que <math>2^N</math> é necessário adicionar um circuito decodificador para reiniciar a contagem antes de chegar ao valor máximo (ou mínimo). A Figura 3 mostra um contador MOD-6. Se não houvesse a porta NAND ligada nas entradas CLR dos FF o módulo do contador seria 8. A sequência de estados do contador MOD-6 é mostrada nas Figura 4 e Tabela 2. Note que na transição do 6º clock o estado do contador passa temporariamente pelo estado (110b), o qual faz com que a saída da porta NAND passe para o estado BAIXO, causando o CLR nos FF, e consequentemente levando o contador para o estado (000b). | + | Para obter um contador com módulo menor do que <math>2^N</math> é necessário adicionar um circuito decodificador para reiniciar a contagem antes de chegar ao valor máximo (ou mínimo). A Figura 3 mostra um contador MOD-6. Se não houvesse a porta NAND ligada nas entradas CLR dos FF o módulo do contador seria 8. A sequência de estados do contador MOD-6 é mostrada nas Figura 4 e Tabela 2. Note que na transição do 6º ''clock'' o estado do contador passa temporariamente pelo estado (110b), o qual faz com que a saída da porta NAND passe para o estado BAIXO, causando o CLR nos FF, e consequentemente levando o contador para o estado (000b). |

| − | [[Imagem:fig16_DIG222802.png|center| | + | [[Imagem:fig16_DIG222802.png|center|500px]] |

<center> | <center> | ||

Figura 3 - Contador assíncrono com módulo < <math>2^N</math>. | Figura 3 - Contador assíncrono com módulo < <math>2^N</math>. | ||

| Linha 296: | Linha 296: | ||

| 2 | | 2 | ||

|} | |} | ||

| − | |||

*Não atingível. | *Não atingível. | ||

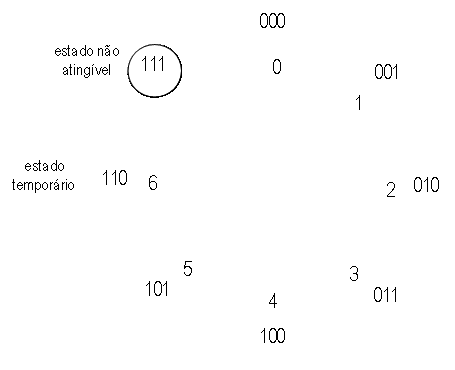

| − | O diagrama de transição de estados do contador de 3 bits MOD-6 é mostrado na Figura 5. No diagrama de transição as linhas contínuas indicam a passagem pelos estados estáveis (000b 101b) e as linhas tracejadas indicam a passagem pelos estados temporários (110b). O estado (111b)embora possível não é atingível. | + | O diagrama de transição de estados do contador de 3 bits MOD-6 é mostrado na Figura 5. No diagrama de transição as linhas contínuas indicam a passagem pelos estados estáveis (000b 101b) e as linhas tracejadas indicam a passagem pelos estados temporários (110b). O estado (111b) embora possível não é atingível. |

| Linha 316: | Linha 315: | ||

::Exemplo: 12 = 1100b D = 1 e C = 1, conectar D e C a porta NAND. | ::Exemplo: 12 = 1100b D = 1 e C = 1, conectar D e C a porta NAND. | ||

| − | ==Contadores de década== | + | ===Contadores de década=== |

Os contadores de década (ou decádico) são contadores que possuem 10 estados distintos, não importando a sequência de contagem. Quando um contador decádico realiza a contagem em sequência binária crescente de 0000b a 1001b (0 a 9), ele é chamado de contador BCD. | Os contadores de década (ou decádico) são contadores que possuem 10 estados distintos, não importando a sequência de contagem. Quando um contador decádico realiza a contagem em sequência binária crescente de 0000b a 1001b (0 a 9), ele é chamado de contador BCD. | ||

| + | ===Contador assíncrono decrescente=== | ||

| + | |||

| + | Os contadores que contam progressivamente a partir do zero são denominados contadores crescentes (ou ascendentes). Já os contadores que contam do valor máximo até zero são chamados decrescentes (ou descendentes). A Figura 6 mostra a configuração para um contador decrescente construído com FF do tipo JK. A configuração é semelhante à do contador crescente, com a única diferença de cada FF é disparado pela saída '''Q\''' no lugar de '''Q'''. | ||

| + | [[Imagem:fig19_DIG222802.png|center|500px]] | ||

| + | <center> | ||

| + | Figura 6 - Contador assíncrono decrescente. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | A Figura 7 mostra o diagrama de tempo das saídas do contador, enquanto que a Tabela 3 mostra a contagem das transições do ''clock'' e os estados correspondentes ao contador. O diagrama de estados do contador decrescente é mostrado na Figura 8 (b), enquanto que o diagrama do contador crescente é mostrado na Figura 8 (a). Note que nos dois diagramas o contador passa por todos os estados. | ||

| + | |||

| + | |||

| + | [[Imagem:fig20_DIG222802.png|center|350px]] | ||

| + | <center> | ||

| + | Figura 7 - Diagrama de tempo do contador assíncrono decrescente. | ||

| + | </center> | ||

| + | |||

| + | |||

| + | |||

| + | {| border="1" cellpadding="5" cellspacing="0" style="text-align: center;" | ||

| + | |+'''Tabela 2 - Contador assíncrono crescente MOD-6''' | ||

| + | |- | ||

| + | ! style="background:#4069e1; width: 20px;" | Clock | ||

| + | ! style="background:#4069e1; width: 20px;" | C | ||

| + | ! style="background:#4069e1; width: 20px;" | B | ||

| + | ! style="background:#4069e1; width: 20px;" | A | ||

| + | ! style="background:#4069e1; width: 20px;" | Decimal | ||

| + | ! style="background:#4069e1; width: 20px;" | Estado | ||

| + | |- | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 7 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 2 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 6 | ||

| + | | 2 | ||

| + | |- | ||

| + | | 3 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 5 | ||

| + | | 3 | ||

| + | |- | ||

| + | | 4 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 4 | ||

| + | | 4 | ||

| + | |- | ||

| + | | 5 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 3 | ||

| + | | 5 | ||

| + | |- | ||

| + | | 6 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 2 | ||

| + | | 6 | ||

| + | |- | ||

| + | | 7 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 7 | ||

| + | |- | ||

| + | | 8 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | | 0 | ||

| + | |- | ||

| + | | 9 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 7 | ||

| + | | 1 | ||

| + | |- | ||

| + | | 10 | ||

| + | | 1 | ||

| + | | 1 | ||

| + | | 0 | ||

| + | | 6 | ||

| + | | 2 | ||

| + | |} | ||

| + | |||

| + | |||

| + | [[Imagem:fig21_DIG222802.png|center|450px]] | ||

| + | <center> | ||

| + | Figura 8 - Diagrama de transição de estados do contador MOD-8. | ||

| + | </center> | ||

| + | |||

| + | ===Contador assíncrono ascendente-descendente=== | ||

| + | |||

| + | |||

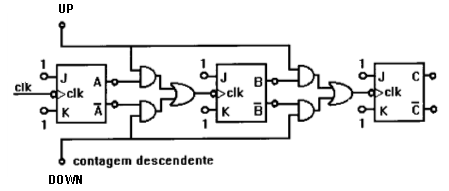

| + | O contador assíncrono ascendente-descendente, também chamado de reversível, é uma combinação dos contadores anteriormente vistos. Ele possui os FF conectados conforme mostra a Figura 9. Nesta configuração a lógica de portas permite que o contador tenha dois modos de operação distintos: | ||

| + | |||

| + | *Modo de contagem ascendente: UP = 1 e DOWN = 0. Os FF B e C são disparados pelas saídas não complementares do FF anterior (Q) | ||

| + | *Modo de contagem descendente: UP = 0 e DOWN = 1. Os FF B e C são disparados pelas saídas complementares do FF anterior (Q\) | ||

| + | |||

| + | |||

| + | [[Imagem:fig22_DIG222802.png|center|450px]] | ||

| + | <center> | ||

| + | Figura 9 - Contador assíncrono ascendente-descendente. | ||

| + | </center> | ||

| + | |||

| + | |||

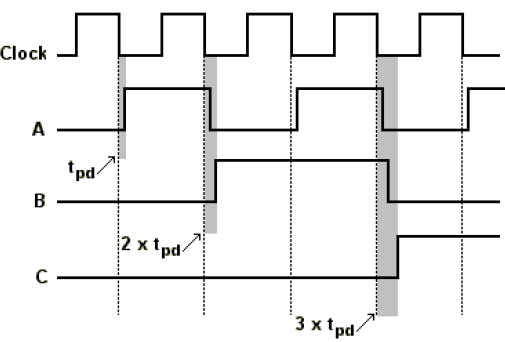

| + | ==Atrasos de propagação de contadores assíncronos== | ||

| + | |||

| + | Em um contador assíncrono cada FF é disparado pela saída de um FF anterior. Essa característica traz como desvantagem o acumulo dos tempos de atraso de propagação. Isso pode ser visto na Figura 10. Ao passar por um FF, o sinal de ''clock'' sofre um atraso de propagação <math>t_{pd}</math> e esse efeito é somado até o último FF, gerando um atraso total de <math>N.t_{pd}</math>, onde N é o número de FF. | ||

| + | |||

| + | |||

| + | [[Imagem:fig23_DIG222802.png|center|450px]] | ||

| + | <center> | ||

| + | Figura 10 - Contador assíncrono ascendente-descendente. | ||

| + | </center> | ||

| + | |||

| + | Para que um contador assíncrono funcione de modo confiável é necessário que o atraso total de propagação seja menor que o período de ''clock'' usado: <math>T_{clk} \ge N.t_{pd}</math>, ou ainda, em termos de frequência máxima, que <math>f_{max}=\frac{1}{N.t_{pd}}</math>. | ||

=Referências= | =Referências= | ||

| Linha 333: | Linha 471: | ||

! style="background:#4069e1;" | [[DIG222802_AULA02 | << ]] | ! style="background:#4069e1;" | [[DIG222802_AULA02 | << ]] | ||

! style="background:#789;" | [[DIG222802 | <> ]] | ! style="background:#789;" | [[DIG222802 | <> ]] | ||

| − | ! style="background:#4069e1;" | [[ | + | ! style="background:#4069e1;" | [[DIG222802_AULA04 | >> ]] |

| + | |} | ||

Edição atual tal como às 18h57min de 20 de abril de 2016

Contadores

Os contadores são circuitos que utilizam flip-flops e são aplicados, principalmente, em contagens, diversas, divisão de frequência, medição de frequência e tempo, divisão de formas de onda e conversão de analógico para digital. Estes circuitos sequenciais são divididos basicamente em duas categorias:

- Contadores assíncronos; e

- Contadores síncronos.

Basicamente a principal diferença entre eles é que o síncrono utiliza um sinal de clock comum a todos os flip-flops e o assíncrono possuí um sinal de clock que é dividido até o último flip-flops.

Contadores assíncronos

Estes contadores também são conhecidos como seriais ou contadores por pulsação (ripple counter). Tal nome advém do fato dos flip-flops (FF) do contador não serem disparados diretamente pelo sinal de clock. Cada FF é disparado pela saída do FF anterior. Esta característica torna estes contadores limitados em termos de velocidade, pois o tempo de ativação (tempo de resposta) é dado aproximadamente pela soma dos tempos de atraso de propagação de cada FF.

Contador assíncrono crescente

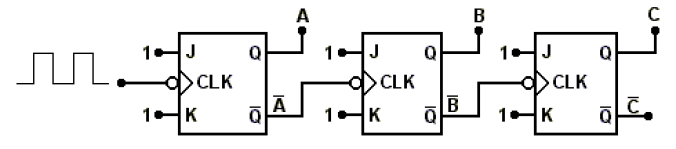

Um circuito típico de um contador assíncrono crescente construído com FF do tipo JK é mostrado na Figura 1. Os FF JK estão com ambas entradas J e K permanentemente em nível alto, estando configuradas portanto como FF tipo T. Cada FF é disparado pela saída do FF anterior. A Figura 2 mostra o diagrama de tempo para esse contador.

Figura 1 - Contador assíncrono crescente.

Figura 2 - Diagrama de tempo do contador assíncrono crescente.

| Clock | D | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 0 | 1 | 0 | 2 | 2 |

| 3 | 0 | 0 | 1 | 1 | 3 | 3 |

| 4 | 0 | 1 | 0 | 0 | 4 | 4 |

| 5 | 0 | 1 | 0 | 1 | 5 | 5 |

| 6 | 0 | 1 | 1 | 0 | 6 | 6 |

| 7 | 0 | 1 | 1 | 1 | 7 | 7 |

| 8 | 1 | 0 | 0 | 0 | 8 | 8 |

| 9 | 1 | 0 | 0 | 1 | 9 | 9 |

| 10 | 1 | 0 | 1 | 0 | 10 | 10 |

| 11 | 1 | 0 | 1 | 1 | 11 | 11 |

| 12 | 1 | 1 | 0 | 0 | 12 | 12 |

| 13 | 1 | 1 | 0 | 1 | 13 | 13 |

| 14 | 1 | 1 | 1 | 0 | 14 | 14 |

| 15 | 1 | 1 | 1 | 1 | 15 | 15 |

| 16 | 0 | 0 | 0 | 0 | 0 | 0 |

| 17 | 0 | 0 | 0 | 1 | 1 | 1 |

| 18 | 0 | 0 | 1 | 0 | 2 | 2 |

O contador tem como conteúdo (estado interno) a contagem do número de transições negativas do clock, de forma que quando ocorre uma transição o conteúdo é incrementado de uma unidade. O conteúdo do contador é dado pelo número binário DCBA, onde A é o bit LSB (bit menos significativo) e D é o bit MSB (bit mais significativo). O modulo (MOD) de um contador é o seu número de estados distintos, portanto, o módulo de um contador com N FF pode ser no máximo o número de possíveis saídas (). A Tabela mostra os estados de contagem de um contador assíncrono com 4 FF (4 bits). Podemos perceber que após 16 transições de clock o contador reinicia a contagem. Por isso, este contador é de MOD-16, ou seja, tem 16 estados distintos (0000b até 1111b). Nos contadores assíncronos, a frequência do clock é dividida por 2 em cada FF, ou seja: na saída A temos clock/2, e na saída D temos clock/16. Portanto, os contadores assíncronos são divisores de frequência e no último FF a frequência de clock é dividida pelo módulo do contador.

Contadores com módulo <

Para obter um contador com módulo menor do que é necessário adicionar um circuito decodificador para reiniciar a contagem antes de chegar ao valor máximo (ou mínimo). A Figura 3 mostra um contador MOD-6. Se não houvesse a porta NAND ligada nas entradas CLR dos FF o módulo do contador seria 8. A sequência de estados do contador MOD-6 é mostrada nas Figura 4 e Tabela 2. Note que na transição do 6º clock o estado do contador passa temporariamente pelo estado (110b), o qual faz com que a saída da porta NAND passe para o estado BAIXO, causando o CLR nos FF, e consequentemente levando o contador para o estado (000b).

Figura 3 - Contador assíncrono com módulo < .

Figura 4 - Diagrama de tempo do contador com módulo < .

| Clock | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 0 | 0 | 1 | 1 | 1 |

| 2 | 0 | 1 | 0 | 2 | 2 |

| 3 | 0 | 1 | 1 | 3 | 3 |

| 4 | 1 | 0 | 0 | 4 | 4 |

| 5 | 1 | 0 | 1 | 5 | 5 |

| 6* | 1 | 1 | 0 | 6 | 6 |

| 6 | 0 | 0 | 0 | 0 | 0 |

| 7 | 0 | 0 | 1 | 1 | 1 |

| 8 | 0 | 1 | 0 | 2 | 2 |

*Não atingível.

O diagrama de transição de estados do contador de 3 bits MOD-6 é mostrado na Figura 5. No diagrama de transição as linhas contínuas indicam a passagem pelos estados estáveis (000b 101b) e as linhas tracejadas indicam a passagem pelos estados temporários (110b). O estado (111b) embora possível não é atingível.

Figura 5 - Diagrama de transição de estados de um contador MOD-6.

Para a construção de um contador módulo X menor que o módulo máximo, o procedimento deve seguir as etapas:

- Determinar o menor número N de FF tal que .

- Exemplo: MOD-12 N = 16.

- Conectar a porta NAND nas entradas assíncronas de todos os FF. Se , não é necessário conectar nada a entrada;

- Conectar as saídas que estarão em ALTO na contagem X, na porta NAND.

- Exemplo: 12 = 1100b D = 1 e C = 1, conectar D e C a porta NAND.

Contadores de década

Os contadores de década (ou decádico) são contadores que possuem 10 estados distintos, não importando a sequência de contagem. Quando um contador decádico realiza a contagem em sequência binária crescente de 0000b a 1001b (0 a 9), ele é chamado de contador BCD.

Contador assíncrono decrescente

Os contadores que contam progressivamente a partir do zero são denominados contadores crescentes (ou ascendentes). Já os contadores que contam do valor máximo até zero são chamados decrescentes (ou descendentes). A Figura 6 mostra a configuração para um contador decrescente construído com FF do tipo JK. A configuração é semelhante à do contador crescente, com a única diferença de cada FF é disparado pela saída Q\ no lugar de Q.

Figura 6 - Contador assíncrono decrescente.

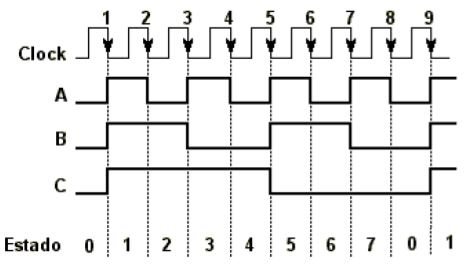

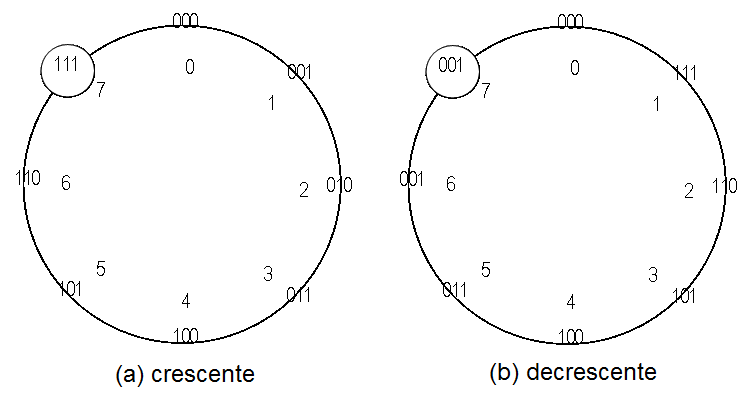

A Figura 7 mostra o diagrama de tempo das saídas do contador, enquanto que a Tabela 3 mostra a contagem das transições do clock e os estados correspondentes ao contador. O diagrama de estados do contador decrescente é mostrado na Figura 8 (b), enquanto que o diagrama do contador crescente é mostrado na Figura 8 (a). Note que nos dois diagramas o contador passa por todos os estados.

Figura 7 - Diagrama de tempo do contador assíncrono decrescente.

| Clock | C | B | A | Decimal | Estado |

|---|---|---|---|---|---|

| 0 | 0 | 0 | 0 | 0 | 0 |

| 1 | 1 | 1 | 1 | 7 | 1 |

| 2 | 1 | 1 | 0 | 6 | 2 |

| 3 | 1 | 0 | 1 | 5 | 3 |

| 4 | 1 | 0 | 0 | 4 | 4 |

| 5 | 0 | 1 | 1 | 3 | 5 |

| 6 | 0 | 1 | 0 | 2 | 6 |

| 7 | 0 | 0 | 1 | 1 | 7 |

| 8 | 0 | 0 | 0 | 0 | 0 |

| 9 | 1 | 1 | 1 | 7 | 1 |

| 10 | 1 | 1 | 0 | 6 | 2 |

Figura 8 - Diagrama de transição de estados do contador MOD-8.

Contador assíncrono ascendente-descendente

O contador assíncrono ascendente-descendente, também chamado de reversível, é uma combinação dos contadores anteriormente vistos. Ele possui os FF conectados conforme mostra a Figura 9. Nesta configuração a lógica de portas permite que o contador tenha dois modos de operação distintos:

- Modo de contagem ascendente: UP = 1 e DOWN = 0. Os FF B e C são disparados pelas saídas não complementares do FF anterior (Q)

- Modo de contagem descendente: UP = 0 e DOWN = 1. Os FF B e C são disparados pelas saídas complementares do FF anterior (Q\)

Figura 9 - Contador assíncrono ascendente-descendente.

Atrasos de propagação de contadores assíncronos

Em um contador assíncrono cada FF é disparado pela saída de um FF anterior. Essa característica traz como desvantagem o acumulo dos tempos de atraso de propagação. Isso pode ser visto na Figura 10. Ao passar por um FF, o sinal de clock sofre um atraso de propagação e esse efeito é somado até o último FF, gerando um atraso total de , onde N é o número de FF.

Figura 10 - Contador assíncrono ascendente-descendente.

Para que um contador assíncrono funcione de modo confiável é necessário que o atraso total de propagação seja menor que o período de clock usado: , ou ainda, em termos de frequência máxima, que .

Referências

[1] Apostila do CURSO DE ELETRÔNICA DIGITAL. CEFET/SC: São José, 2011.

| << | <> | >> |

|---|